## **TE0705 CPLD**

## **Overview**

Terbever wordenbergter 4: LCMX02-1200HC

# • 1.1 Feature Summary

- Power Management Revision and supported PCB Revision

Reserving angement revision

- BooP Mode Contremption

FPGA UART Distingl Description

I2C to GPIO

2.2.1 User Dip Switch

2.2.2 JTAG

• 2.2.2.1 PCB REV04 (Default)

## Firmware Revision and supported PCB Revision

2.2.4 Reset See Document Change HistoryBoot mode

• 2.2.5.1 PCB REV04 (Default) 2.2.5.2 PCB REV03 (Optional)

# Product Specification

2.2.8 NOSEQ

2.2.9 PGOOD

Port Description On-board LEDs

2.3.1 I2C to GPIO registers

| Name Appt. A: Cl<br>VHD Name $^{\circ}$ 3.1 | Revision Changes                                                                                 | Pin   | Pull up/ down | Bank Power | Description                                                        |

|---------------------------------------------|--------------------------------------------------------------------------------------------------|-------|---------------|------------|--------------------------------------------------------------------|

| ACBU <b>\$</b> 4Appx. B: Le                 | Document Change I<br>gal Notices<br>Data Privacy<br>Document Warranty<br>Limitation of Liability | 96    | UP            | 3.3V       | FTDI / It can be<br>read via i2c to<br>GPIO. (<br>GPIO_input(22) ) |

| ACBUS5 ° 4.5<br>° 4.6                       | Copyright Notice<br>Technology License<br>Environmental Prote<br>REACH, RoHS and<br>Intents      | ction | UP            | 3.3V       | FTDI / It can be<br>read via i2c to<br>GPIO. (<br>GPIO_input(23) ) |

| ADBUS4                                      | out                                                                                              | 98    | NONE          | 3.3V       | FTDI / M_TCK is connected to ADBUS4.                               |

| ADBUS7                                      | out                                                                                              | 97    | UP            | 3.3V       | FTDI / currently_no<br>t_used                                      |

| BDBUS0                                      | inout                                                                                            | 87    | NONE          | 3.3V       | FTDI / Module<br>UART0-RX <<<br>FTDI                               |

| BDBUS1                                      | inout                                                                                            | 86    | NONE          | 3.3V       | FTDI /Module<br>UART0-TX >><br>FTDI                                |

| C_TCK                                       | out                                                                                              | 81    | DOWN          | 3.3V       | TCK JTAG port<br>pin connected to<br>Module                        |

| C_TDI                                       | out                                                                                              | 84    | DOWN          | 3.3V       | TDI JTAG port<br>pin connected to<br>Module                        |

| C_TDO    | in    | 83 | DOWN | 3.3V | TDO JTAG port<br>pin connected to<br>Module                                                                                                                                                        |

|----------|-------|----|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_TMS    | out   | 85 | UP   | 3.3V | TMS JTAG port<br>pin connected to<br>Module                                                                                                                                                        |

| CM0      | in    | 67 | UP   | 3.3V | DIP Switch S3-M1<br>/ Used to select<br>FMC_VADJ voltage                                                                                                                                           |

| CM1      | in    | 66 | UP   | 3.3V | DIP Switch S3-M2<br>/ Used to select<br>FMC_VADJ<br>voltage                                                                                                                                        |

| EN_FMC   | out   | 35 | NONE | 3.3V | Power SoC<br>(EN5335QI) power<br>on signal (VADJ<br>enable)                                                                                                                                        |

| EN1      | out   | 53 | UP   | 3.3V | Power Enable Pin for CPLD of module                                                                                                                                                                |

| JTAGEN   |       | 82 | UP   | 3.3V | Enable JTAG<br>access to carrier<br>CPLD for<br>Firmware update (<br>Zero: JTAG routed<br>to module, One:<br>CPLD access ) Set<br>DIP Switch S3-<br>JTAGEN (S3-<br>C) to ON, for<br>module access. |

| JTAGMODE | out   | 58 | NONE | 3.3V | Enable JTAG<br>access to module<br>CPLD for firmware<br>programming. If<br>JTAGMODE = '0'<br>JTAG port is<br>routed to FPGA of<br>module otherwise<br>JTAG port is<br>routed to CPLD of<br>module. |

| M_TCK    | in    | 91 | UP   | 3.3V | TCK JTAG port<br>pin connected<br>to FTDI chip                                                                                                                                                     |

| M_TDI    | in    | 94 | UP   | 3.3V | TDI JTAG port<br>pin connected<br>to FTDI chip                                                                                                                                                     |

| M_TDO    | out   | 95 | UP   | 3.3V | TDO JTAG port<br>pin connected<br>to FTDI chip                                                                                                                                                     |

| M_TMS    | in    | 90 | UP   | 3.3V | TMS JTAG port<br>pin connected<br>to FTDI chip                                                                                                                                                     |

| MIO10    | inout | 32 | UP   | 3.3V | MIO / I2C SCL pin<br>of CPLD of TE0705                                                                                                                                                             |

| MIO11    | inout | 31 | UP   | 3.3V | MIO / I2C SDA pin<br>of CPLD of TE0705                                                                                                                                                             |

| MIO12    | inout | 39 | NONE | 3.3V | MIO                                                                                                                                                                                                |

| MIO13    | inout | 34 | NONE | 3.3V | MIO                                                                                                                                                                                                |

| MIO14      | inout | 40 | NONE | 3.3V | MIO / Module<br>UART0-RX <<<br>BDBUS0                                                                                                                                                                 |

|------------|-------|----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIO15      | inout | 30 | NONE | 3.3V | MIO /<br>Module UART0-<br>TX >> BDBUS1                                                                                                                                                                |

| MODE       | out   | 28 | DOWN | 3.3V | Boot mode select<br>pin for Zynq<br>Devices                                                                                                                                                           |

| NOSEQ      | inout | 29 | UP   | 3.3V | For TE0715<br>module is<br>connected to<br>M_TMS JTAG pin<br>for programming<br>the CPLD of<br>TE0715. For other<br>modules this pin is<br>used as GPIO.                                              |

| PGOOD      | inout | 27 | UP   | 3.3V | For TE0715<br>module is<br>connected to M-<br>TDO JTAG pin for<br>programming the<br>CPLD of TE0715.<br>For other modules<br>this pin is used as<br>either GPIO pin or<br>boot mode<br>selection pin. |

| PHY_LED1   | out   | 45 | NONE | 3.3V | RJ45 connector<br>right LED Green<br>LED anode and<br>yellow LED<br>cathode / State of<br>this pin indicates<br>PGOOD and<br>NOSEQ signal<br>state.                                                   |

| PHY_LED1_A | out   | 49 | NONE | 3.3V | RJ45 connector<br>right LED Green<br>LED cathode and<br>yellow LED anode<br>/ State of this pin<br>indicates PGOD<br>and NOSEQ signal<br>state.                                                       |

| PHY_LED2   | out   | 47 | NONE | 3.3V | RJ45 connector<br>left LED Green<br>LED cathode and<br>yellow LED anode<br>/ State of this pin<br>indicates EN_FMC<br>( Power Ok of<br>EN5335QI<br>PowerSoC)                                          |

| PHY_LED2_A | out   | 48 | NONE | 3.3V | RJ45 connector<br>left LED Green<br>LED anode and<br>yellow LED<br>cathode / State of<br>this pin indicates<br>EN_FMC ( Power<br>Ok of EN5335QI<br>PowerSoC)                                          |

| POK_FMC    | in    | 36 | UP   | 3.3V | FMC VADJ Power<br>Good                                                                                                                                                                                |

| RESIN     | out | 54 | UP   | 3.3V | Module reset that<br>connected to S2<br>push button                                                                                                  |

|-----------|-----|----|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1        | in  | 75 | UP   | 3.3V | User button                                                                                                                                          |

| S2        | in  | 74 | UP   | 3.3V | User button /<br>Global Reset push<br>button                                                                                                         |

| SD_DETECT | in  | 42 | UP   | 3.3V | SD card detection /<br>Used for FPGA<br>Boot Mode<br>selection.<br>Connected to<br>MODE pin ,if<br>USR0 = OFF for<br>PCB REV04.                      |

| SD_WP     | in  | 43 | UP   | 3.3V | SD write protect                                                                                                                                     |

| ULED1     | out | 78 | NONE | 3.3V | LED D6 /<br>Connected to<br>MODE0 signal . If<br>MODE0='1'<br>FMC_VADJ = 1.8V<br>Connected to<br>GPIO_output(0) , if<br>S1 push button is<br>pushed. |

| ULED2     | out | 77 | NONE | 3.3V | LED D7 /<br>Connected to<br>MODE1 signal. If<br>MODE1=1'<br>FMC_VADJ = 2.5V<br>Connected to<br>GPIO_output(1), if<br>S1 push button is<br>pushed.    |

| ULED3     | out | 76 | NONE | 3.3V | LED D8 /<br>Connected to<br>MODE2 signal. If<br>MODE2='1'<br>FMC_VADJ = 3.3V<br>Connected to<br>GPIO_output(2) , if<br>S1 push button is<br>pushed.  |

| ULED4     | out | 65 | NONE | 3.3V | LED D9 /<br>Connected to<br>MODE3 signal. If<br>MODE3='1'<br>FMC_VADJ = 1.8V<br>Connected to<br>GPIO_output(3) , if<br>S1 push button is<br>pushed.  |

| ULED5     | out | 71 | NONE | 3.3V | LED D4 /<br>Connected to<br>RESET push<br>button (S2)<br>Connected to<br>GPIO_output(4), if<br>S1 push button is<br>pushed.                          |

| ULED6             | out | 70 | NONE | 3.3V | LED D15 /<br>Connected to<br>SD_DETECT. f<br>LED is ON><br>MODE = '1' (QSPI<br>boot mode) else<br>MODE = '0' (SD<br>card boot mode)<br>Connected to<br>GPIO_output(5) , if<br>S1 push button is<br>pushed. |

|-------------------|-----|----|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ULED7             | out | 69 | NONE | 3.3V | LED D14 /<br>Connected to<br>UART0-TX<br>Connected to<br>GPIO_output(6), if<br>S1 push button is<br>pushed.                                                                                                |

| ULED8             | out | 68 | NONE | 3.3V | LED D5 /<br>Connected to<br>UART0-RX<br>Connected to<br>GPIO_output(7), if<br>S1 push button is<br>pushed.                                                                                                 |

| USB_OC            | in  | 99 | UP   | 3.3V | USB Over Current                                                                                                                                                                                           |

| USR0 <sup>*</sup> | in  | 64 | NONE | 3.3V | DIP Switch S4-1 /<br>Used to determine<br>if TE0715 CPLD<br>access is<br>activated. If USR0<br>= ON Access to<br>TE0715 CPLD , If<br>USR0 = OFF No<br>access to TE0715<br>CPLD                             |

| USR1 <sup>*</sup> | in  | 61 | NONE | 3.3V | DIP Switch S4-2 /<br>USR1 can set or<br>reset NOSEQ, if<br>USR0 = OFF                                                                                                                                      |

| USR2 <sup>*</sup> | in  | 60 | NONE | 3.3V | DIP Switch S4-3 /<br>USR2 can set set<br>or reset PGOOD, if<br>USR0 = OFF                                                                                                                                  |

| USR3 <sup>*</sup> | in  | 59 | NONE | 3.3V | DIP Switch S4-4 /<br>Connected to<br>JTAGMODE signal<br>for accessing to<br>CPLD of module.<br>USR3 = ON No<br>access to CPLD of<br>module, USR3 =<br>OFF Access to<br>CPLD of module                      |

| VID0              | out | 37 | NONE | 3.3V | VADJ Voltage<br>selection of power<br>SoC (EN5335QI)                                                                                                                                                       |

| VID1              | out | 38 | NONE | 3.3V | VADJ Voltage<br>selection of power<br>SoC (EN5335QI)                                                                                                                                                       |

| VID2              | out | 41 | NONE | 3.3V | VADJ Voltage<br>selection of power<br>SoC (EN5335QI)                                                                                                                                                       |

| X6 | in | 19 | NONE | 3.3V | Connection pin<br>between CPLD of<br>carrier board and<br>FPGA on the<br>module via B2B<br>connector. It can<br>be read via i2c to<br>GPIO.( GPIO_input<br>(31) ) |

|----|----|----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| YO | in | 15 | DOWN | 3.3V | Connection pin<br>between CPLD of<br>carrier board and<br>FPGA on the<br>module via B2B<br>connector. It can<br>be read via i2c to<br>GPIO.( GPIO_input<br>(24) ) |

| Y1 | in | 14 | DOWN | 3.3V | Connection pin<br>between CPLD of<br>carrier board and<br>FPGA on the<br>module via B2B<br>connector. It can<br>be read via i2c to<br>GPIO.( GPIO_input<br>(25) ) |

| Y2 | in | 13 | DOWN | 3.3V | Connection pin<br>between CPLD of<br>carrier board and<br>FPGA on the<br>module via B2B<br>connector. It can<br>be read via i2c to<br>GPIO.( GPIO_input<br>(26) ) |

| Y3 | in | 10 | DOWN | 3.3V | Connection pin<br>between CPLD of<br>carrier board and<br>FPGA on the<br>module via B2B<br>connector. It can<br>be read via i2c to<br>GPIO.( GPIO_input<br>(27) ) |

| Y4 | in | 9  | NONE | 3.3V | Connection pin<br>between CPLD of<br>carrier board and<br>FPGA on the<br>module via B2B<br>connector. It can<br>be read via i2c to<br>GPIO.( GPIO_input<br>(28) ) |

| Y5 | in | 8  | NONE | 3.3V | Connection pin<br>between CPLD of<br>carrier board and<br>FPGA on the<br>module via B2B<br>connector. It can<br>be read via i2c to<br>GPIO.( GPIO_input<br>(29) ) |

| Y6 | in | 7 | NONE | 3.3V | Connection pin<br>between CPLD of<br>carrier board and<br>FPGA on the<br>module via B2B<br>connector. It can<br>be read via i2c to<br>GPIO.(GPIO_input<br>(30)) |

|----|----|---|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----|----|---|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

\*Note: USR dip switch (S4-Dip Switch) does not exist in PCB revision 3 or older.

## **Functional Description**

### **User Dip Switch**

User has 8 dip switches and two push buttons in total on the board. In the following tables you can find more information about it.

| DIP Switch S3 |       |          |       |                                                                            |  |  |

|---------------|-------|----------|-------|----------------------------------------------------------------------------|--|--|

| S3-1          | S3-2  | S3-3     | S3-4  | Description                                                                |  |  |

| СМ1**         | СМ0** | JTAGEN** | MIO0* | JTAGEN set carrier<br>board CPLD into the<br>chain for firmware<br>update. |  |  |

\*Note: MIO0 is not connected to CPLD chip.

\*\*Pin names in the schematic of board. Names on the board (labels) : CM1 M2 , CM0 M1, JTAGEN ENJTAG

| DIP Switch S4 <sup>*</sup> |      |      |      |             |  |  |

|----------------------------|------|------|------|-------------|--|--|

| S4-1                       | S4-2 | S4-3 | S4-4 | Description |  |  |

| USR0                       | USR1 | USR2 | USR3 |             |  |  |

\*Note: This dip switch exists only for PCB revision 4 or later.

| USRO | Description                                  |

|------|----------------------------------------------|

| OFF  | No access to TE0715 CPLD                     |

| ON   | Access to TE0715 CPLD                        |

| USR1 | Description                                  |

| OFF  | NOSEQ = '0' if USR0 = OFF else NOSEQ = M_TMS |

| ON   | NOSEQ = '1' if USR0 = OFF else NOSEQ = M_TMS |

| USR2 | Description                                  |

| OFF  | PGOOD = '0' if USR0 = OFF else PGOOD = 'Z'   |

| ON   | PGOOD = '1' if USR0 = OFF else PGOOD = 'Z'   |

| USR3 | Description                               |

|------|-------------------------------------------|

| OFF  | JTAGMODE = '0' JTAG routed to module FPGA |

| ON   | JTAGMODE = '1' Access to CPLD of module   |

### **JTAG**

In normal mode JTAG is routed directly to the module. JTAGEN set carrier board CPLD into the chain for firmware update. Set S3-3 (ENJTAG) to OFF to get access to carrier CPLD. JTAGMODE set module CPLD into the chain for firmware update. In normal mode JTAG is routed directly to FPGA. To access CPLD of TE0715 JTAG port must be routed to special pins same as NOSEQ pin. Therefore in PCB REV04 or later USR0 is used to access CPLD of TE0715 module. For PCB REV03 CM0(S3-2) and CM1(S3-1) dip switches will be used for this purpose. In this case user must be careful because these dip switches are used to select FMC\_VADJ output voltage too.

### () Warning

For some 4x5 modules if FMC\_VADJ voltage is set incorrectly, the FPGA can be damaged !

More information about JTAG pins can be found in the following table:

| Pin   | Connected to | Condition for | * P <b>CB</b> nREW044 for<br>*        | l <b>RBB</b> SCEØØØN        | Connected to | Condition for | • P <b>CB</b> nREEW044 foon<br>*       | l <b>RIBB</b> SCEIØØØN                                                                           |

|-------|--------------|---------------|---------------------------------------|-----------------------------|--------------|---------------|----------------------------------------|--------------------------------------------------------------------------------------------------|

| M_TMS | NOSEQ        | USR0 = ON     | CM1(S3-1)<br>=ON and CM0<br>(S3-2)=ON | Access to<br>TE0715<br>CPLD | C_TMS        | USR0 = OFF    | CM1(S3-1)<br>=OFF or CM0<br>(S3-2)=OFF | No access to<br>TE0715<br>CPLD. In this<br>case NOSEQ<br>can be used<br>as user IO.              |

| М_ТСК | MODE         | USR0 = ON     | CM1(S3-1)<br>=ON and CM0<br>(S3-2)=ON | Access to<br>TE0715<br>CPLD | с_тск        | USR0 = OFF    | CM1(S3-1)<br>=OFF or CM0<br>(S3-2)=OFF | No access to<br>TE0715<br>CPLD. In this<br>case MODE<br>will be used<br>as SD card<br>detection. |

| M_TDI | EN1          | USR0 = ON     | CM1(S3-1)<br>=ON and CM0<br>(S3-2)=ON | Access to<br>TE0715<br>CPLD | C_TDI        | USR0 = OFF    | CM1(S3-1)<br>=OFF or CM0<br>(S3-2)=OFF | No access to<br>TE0715<br>CPLD. In this<br>case EN1 is<br>'1'.                                   |

| C_TDO | PGOOD        | USR0 = ON     | CM1(S3-1)<br>=ON and CM0<br>(S3-2)=ON | Access to<br>TE0715<br>CPLD | M_TDO        | USR0 = OFF    | CM1(S3-1)<br>=OFF or CM0<br>(S3-2)=OFF | No access to<br>TE0715<br>CPLD. In this<br>case PGOOD<br>can be used<br>as user IO.              |

\*Note: This case is valid if jed file for accessing to TE0715 CPLD is programmed on the TE0705 carrier board CPLD.

| Pin      | CPLD Pin | Connected to             | Description                                                                                  |

|----------|----------|--------------------------|----------------------------------------------------------------------------------------------|

| JTAGEN   | 82       | S3-3 Dip Switch (ENJTAG) | To access CPLD of carrier<br>board, JTAGEN must be set<br>to '1'. ( ENJTAG (S3-3) =<br>OFF ) |

| JTAGMODE | 58       | B2B JB1-90               | To access CPLD of module this pin must be set to high.                                       |

PCB REV04 (Default)

| Status                       | S4-1(USR0) | S4-4(USR3) | S3-3(ENJTAG) | Description |

|------------------------------|------------|------------|--------------|-------------|

| Access to carrier board CPLD |            |            | OFF          |             |

| Access to FPGA of module     | OFF        | OFF        | ON           |             |

| Access to CPLD of module     | OFF        | ON         | ON           |             |

| Access to the<br>TE0715 CPLD | ON         | ON         | ON           |             |

| JTAGMODE | Condition  | Description              |

|----------|------------|--------------------------|

| 0        | USR3 = OFF | To access FPGA of module |

| 1        | USR3 = ON  | To access CPLD of module |

### PCB REV03 (Optional)

| Status                                      | CM1(S3-1) | CM0(S3-2) | S3-3(ENJTAG) | FMC_VADJ | Description                                                                                                                |

|---------------------------------------------|-----------|-----------|--------------|----------|----------------------------------------------------------------------------------------------------------------------------|

| Access to<br>carrier board<br>CPLD          |           |           | OFF          |          |                                                                                                                            |

| Access to<br>FPGA of<br>module              | OFF       | OFF       | ON           | 1.8V     |                                                                                                                            |

| Access to<br>FPGA of<br>module              | OFF       | ON        | ON           | 3.3V     |                                                                                                                            |

| Access to<br>FPGA of<br>module              | ON        | OFF       | ON           | 2.5V     |                                                                                                                            |

| Access to<br>CPLD of<br>module <sup>*</sup> | ON        | ON        | ON           | 1.8V     | Attention: It is<br>exists two<br>separate jed file to<br>access the CPLD<br>on the TE0715<br>module and other<br>modules. |

\*For accessing to CPLD of TE0715, special jed file in optional folder must be programmed on the CPLD of carrier board TE0705. If jed file for accessing to CPLD of TE0715 (Access to TE0715 CPLD) is programmed on the CPLD of carrier board, CPLD of other modules can not be programmed more. In this case, if user need to update firmware CPLD of the module, user should program other jed file (No Access to TE0715 CPLD) on the carrier board CPLD.

| JTAGMODE | Condition                           | Description              |

|----------|-------------------------------------|--------------------------|

| 0        | CM1(S3-1)= OFF or CM0(S3-2)=<br>OFF | To access FPGA of module |

| 1        | CM1(S3-1)= ON and CM0(S3-2)=<br>ON  | To access CPLD of module |

### **Power**

To adjust output voltage of EN5335QI power SoC (FMC\_VADJ) CM1(S3-1)and CM0(S3-2) are used. EN\_FMC pin is for activating this power SoC. EN\_FMC signal will be set to '1' to enable the power SoC after power on. VID0, VID1 and VID2 are connected to EN5335QI PowerSoC chip to select output voltage.

| EN5335QI Power SoC Voltage Select Lines |      |      |          |                |  |

|-----------------------------------------|------|------|----------|----------------|--|

| VID2                                    | VID1 | VID0 | Vout     | Description    |  |

| 0                                       | 0    | 0    | 3.3V     |                |  |

| 0                                       | 0    | 1    | 2.5V     |                |  |

| 0                                       | 1    | 0    | 1.8V     |                |  |

| 0                                       | 1    | 1    | 1.5V     | Not selectable |  |

| 1                                       | 0    | 0    | 1.25V    | Not selectable |  |

| 1                                       | 0    | 1    | 1.2V     | Not selectable |  |

| 1                                       | 1    | 0    | 0.8V     | Not selectable |  |

| 1                                       | 1    | 1    | Reserved |                |  |

| EN5335QI Power SoC<br>output voltage | CM1(S3-1) | CM0(S3-2) | Description                                                         |

|--------------------------------------|-----------|-----------|---------------------------------------------------------------------|

| 1.8V                                 | OFF       | OFF       | Access to FPGA of module<br>for PCB REV03                           |

| 3.3V                                 | OFF       | ON        | Access to FPGA of module<br>for PCB REV03                           |

| 2.5V                                 | ON        | OFF       | Access to FPGA of module<br>for PCB REV03                           |

| 1.8V                                 | ON        | ON        | Access to TE0715 CPLD or<br>CPLD of other modules for<br>PCB REV03* |

\*There are for PCB REV03 two jed files in optional folder. One of them is for accessing to TE0715 CPLD and other jed file is for accessing to other 4x5 modules except TE0715. For PCB REV03 both CPLD of TE0715 and other modules except TE0715 can not be accessed via one jed file for CPLD of carrier board.

### Reset

RESIN pin (active low) of module can be set by S2 button.

| Pin   | CPLD Pin | Connected to                | Description |

|-------|----------|-----------------------------|-------------|

| RESIN | 54       | S2 push button / B2B JB2-17 | Active-low  |

### **Boot mode**

When SD card is plugged, SD\_DETECT signal will be set to '0'. If CM0(S3-2) and CM1(S3-1) for PCB REV03 and USR0 for PCB REV04 are not set for accessing to CPLD of TE0715 module, SD\_DETECT will be connected to MODE pin. MODE pin is responsible to set boot mode. If MODE pin is set to high, QSPI boot mode is selected else SD card boot mode is chosen.

| Pin | CPLD Pin | In hardware<br>connected to | Connected to<br>(Firmware of<br>PCB REV04) | Connected to<br>(Firmware of<br>PCB REV03) | Description |

|-----|----------|-----------------------------|--------------------------------------------|--------------------------------------------|-------------|

|-----|----------|-----------------------------|--------------------------------------------|--------------------------------------------|-------------|

| SD_DETECT | 42 | SD card detection pin | MODE pin<br>if USR0 = OFF | MODE pin if CM1<br>(S3-1)= OFF or<br>CM0(S3-2)= OFF |  |

|-----------|----|-----------------------|---------------------------|-----------------------------------------------------|--|

|-----------|----|-----------------------|---------------------------|-----------------------------------------------------|--|

### PCB REV04 (Default)

| Boot Mode*        | S4-3 (USR2) | SD Card | Description              |

|-------------------|-------------|---------|--------------------------|

| JTAG Mode         | OFF         | Plugged | PGOOD = '0' , MODE = '0' |

| eMMC Mode         | OFF         | Removed | PGOOD = '0' , MODE = '1' |

| SD Card Boot Mode | ON          | Plugged | PGOOD = '1' , MODE = '0' |

| QSPI Boot Mode    | ON          | Removed | PGOOD = '1' , MODE = '1' |

\*It is valid only for SoC. Note that after any change in dip switches carrier board must be reset, to change boot mode correctly.

### PCB REV03 (Optional)

The following boot mode table is not valid while CM1 = ON and CM0 = ON and jed file for accessing to TE0715 CPLD is programmed on the CPLD of carrier board for all 4x5 modules.

| Boot Mode*           | vir_usr2** | SD Card | Related<br>Command in<br>linux <sup>***</sup> | Related<br>Command in<br>FSBL <sup>***</sup> | Description                 |

|----------------------|------------|---------|-----------------------------------------------|----------------------------------------------|-----------------------------|

| JTAG Mode            | 1          | Plugged | i2cset -y 0<br>0x30 0x02 0x01                 | iic_write<br>(0x30,0x02,<br>0x01)            | PGOOD = '0' ,<br>MODE = '0' |

| eMMC Mode            | 1          | Removed | i2cset -y 0<br>0x30 0x02 0x01                 | iic_write<br>(0x30,0x02,<br>0x01)            | PGOOD = '0' ,<br>MODE = '1' |

| SD Card Boot<br>Mode | 0          | Plugged | i2cset -y 0<br>0x30 0x02 0x00                 | iic_write<br>(0x30,0x02,<br>0x00)            | PGOOD = '1' ,<br>MODE = '0' |

| QSPI Boot<br>Mode    | 0          | Removed | i2cset -y 0<br>0x30 0x02 0x00                 | iic_write<br>(0x30,0x02,<br>0x00)            | PGOOD = '1' ,<br>MODE = '1' |

\*It is valid only for SoC. Note that after any change in vir\_usr2 oder SD Card detection switch carrier board must be reset, to change boot mode correctly.

\*\*vir\_usr2 can be changed only via I2C to GPIO in linux console or in FSBL code. Its default value is '0'. If no I2C to GPIO is designed in Vivado and Linux, vir\_usr2 can not be changed. Because of its default value after power on ('0') user can choose only SD card boot mode and QSPI boot mode by plugging and removing the SD card respectively.

\*\*\*After setting vir\_usr2 via I2C to GPIO it is necessary to reset the board manually to change boot mode.

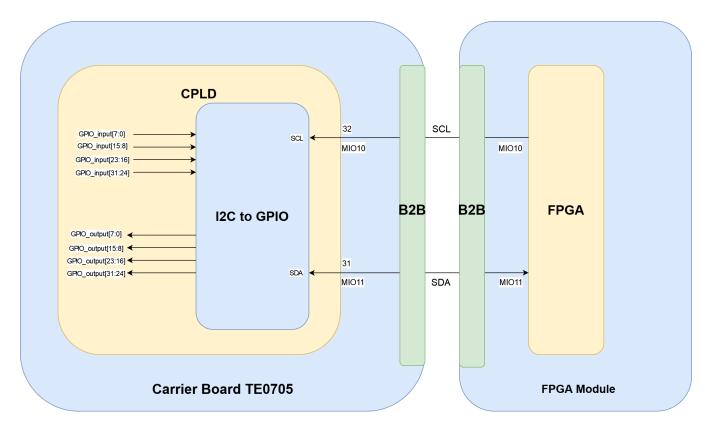

### **I2C to GPIO**

I2C to GPIO is a subsystem in firmware of CPLD that provides an i2c interface that writes received data to GPIO\_output 8 bit registers or reads 8 bit GPIO\_input registers and send read data to i2c bus.

I2C bus is connected to MIO10 (SCL signal) and MIO11 (SDA signal). MIO10 to MIO15 are direct connection between CPLD of TE0705 and FPGA on the module through B2B connector. If in FPGA design exists no i2c interface for MIO10 and MIO11, this block will be unused. More information about MIO10 to MIO15 are shown in the following table for whole Trenz Electronic 4x5 modules and TE0705 carrier board:

| B2B Pin          | B2B JB1-96                      | B2B JB1-94                      | B2B JB1-<br>100                 | B2B JB1-98                      | B2B JB1-91                      | B2B JB1-86                      |                                                                                                          |

|------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------|

| Carrier<br>board | Label /<br>Firmware<br>function | Description                                                                                              |

| TE0705           | MIO10 / I2C-<br>SCL             | MIO11 / I2C-<br>SDA             | MIO12 / GPIO                    | MIO13 / GPIO                    | MIO14 /<br>UART0-RX             | MIO15 /<br>USRT0-TX             | MIO10 and<br>MIO11 are<br>used in CPLD<br>firmware as I2C<br>SCL and<br>SDA respective<br>ly.            |

| B2B Pin          | B2B JM1-<br>95                  | B2B JM1-<br>93                  | B2B JM1-<br>99                  | B2B JM1-<br>97                  | B2B JM1-<br>92                  | B2B JM1-<br>85                  |                                                                                                          |

| Module           | Label /<br>Chip pin             | Description                                                                                              |

| TEM0007          | I2C_CON_SCL<br>/ A3             | I2C_CON_SDA<br>/ E3             | UART_CON_TX<br>/C2              | USRT_CON_R<br>X / D3            | UART_RX / H2                    | UART_TX / H5                    | MIO10 and<br>MIO11 are<br>already set in<br>test_design of<br>TEM0007 as<br>SCL and SDA<br>respectively. |

| TE0710 | B14_IO2 / R10      | B14_IO6 / L18      | B14_IO7 / T11      | B14_IO3 / M18      | B16_IO4 / A8       | B16_IO0 / B8       | By using an<br>external IIC IP<br>core B14_IO2<br>and B14_IO6<br>can be used as<br>I2C SCL and<br>SDA<br>respectively.   |

|--------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------|

| TE0711 | B14_IO2 / M13      | B14_IO6 / L18      | B14_IO7 / R16      | B14_IO3 / M18      | B14_IO4 / N17      | B14_IO0 / R10      | By using an<br>external IIC IP<br>core B14_IO2<br>and B14_IO6<br>can be used as<br>I2C SCL and<br>SDA<br>respectively.   |

| TE0712 | B14_L4_P / T21     | B14_L9_N / Y22     | B14_L24_N /<br>R17 | B14_L4_N /<br>U21  | B14_L24_P /<br>P16 | B14_L18_N /<br>U18 | By using an<br>external IIC IP<br>core B14_L4_P<br>and B14_L9_N<br>can be used as<br>I2C SCL and<br>SDA<br>respectively. |

| TE0713 | B14_L4_P / T21     | B14_L9_N / Y22     | B14_L24_N /<br>R19 | B14_L4_N /<br>U21  | B14_L24_P /<br>P19 | B14_L18_N /<br>U18 | By using an<br>external IIC IP<br>core B14_L4_P<br>and B14_L9_N<br>can be used as<br>I2C SCL and<br>SDA<br>respectively. |

| TE0741 | MIO10 /<br>B14_L22 | MIO11 /<br>B14_K21 | MIO12 /<br>B14_H23 | MIO13 /<br>B14_K22 | MIO14 /<br>B14_J21 | MIO15 /<br>B14_G24 | By using an<br>external IIC IP<br>core B14_L22<br>and B14_K21<br>can be used as<br>I2C SCL and<br>SDA<br>respectively.   |

| TE0841 | B65_SCL / Y19      | B65_SDA /<br>AA19  | B65_L3_N /<br>AF23 | B65_L3_P /<br>AF22 | B65_L2_N /<br>AH24 | B65_L4_N /<br>AG24 | By using an<br>external IIC IP<br>core B65_SCL<br>and<br>B65_SDA can<br>be used as I2C<br>SCL and SDA<br>respectively.   |

| TE0715 | MIO10 / G16        | MIO11 / B19        | MIO12 / C18        | MIO13 / A17        | MIO14 / B17        | MIO15 / E17        | MIO10 and<br>MIO11 can be<br>set as SCL and<br>SDA for I2C0<br>of TE0715<br>respectively.                                |

| TE0720 | MIO10 / G7         | MIO11 / B4         | MIO12 / C5         | MIO13 / A6         | MIO14 / B6         | MIO15 / E6         | MIO10 and<br>MIO11 are<br>already set as<br>as SCL and<br>SDA for I2C0 in<br>test_design of<br>TE0720<br>respectively.   |

| TE0820 | MIC26 / L15 | MIO27 / J15 | MIO28 / K15 | MIO29 / G16 | MIC30 / F16 | MIO31 / H16 | MIO26 and<br>MIO27 can be<br>set only for<br>I2C0 of FPGA<br>and this bus is<br>already used<br>for another<br>components<br>same as<br>EEPROM and<br>PLL chip. If<br>MIO10 and<br>MIO11 are<br>used as I2C<br>bus for data<br>communication<br>with CPLD,<br>then there are<br>no access to<br>PLL and<br>EEPROM chip. |

|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TE0821 | MIO26 / L15 | MIO27 / J15 | MIO28 / K15 | MIO29 / G16 | MIO30 / F16 | MIO31 / H16 | MIO26 and<br>MIO27 can be<br>set only for<br>I2C0 of FPGA<br>and this bus is<br>already used<br>for another<br>components<br>same as<br>EEPROM and<br>PLL chip. If<br>MIO10 and<br>MIO11 are<br>used as I2C<br>bus for data<br>communication<br>with CPLD,<br>then there are<br>no access to<br>PLL and<br>EEPROM chip. |

| TE0823 | MIO26 / L15 | MIO27 / J15 | MIO28 / K15 | MIO29 / G16 | MIO30 / F16 | MIO31 / H16 | MIO26 and<br>MIO27 can be<br>set only for<br>I2C0 of FPGA<br>and this bus is<br>already used<br>for another<br>components<br>same as<br>EEPROM and<br>PLL chip. If<br>MIO10 and<br>MIO11 are<br>used as I2C<br>bus for data<br>communication<br>with CPLD,<br>then there are<br>no access to<br>PLL and<br>EEPROM chip. |

There are more additional connections between CPLD and FPGA on the module , that are listed in the following table:

| CPLD Pin | Carrier board B2B<br>Pin | Module B2B Pin | In firmware used as                                      | Description                                             |

|----------|--------------------------|----------------|----------------------------------------------------------|---------------------------------------------------------|

| X6       | B2B JB1-84               | B2B JM1-83     | No specific function. It can only be read by GPIO_input. | It can be read via i2c to<br>GPIO. (GPIO_input<br>(31)) |

| YO       | B2B JB2-76               | B2B JM2-75     | No specific function. It can only be read by GPIO_input. | It can be read via i2c to<br>GPIO. (GPIO_input<br>(24)) |

| Y1 | B2B JB2-78 | B2B JM2-77 | No specific function. It can only be read by GPIO_input. | It can be read via i2c to<br>GPIO. (GPIO_input<br>(25)) |

|----|------------|------------|----------------------------------------------------------|---------------------------------------------------------|

| Y2 | B2B JB2-82 | B2B JM2-81 | No specific function. It can only be read by GPIO_input. | It can be read via i2c to<br>GPIO. (GPIO_input<br>(26)) |

| Y3 | B2B JB2-84 | B2B JM2-83 | No specific function. It can only be read by GPIO_input. | It can be read via i2c to<br>GPIO. (GPIO_input<br>(27)) |

| Y4 | B2B JB2-86 | B2B JM2-85 | No specific function. It can only be read by GPIO_input. | It can be read via i2c to<br>GPIO. (GPIO_input<br>(28)) |

| Y5 | B2B JB2-88 | B2B JM2-87 | No specific function. It can only be read by GPIO_input. | It can be read via i2c to<br>GPIO. (GPIO_input<br>(29)) |

| Y6 | B2B JB2-90 | B2B JM2-89 | No specific function. It can only be read by GPIO_input. | It can be read via i2c to<br>GPIO. (GPIO_input<br>(30)) |

It is depends on the module , which bank and pin of FPGA is connected to the module B2B pins that are written in this table.

### UART

| Pin   | CPLD Pin | Connected to | Module UART<br>Signal | Description                    |

|-------|----------|--------------|-----------------------|--------------------------------|

| MIO14 | 40       | B2B JB1-91   | UART0-RX              | In firmware MIO14 <=<br>BDBUS0 |

| MIO15 | 30       | B2B JB1-86   | UART0-TX              | In firmware BDBUS1<br><= MIO15 |

### NOSEQ

NOSEQ is used as TMS signal of JTAG port to program CPLD of TE0715 module. NOSEQ can be used as GPIO pin by user too. It can be controlled differentially for PCB REV03 and REV04 as in the following table is shown:

| NOSEQ | Condition for PCB<br>REV04 or later | Condition for PCB<br>REV03                                                                                                                                                                                                                                                                                             | Related command in linux      | Description                                                                                                                                  |

|-------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| '0'   | USR1 = OFF and<br>USR0 = OFF        | GPIO_output [15:8] =<br>0x01, if access to<br>TE0715 is programmed<br>on the carrier board<br>CPLD and CM1(S3-1)=<br>OFF or CM0(S3-2)=<br>OFF<br>GPIO_output [15:8] =<br>0x01, if no access to<br>TE0715 CPLD is<br>programmed on the<br>carrier board CPLD, it<br>is not dependent on<br>CM0(S3-2) and CM1<br>(S3-1). | i2cset -y 0 0x30<br>0x01 0x01 | If module has no i2c<br>interface for MIO10<br>and MIO11 pins in<br>vivado and linux design<br>, this option for PCB<br>REV03 does not work. |

| '1' | USR1 = ON and USR0<br>= OFF | GPIO_output [15:8] =<br>0x00 , if access to<br>TE0715 is programmed<br>on the carrier board<br>CPLD and CM1(S3-1)=<br>OFF or CM0(S3-2)=<br>OFF                        | i2cset -y 0 0x30<br>0x01 0x00 | If module has no i2c<br>interface for MIO10<br>and MIO11 pins in<br>vivado and linux design<br>, this option for PCB<br>REV03 does not work. |

|-----|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|     |                             | GPIO_output [15:8] =<br>0x00, if no access to<br>TE0715 CPLD is<br>programmed on the<br>carrier board CPLD, it<br>is not dependent on<br>CM0(S3-2) and CM1<br>(S3-1). |                               |                                                                                                                                              |

### PGOOD

PGOOD pin is used as TDO JTAG signal to program CPLD of TE0715 module. PGOOD pin is used to select boot mode for SoC modules too. After booting user can use PGOOD as GPIO pin. PGOOD can be set or reset differentially for PCB REV04 and REV03 as shown:

| PGOOD | Condition for PCB<br>REV04 or later | Condition for PCB<br>REV03                                                                                                                                                                                                                                                                                               | Related command<br>in linux   | Description                                                                                                                                  |

|-------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| .0.   | USR2 = OFF and<br>USR0 = OFF        | GPIO_output [23:16] =<br>0x01, if access to<br>TE0715 is programmed<br>on the carrier board<br>CPLD and CM1(S3-1)=<br>OFF or CM0(S3-2)=<br>OFF<br>GPIO_output [23:16] =<br>0x01, if no access to<br>TE0715 CPLD is<br>programmed on the<br>carrier board CPLD, it<br>is not dependent on<br>CM0(S3-2) and CM1<br>(S3-1). | i2cset -y 0 0x30<br>0x02 0x01 | If module has no i2c<br>interface for MIO10<br>and MIO11 pins in<br>vivado and linux design<br>, this option for PCB<br>REV03 does not work. |

| '1'   | USR2 = ON and USR0<br>= OFF         | GPIO_output [23:16] =<br>0x00, if access to<br>TE0715 is programmed<br>on the carrier board<br>CPLD and CM1(S3-1)=<br>OFF or CM0(S3-2)=<br>OFF<br>GPIO_output [23:16] =<br>0x00, if no access to<br>TE0715 CPLD is<br>programmed on the<br>carrier board CPLD, it<br>is not dependent on<br>CM0(S3-2) and CM1<br>(S3-1). | i2cset -y 0 0x30<br>0x02 0x00 | If module has no i2c<br>interface for MIO10<br>and MIO11 pins in<br>vivado and linux design<br>, this option for PCB<br>REV03 does not work. |

### **On-board LEDs**

LED glows depending on various signals in firmware or pins of CPLD. Additionally to test I2C to GPIO output registers S1 push button can be used to display GPIO\_output[7:0] register on LEDs. If S1 is pushed, ULED1 to ULED7 display GPIO\_output[7:0] register. PHY\_LED1/PHY\_LED1\_A and PHY\_LED2/PHY\_LED2\_A are RJ45 connector right LED and RJ45 connector left LED respectively. These LEDs are using to display states of PGOOD, NOSEQ and EN\_FMC signals.

| RJ45 Connector<br>LED                                     | Designator       | LED Status | Condition                   | Description                                                                       |

|-----------------------------------------------------------|------------------|------------|-----------------------------|-----------------------------------------------------------------------------------|

| PHY_LED1 (Green<br>LED Anode, Yellow                      | J14C (Right LED) | OFF        | PGOOD = '0', NOSEQ<br>= '0' |                                                                                   |

| LED Cathode) ,<br>PHY_LED1_A                              |                  | ON Yellow  | PGOOD = '0', NOSEQ<br>= '1' |                                                                                   |

| (Green LED<br>Cathode, Yellow<br>LED Anode)               |                  | ON Green   | PGOOD = '1', NOSEQ<br>= '0' |                                                                                   |

|                                                           |                  | Blinky     | PGOOD = '1', NOSEQ<br>= '1' |                                                                                   |

| PHY_LED2 (Green<br>LED Cathode,<br>Yellow LED<br>Anode),  | J14B (Left LED)  | ON Green   | EN_FMC = '1'                | Power Ok signal of<br>EN5335QI PowerSoC<br>is high. FMC_VADJ<br>voltage is ok.    |

| PHY_LED2_A<br>(Green LED<br>Anode, Yellow LED<br>Cathode) |                  | Blinky     | EN_FMC = '0'                | Power Ok signal of<br>EN5335QI PowerSoC<br>is low. FMC_VADJ<br>voltage is faulty. |

| LED   | Designator | Connected<br>to Port /<br>Signal | Condition                                 | Connected<br>to Port /<br>Signal | Condition                      | Description                                                                                  |

|-------|------------|----------------------------------|-------------------------------------------|----------------------------------|--------------------------------|----------------------------------------------------------------------------------------------|

| ULED1 | D6         | GPIO_output(0)                   | S1 = '0' (S1<br>push button is<br>pushed) | mode0                            | S1 = '1' (S1 is<br>not pushed) | mode0 = '1' , If<br>CM1(S3-1)=<br>OFF and CM0<br>(S3-2)=<br>OFF FMC_VAD<br>J = 1.8V          |

| ULED2 | D7         | GPIO_output(1)                   | S1 = '0' (S1<br>push button is<br>pushed) | mode1                            | S1 = '1' (S1 is<br>not pushed) | mode1 = '1' , If<br>CM1(S3-1)=<br>ON and CM0<br>(S3-2)=<br>OFF FMC_VAD<br>J = 2.5V           |

| ULED3 | D8         | GPIO_output(2)                   | S1 = '0' (S1<br>push button is<br>pushed) | mode2                            | S1 = '1' (S1 is<br>not pushed) | mode2 = '1', If<br>CM1(S3-1)=<br>OFF and CM0<br>(S3-2)=<br>ON FMC_VADJ<br>= 3.3V             |

| ULED4 | D9         | GPIO_output(3)                   | S1 = '0' (S1<br>push button is<br>pushed) | mode3                            | S1 = '1' (S1 is<br>not pushed) | mode3 = '1' , If<br>CM1(S3-1)=<br>ON and CM0<br>(S3-2)=<br>ON FMC_VAD<br>J = 1.8V            |

| ULED5 | D4         | GPIO_output(4)                   | S1 = '0' (S1<br>push button is<br>pushed) | S2 button<br>(Reset)             | S1 = '1' (S1 is<br>not pushed) | If LED is ON><br>S2 Reset push<br>button is<br>pushed.                                       |

| ULED6 | D15        | GPIO_output(5)                   | S1 = '0' (S1<br>push button is<br>pushed) | SD_DETECT                        | S1 = '1' (S1 is<br>not pushed) | If LED is ON><br>MODE = '1'<br>(QSPI boot<br>mode) else<br>MODE = '0' (SD<br>card boot mode) |

| ULED7 | D14        | GPIO_output(6)                   | S1 = '0' (S1<br>push button is<br>pushed) | Module UART0-<br>RX              | S1 = '1' (S1 is<br>not pushed) |                                                                                              |

| ULED8 D5 GPIO_output(7) S1 = '0' (S1 push button is pushed) Module UART0- S1 = '1' (S1 is not pushed) |

|-------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------|

## I2C to GPIO registers access methods

I2C to GPIO subsystem has 4 output and 4 input 8 bit registers. These registers can be written or read in linux or FSBL code as shown in the following tables:

| GPIO input<br>registers | Address | Read Command in<br>Linux | Read Command in FSBL           | Description                                        |

|-------------------------|---------|--------------------------|--------------------------------|----------------------------------------------------|

| GPIO_input[7:0]         | 0x00    | i2cget -y 0 0x30<br>0x00 | iic_read8(0x30,<br>0x00,&data) | 0x30 is device address.<br>( I2C to GPIO address). |

| GPIO_input[15:8]        | 0x01    | i2cget -y 0 0x30<br>0x01 | iic_read8(0x30,<br>0x01,&data) | 0x30 is device address.<br>( I2C to GPIO address). |

| GPIO_input[23:16]       | 0x02    | i2cget -y 0 0x30<br>0x02 | iic_read8(0x30,<br>0x02,&data) | 0x30 is device address.<br>( I2C to GPIO address). |

| GPIO_input[31:24]       | 0x03    | i2cget -y 0 0x30<br>0x03 | iic_read8(0x30,<br>0x03,&data) | 0x30 is device address.<br>( I2C to GPIO address). |

| GPIO output<br>registers | Address | Write Command in Linux                 | Write Command in FSBL          | Description                                                                        |

|--------------------------|---------|----------------------------------------|--------------------------------|------------------------------------------------------------------------------------|

| GPIO_output[7:0]         | 0x00    | i2cset -y 0 0x30<br>0x00 <data></data> | iic_write8(0x30,<br>0x00,data) | 0x30 is device address.<br>( I2C to GPIO<br>address). 0x00 is<br>register address. |

| GPIO_output[15:8]        | 0x01    | i2cset -y 0 0x30<br>0x01 <data></data> | iic_write8(0x30,<br>0x01,data) | 0x30 is device address.<br>( I2C to GPIO<br>address). 0x01 is<br>register address. |

| GPIO_output[23:16]       | 0x02    | i2cset -y 0 0x30<br>0x02 <data></data> | iic_write8(0x30,<br>0x02,data) | 0x30 is device address.<br>( I2C to GPIO<br>address). 0x02 is<br>register address. |

| GPIO_output[31:24]       | 0x03    | i2cset -y 0 0x30<br>0x03 <data></data> | iic_write8(0x30,<br>0x03,data) | 0x30 is device address.<br>( I2C to GPIO<br>address). 0x03 is<br>register address. |

### **I2C to GPIO registers**

| GPIO_input bit | Port/Signal | Description                                 |

|----------------|-------------|---------------------------------------------|

| 0              | VID0        | EN5335QI Power SoC Voltage<br>Select Line 0 |

| 1              | VID1        | EN5335QI Power SoC Voltage<br>Select Line 1 |

| 2              | VID2        | EN5335QI Power SoC Voltage<br>Select Line 2 |

| 3              | USB_OC      | USB Over Current                            |

| 15             | MIO15       | UART0-TX        |

|----------------|-------------|-----------------|

| 14             | MIO14       | UARTO-RX        |

| 13             | MIO13       |                 |

| 12             | MIO12       |                 |

| 11             | MIO11       | I2C-SDA         |

| 10             | MIO10       | I2C-SCL         |

| 9              | CM1(S3-1)   | DIP Switch S3-A |

| 8              | CM0(S3-2)   | DIP Switch S3-B |

| GPIO input bit | Port/Signal | Description     |

| 7              | USR3        | DIP Switch S4-D |

| 6              | USR2        | DIP Switch S4-C |

| 5              | USR1        | DIP Switch S4-B |

| 4              | USR0        | DIP Switch S4-A |

|                |             |                 |

| GPIO input bit | Port/Signal | Description         |

|----------------|-------------|---------------------|

| 16             | NOSEQ       |                     |

| 17             | PGOOD       |                     |

| 18             | SD_WP       |                     |

| 19             | SD_DETECT   |                     |

| 20             | S1          | User Button         |

| 21             | POK_FMC     | FMC VADJ Power Good |

| 22             | ACBUS4      |                     |

| 23             | ACBUS5      |                     |

| GPIO input bit | Port/Signal | Description |

|----------------|-------------|-------------|

| 24             | Y0          |             |

| 25             | Y1          |             |

| 26             | Y2          |             |

| 27             | Y3          |             |

| 28             | Y4          |             |

| 29 | Y5 |  |

|----|----|--|

| 30 | Y6 |  |

| 31 | X6 |  |

| GPIO output register | Port / Signal | Condition                                                                                  | Description                                                                                                                                                                                                                                                                                 |

|----------------------|---------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_output [7:0]    | ULEDs         | S1 (User push button) = ON<br>(pushed)                                                     | To test GPIO_output it is<br>helpful to check the sent data<br>via i2c to GPIO on the ULEDs.                                                                                                                                                                                                |

| GPIO_output [15:8]   | vir_usr1      | GPIO_output[15:8] = 0x00<br>vir_usr1 = '0'<br>GPIO_output[15:8] = 0x01<br>vir_usr1 = '1'   | This register is used to control<br>NOSEQ pin for PCB REV03.<br>If no access to TE0715<br>CPLD or access to TE0715<br>CPLD jed file is programmed<br>on the CPLD of carrier board<br>and CM0(S3-2) and CM1(S3-<br>1) are OFF:<br>vir_usr1 = '1' NOSEQ = '0'*<br>vir_usr1 = '0' NOSEQ = '1'* |

| GPIO_output [23:16]  | vir_usr2      | GPIO_output[23:16] = 0x00<br>vir_usr2 = '0'<br>GPIO_output[23:16] = 0x01<br>vir_usr2 = '1' | This register is used to control<br>PGOOD pin for PCB REV03.<br>If no access to TE0715 CPLD<br>or access to TE0715 CPLD<br>jed file is programmed on the<br>CPLD of carrier board and<br>CM0(S3-2) and CM1(S3-1)<br>are OFF:<br>vir_usr2 = '1' PGOOD= '0'<br>vir_usr2 = '0' PGOOD = '1'     |

| GPIO_output [31:24]  |               |                                                                                            |                                                                                                                                                                                                                                                                                             |

\*Note: This is only valid for PCB REV03. For PCB REV04 vir\_usr1,vir\_usr2 and vir\_usr3 are not be used. For PCB REV04 PGOOD and NOSEQ can be controlled via USR2 and USR1 dip switches respectively.

## Appx. A: Change History

## **Revision Changes**

REV02 to REV03

- JTAG timing correction

- Renaming ports according to the schematic REV04

- RGPIO is removed.

- I2C to GPIO sub system is added for communication between FPGA on the module and CPLD on the carrier board. (MIO10 --> SCL , MIO11 --> SDA)

- Access to CPLD chip of TE0715 either via USR0 Dip switch for PCB REV04 or via CM0 and CM1 for PCB REV03 revisions

- In PCB REV04 USR0 is used to access to TE0715 CPLD

- In PCB REV04 USR1 is used to change NOSEQ signal, if no access to TE0715 CPLD is active (USR0 = OFF)

- In PCB REV04 USR2 is used to change PGOOD, if no access to TE0715 CPLD is active (USR0 = OFF)

- In PCB REV04 USR3 is used to change JTAGMODE signal of CPLD of module. USR3 = OFF --> Access to FPGA, USR3 = ON --> Access to CPLD of module

- In PCB REV03 CM0 and CM1 dip switches are used to access to CPLD of TE0715 or other modules.

- Displaying PGOOD and NOSEQ signal states on PHY\_LED1/PHY\_LED1\_A

- Displaying state of POK\_FMC (power ok signal of EN5335QI PowerSoC) on PHY\_LED2/PHY\_LED2\_A

REV01 to REV02

- Power Management

VADJ is switchable by S3 dip switches

Reset Management

only little changes

RGPIO Interface to FPGA

DCDC surgest

- RGPIO support

- LED

- new Order and accessible by RGPIO

Module CPLD access is possible know

## **Document Change History**

To get content of older revision got to "Change History" of this page and select older document revision number.

| Date       | Document<br>Revision | CPLD Firmware<br>Revision | Supported PCB<br>Revision | Authors | Description                                   |

|------------|----------------------|---------------------------|---------------------------|---------|-----------------------------------------------|

|            |                      | REV03                     | REV03, REV04              |         | REV03 release                                 |

|            |                      |                           |                           |         | <ul> <li>Firmware<br/>release (SC-</li> </ul> |

| Er         | Er                   |                           |                           | Er      | PGM-TE0705-<br>PCB_REV0304                    |

| ro         | ro                   |                           |                           | ro      | CARRIER-<br>CPLD_REV03-                       |

| r          | r                    |                           |                           | r       | 20230329.zip)<br>• I2C to GPIO<br>added       |

| re         | re                   |                           |                           | re      | RGPIO     removed                             |

| n          | n                    |                           |                           | n       | ULEDs and     PHY_LEDs                        |

| d          | d                    |                           |                           | d       | function<br>changed                           |

| er         | er                   |                           |                           | er      |                                               |

| in         | in                   |                           |                           | in      |                                               |

| g          | g                    |                           |                           | g       |                                               |

| m          | m                    |                           |                           | m       |                                               |

| ac         | ac                   |                           |                           | ac      |                                               |

| ro         | ro                   |                           |                           | ro      |                                               |

| <b>'</b> p | 'p                   |                           |                           | 'p      |                                               |

| а          | а                    |                           |                           | а       |                                               |

| g          | g                    |                           |                           | g       |                                               |

| e-         | e-                   |                           |                           | e-      |                                               |

| in         | in                   |                           |                           | in      |                                               |

| fo'        | fo'                  |                           |                           | fo'     |                                               |

| А          | А                    |                           |                           | А       |                                               |

| m          | m                    |                           |                           | m       |                                               |

| bi         | bi                   |                           |                           | bi      |                                               |

| gu         | gu                   |                           |                           | gu      |                                               |

| ou         | ou                   |                           |                           | ou      |                                               |

| S          | s                    |                           |                           | S       |                                               |

| m          | m                    |                           |                           | m       |                                               |

et et et ho ho ho d d d ov ov ov erl erl erl oa oa oa di di di ng ng ng fo fo fo r r r m m m et et et ho ho ho d d d jd jd jd k. k. k. pr pr pr ох ох ох y2 y2 y2 79 79 79 .\$ .\$ .\$ Pr Pr Pr ох ох ох y4 y4 y4 02 02 02 2# 2# 2# ha ha ha s s s С С С on on on te te te nt nt nt Le Le Le ve ve ve IP IP IP er er er mi mi mi SS SS SS io io io

n. n. n. С С С an an an no no no t t t re re re so so so lv lv lv е е е w w w hi hi hi ch ch ch m m m et et et ho ho ho d d d to to to in in in vo vo vo ke ke ke fo fo fo r r r [n [n [n ull ull ull , , , cl cl cl as as as s s s ja ja ja va va va la la la ng ng ng St St St rin rin rin g, g, g, cl cl cl as as as

s s s со со со m. m. m. atl atl atl as as as si si si an an an со со со nfl nfl nfl ue ue ue nc nc nc e. e. e. ра ра ра ge ge ge s. s. s. Ρ Ρ Ρ ag ag ag e] e] e] du du du е е е to to to ov ov ov erl erl erl ар ар ар pi pi pi ng ng ng pr pr pr ot ot ot ot ot ot ур ур ур es es es be be be tw tw tw ee ee ee n: n: n: [in [in [in te te te rf rf rf

ac ac ac е е е со со со m. m. m. atl atl atl as as as si si si an an an со со со nfl nfl nfl ue ue ue nc nc nc e. e. e. us us us er er er С С С on on on flu flu flu en en en се ce се U U U se se se r, r, r, cl cl cl as as as s s s ja ja ja va va va la la la ng ng ng St St St rin rin rin g, g, g, cl cl cl as as as

s s s со со со m. m. m. atl atl atl as as as si si si an an an со со со nfl nfl nfl ue ue ue nc nc nc e. e. e. со со со re re re С С С on on on te te te nt nt nt Е Е Е nti nti nti ty ty ty 0 0 0 bj bj bj ес ec ec t] t] t] [in [in [in te te te rf rf rf ac ac ac е е е со со со m. m. m. atl atl atl as as as si si si an an an

us us us er er er U U U se se se r, r, r, cl cl cl as as as s s s ja ja ja va va va la la la ng ng ng St St St rin rin rin g, g, g, cl cl cl as as as s s s со со со m. m. m. atl atl atl as as as si si si an an an со со со nfl nfl nfl ue ue ue nc nc nc e. e. e. со со со re re re С С С on on on te te te

| 11 17      |       | 1     |              | 1 1           | 1                     |

|------------|-------|-------|--------------|---------------|-----------------------|

| nt         | nt    |       |              | nt            |                       |

| E          | E     |       |              | E             |                       |

| nti        | nti   |       |              | nti           |                       |

| ty         | ty    |       |              | ty            |                       |

| о          | О     |       |              | 0             |                       |

| bj         | bj    |       |              | bj            |                       |

| ec         | ec    |       |              | ec            |                       |

| t]         | t]    |       |              | t]            |                       |

| ч<br>,     | L. L. |       |              | L,            |                       |

|            |       |       |              |               |                       |

| 2017-06-08 | v.34  | REV02 | REV03,REV04  | John Hartfiel | document style update |

| 2016-11-17 | v.27  | REV02 | REV03, REV04 | John Hartfiel | Revision 02 finished  |

|            |       |       |              |               |                       |

| 2016-11-04 |       |       |              |               | Initial release       |

|            | v.1   |       |              |               |                       |

|            |       |       |              | Er            |                       |

|            |       |       |              |               |                       |

|            |       |       |              | ro            |                       |

|            |       |       |              | r             |                       |

|            |       |       |              | re            |                       |

|            |       |       |              | n             |                       |

|            |       |       |              | d             |                       |

|            |       |       |              | er            |                       |

|            |       |       |              | in            |                       |

|            |       |       |              | g             |                       |

|            |       |       |              | m             |                       |

|            |       |       |              | ac            |                       |

|            |       |       |              | ro            |                       |

|            |       |       |              | 'p            |                       |

|            |       |       |              | a             |                       |

|            |       |       |              |               |                       |

|            |       |       |              | g             |                       |

|            |       |       |              | e-            |                       |

|            |       |       |              | in            |                       |

|            |       |       |              | fo'           |                       |

|            |       |       |              | А             |                       |

|            |       |       |              |               |                       |

|            |       |       |              | m             |                       |

|            |       |       |              | bi            |                       |

|            |       |       |              | gu            |                       |

|            |       |       |              | ou            |                       |

|            |       |       |              | S             |                       |

|            |       | I     |              | I             |                       |

m et ho d ov erl oa di ng fo r m et ho d jd k. pr ох y2 79 .\$ Pr ох y4 02 2# ha s С on te nt Le ve IP er mi SS

io n. С an no t re so lv е w hi ch m et ho d to in vo ke fo r [n ull , cl as s ja va la ng St rin g, cl

as s со m. atl as si an со nfl ue nc e. ра ge s. Ρ ag e] du е to ov erl ар pi ng pr ot ot ур es be tw ee n: [in te

rf ac е со m. atl as si an со nfl ue nc e. us er С on flu en се U se r, cl as s ja va la ng St rin g, cl

as s со m. atl as si an со nfl ue nc e. со re С on te nt Е nti ty 0 bj ес t] [in te rf ac е со m. atl as si an us er U se r, cl as s ja va la ng St rin g, cl as s со m. atl as si an со nfl ue nc e. со re С on

|     |  | te  |  |

|-----|--|-----|--|

|     |  | nt  |  |

|     |  | E   |  |

|     |  | nti |  |

|     |  |     |  |

|     |  | ty  |  |

|     |  | 0   |  |

|     |  | bj  |  |

|     |  | ec  |  |

|     |  | t]  |  |

|     |  |     |  |

|     |  |     |  |

| All |  |     |  |

|     |  |     |  |

|     |  |     |  |

|     |  | Er  |  |

|     |  | ro  |  |

|     |  | r   |  |

|     |  | re  |  |

|     |  | n   |  |

|     |  | d   |  |

|     |  | er  |  |

|     |  | in  |  |

|     |  |     |  |

|     |  | g   |  |

|     |  | m   |  |

|     |  | ac  |  |

|     |  | ro  |  |

|     |  | 'p  |  |

|     |  | а   |  |

|     |  | g   |  |

|     |  | e-  |  |

|     |  | in  |  |

|     |  | fo' |  |

|     |  |     |  |

|     |  | А   |  |

|     |  | m   |  |

|     |  | bi  |  |

|     |  | gu  |  |

|     |  | ou  |  |

|     |  | s   |  |

|     |  |     |  |

|     |  | m   |  |

|     |  | et  |  |

|     |  | . 1 |  |

ho d ov erl oa di ng fo r m et ho d jd k. pr ох y2 79 .\$ Pr ох y4 02 2# ha s С on te nt Le ve IP er mi SS io n.

С an no t re so lv е w hi ch m et ho d to in vo ke fo r [n ull , cl as s ja va la ng St rin g, cl as s

со m. atl as si an со nfl ue nc e. ра ge s. Ρ ag e] du е to ov erl ар pi ng pr ot ot ур es be tw ee n: [in te rf ac

е со m. atl as si an со nfl ue nc e. us er С on flu en се U se r, cl as s ja va la ng St rin g, cl as s

со m. atl as si an со nfl ue nc e. со re С on te nt Е nti ty 0 bj ec t] [in te rf ac е со m. atl as si an us

er U se r, cl as s ja va la ng St rin g, cl as s со m. atl as si an со nfl ue nc e. со re С on te nt

## Appx. B: Legal Notices

### **Data Privacy**

Please also note our data protection declaration at https://www.trenz-electronic.de/en/Data-protection-Privacy

### **Document Warranty**

The material contained in this document is provided "as is" and is subject to being changed at any time without notice. Trenz Electronic does not warrant the accuracy and completeness of the materials in this document. Further, to the maximum extent permitted by applicable law, Trenz Electronic disclaims all warranties, either express or implied, with regard to this document and any information contained herein, including but not limited to the implied warranties of merchantability, fitness for a particular purpose or non infringement of intellectual property. Trenz Electronic shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein.

## **Limitation of Liability**

In no event will Trenz Electronic, its suppliers, or other third parties mentioned in this document be liable for any damages whatsoever (including, without limitation, those resulting from lost profits, lost data or business interruption) arising out of the use, inability to use, or the results of use of this document, any documents linked to this document, or the materials or information contained at any or all such documents. If your use of the materials or information from this document results in the need for servicing, repair or correction of equipment or data, you assume all costs thereof.

## **Copyright Notice**

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Trenz Electronic.

## **Technology Licenses**

The hardware / firmware / software described in this document are furnished under a license and may be used /modified / copied only in accordance with the terms of such license.

## **Environmental Protection**

To confront directly with the responsibility toward the environment, the global community and eventually also oneself. Such a resolution should be integral part not only of everybody's life. Also enterprises shall be conscious of their social responsibility and contribute to the preservation of our common living space. That is why Trenz Electronic invests in the protection of our Environment.

### **REACH, RoHS and WEEE**

#### REACH

Trenz Electronic is a manufacturer and a distributor of electronic products. It is therefore a so called downstream user in the sense of REACH. The products we supply to you are solely non-chemical products (goods). Moreover and under normal and reasonably foreseeable circumstances of application, the goods supplied to you shall not release any substance. For that, Trenz Electronic is obliged to neither register nor to provide safety data sheet. According to present knowledge and to best of our knowledge, no SVHC (Substances of Very High Concern) on the Candidate List are contained in our products. Furthermore, we will immediately and unsolicited inform our customers in compliance with REACH - Article 33 if any substance present in our goods (above a concentration of 0,1 % weight by weight) will be classified as SVHC by the European Chemicals Agency (ECHA).

#### RoHS

Trenz Electronic GmbH herewith declares that all its products are developed, manufactured and distributed RoHS compliant.

#### WEEE

Information for users within the European Union in accordance with Directive 2002/96/EC of the European Parliament and of the Council of 27 January 2003 on waste electrical and electronic equipment (WEEE).