...

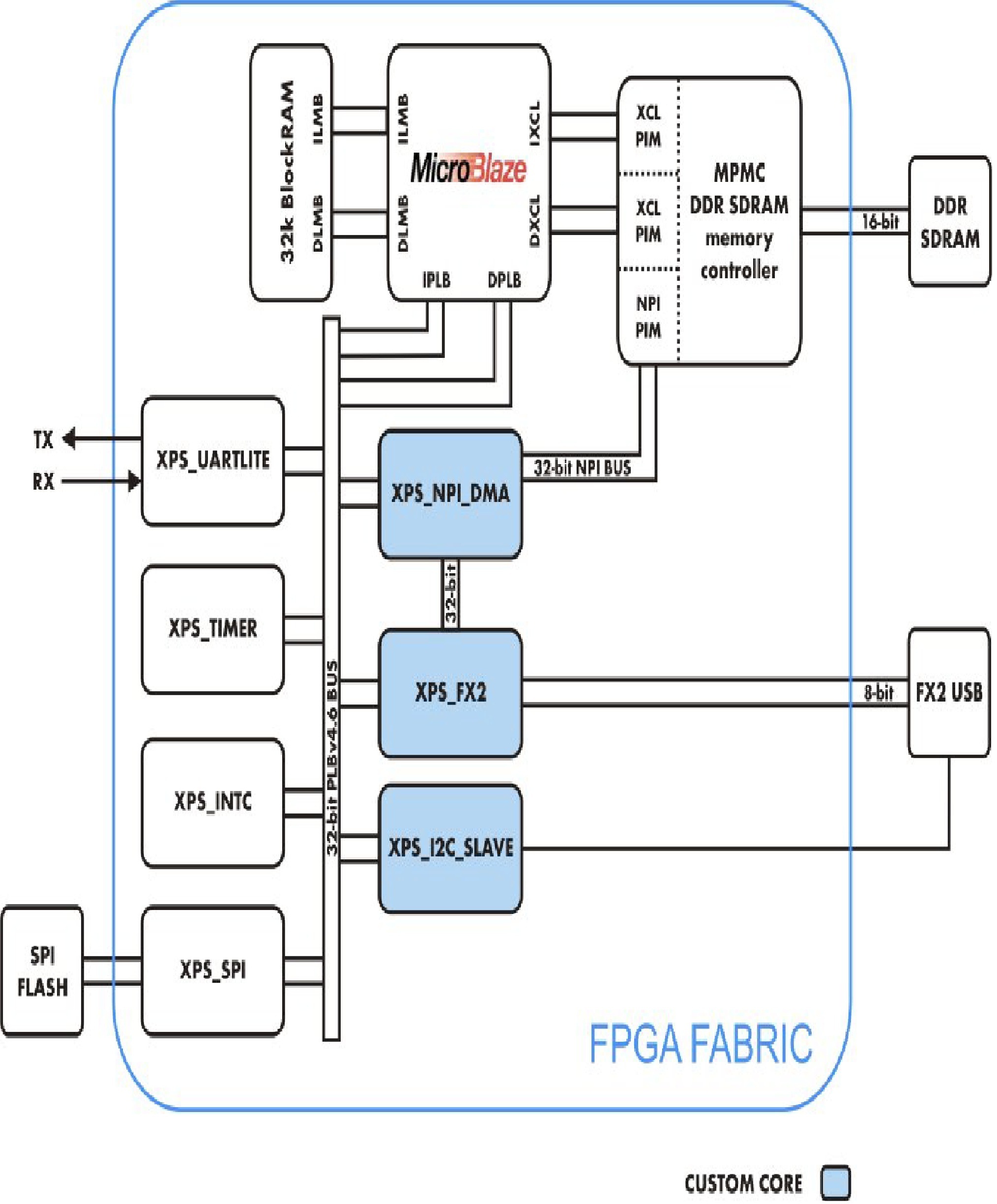

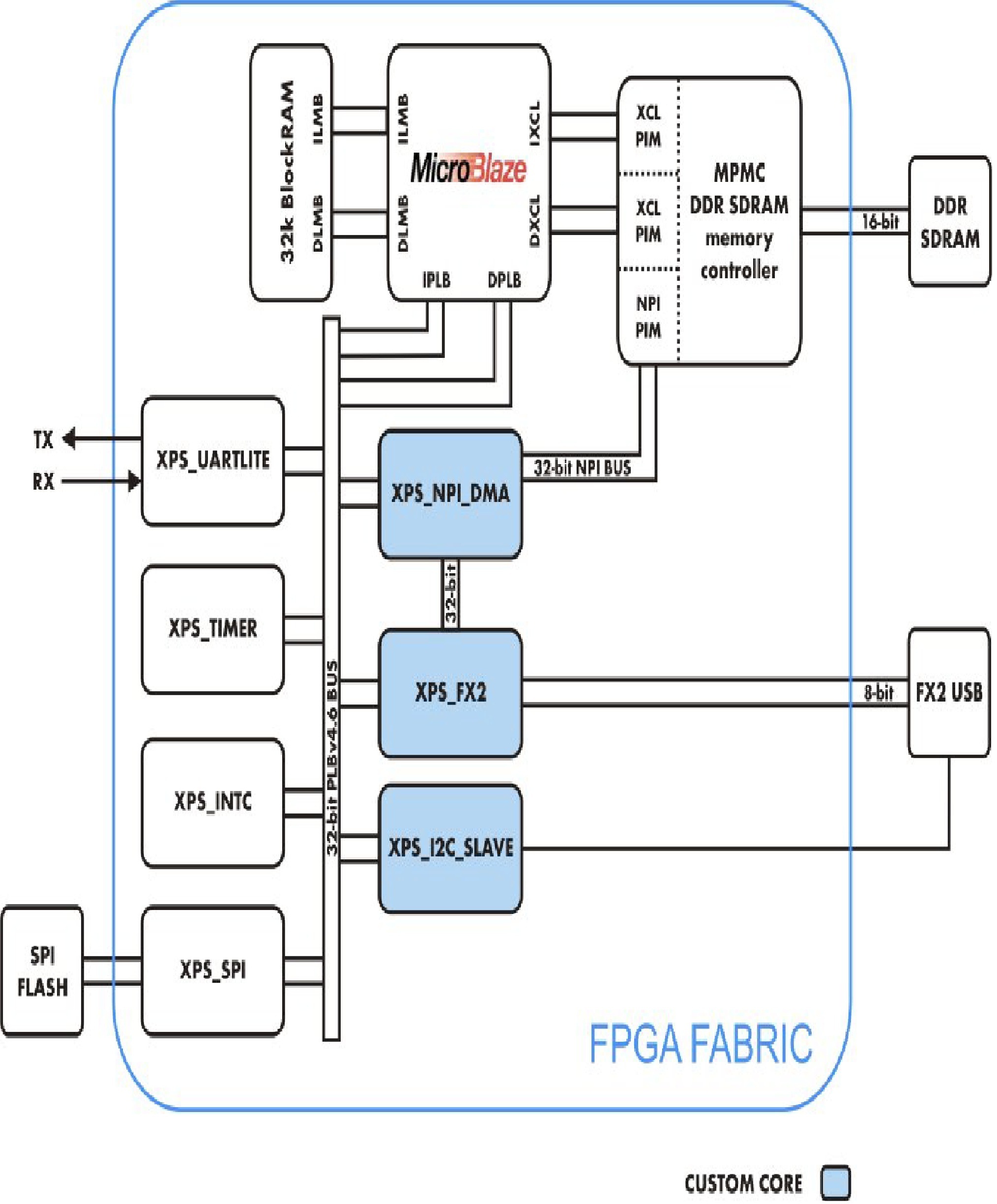

Besides standard IP cores, the reference architecture contains three custom IP cores:

| Scroll Title |

|---|

| title | Reference IP custom blocks dependencies and connections |

|---|

|

| custom IP block | brief description | is used to deliver MB Command

to FPGA's MicroBlaze soft μP

(through FX22MB_REGs)

and retrieve "reply"

(through MB2FX2_REGs) | is used to realize a

FPGA ↔ FX2 μC

connection | is used to realize a

FPGA ↔ DRAM

connection |

|---|

| XPS_I2C_SLAVE |

|

...

...

...

| custom DMA between DDR SDRAM and other multiple sources; |  |  |  | | XPS_FX2 |

|

...

| used for high speed bidirectional communication between

the FPGA and a |

|

...

| Info |

|---|

| XPS_NPI_DMA and XPS_FX2 could be used to realize a USB FX2 microcontroller ↔ DRAM connection and (using the SW API Layer) a USB (host computer) ↔ DRAM connection |

| Scroll pdf title |

|---|

| title | Reference architecture block diagram. |

|---|

|

|

...