...

| Scroll Title |

|---|

| anchor | Table_HWM |

|---|

| title | Hardware Modules |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | EMMC | Others | Notes |

|---|

| TE0835-0102-MXE21-A | 25dr_1e_4gb | REV1REV2 | 4GB | 128MB | NA | NA | NA |

|

Design supports following carriers:

| Scroll Title |

|---|

| anchor | Table_HWC |

|---|

| title | Hardware Carrier |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Carrier Model | Notes |

|---|

| TEB0835- |

01

|

Additional HW Requirements:

...

- Prepare HW like described on section TE0835 Test Board#Hardware Setup

- Connect UART USB (most cases same as JTAG)

- Select SD Card as Boot Mode (or QSPI - depending on step 1)

Note: See TRM of the Carrier, which is used. - Power On PCB

Note: 1. Zynqmp RFSoC Boot ROM loads FSBL from SD into OCM, 2. FSBL loads U-boot from SD into DDR, 3. U-boot load Linux from SD into DDR - Open the RF Analyzer GUI

- Click on Connect

- Adjust the desired JTAG frequency (for example 30MHZ)

- Give the generated bitstream file path

- Click on Download Bitstream on the FPGA

- When downloading is finished, click on Select Target

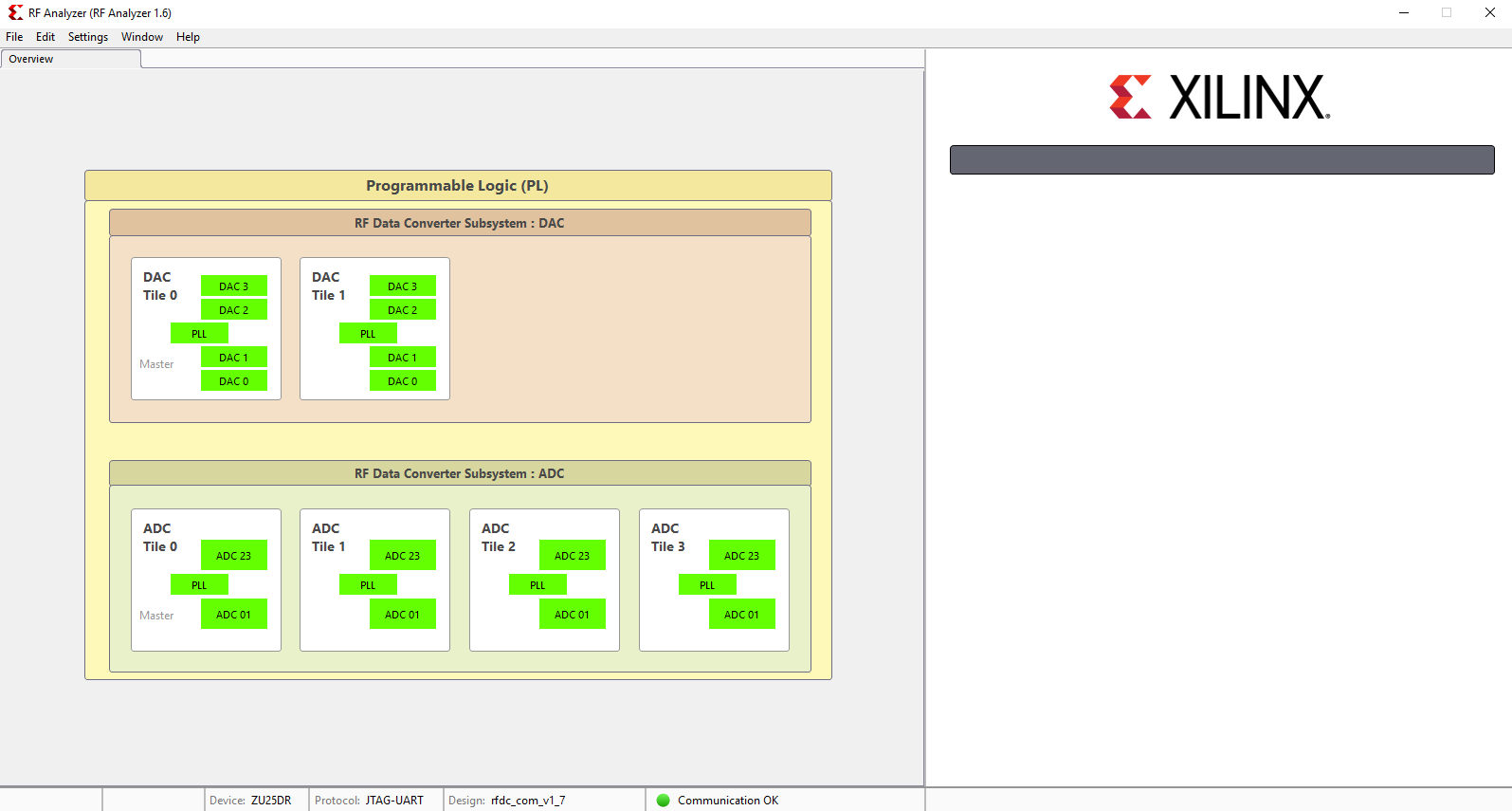

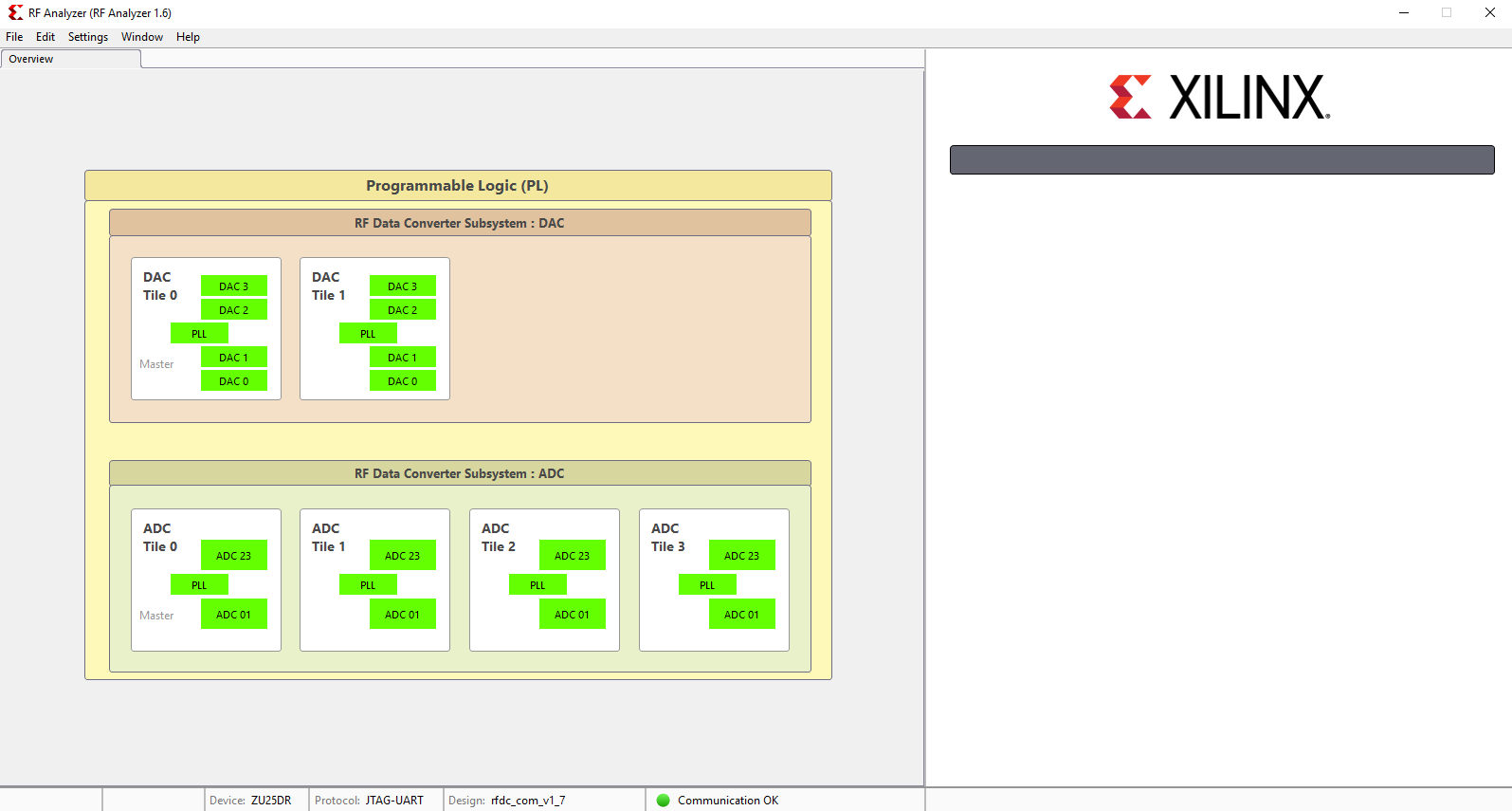

- After the initilalisation, all ADCs/DACs tiles are visible

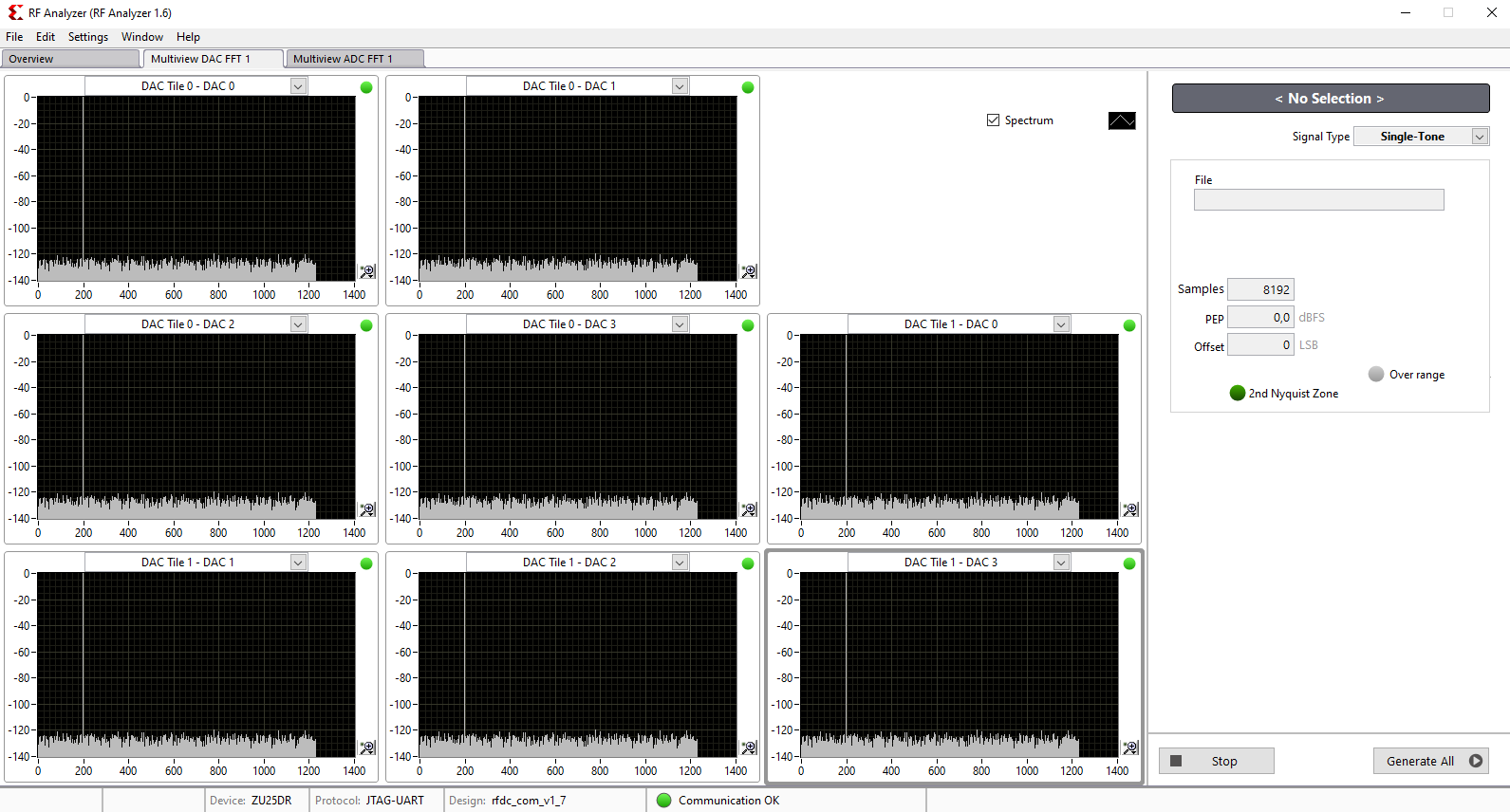

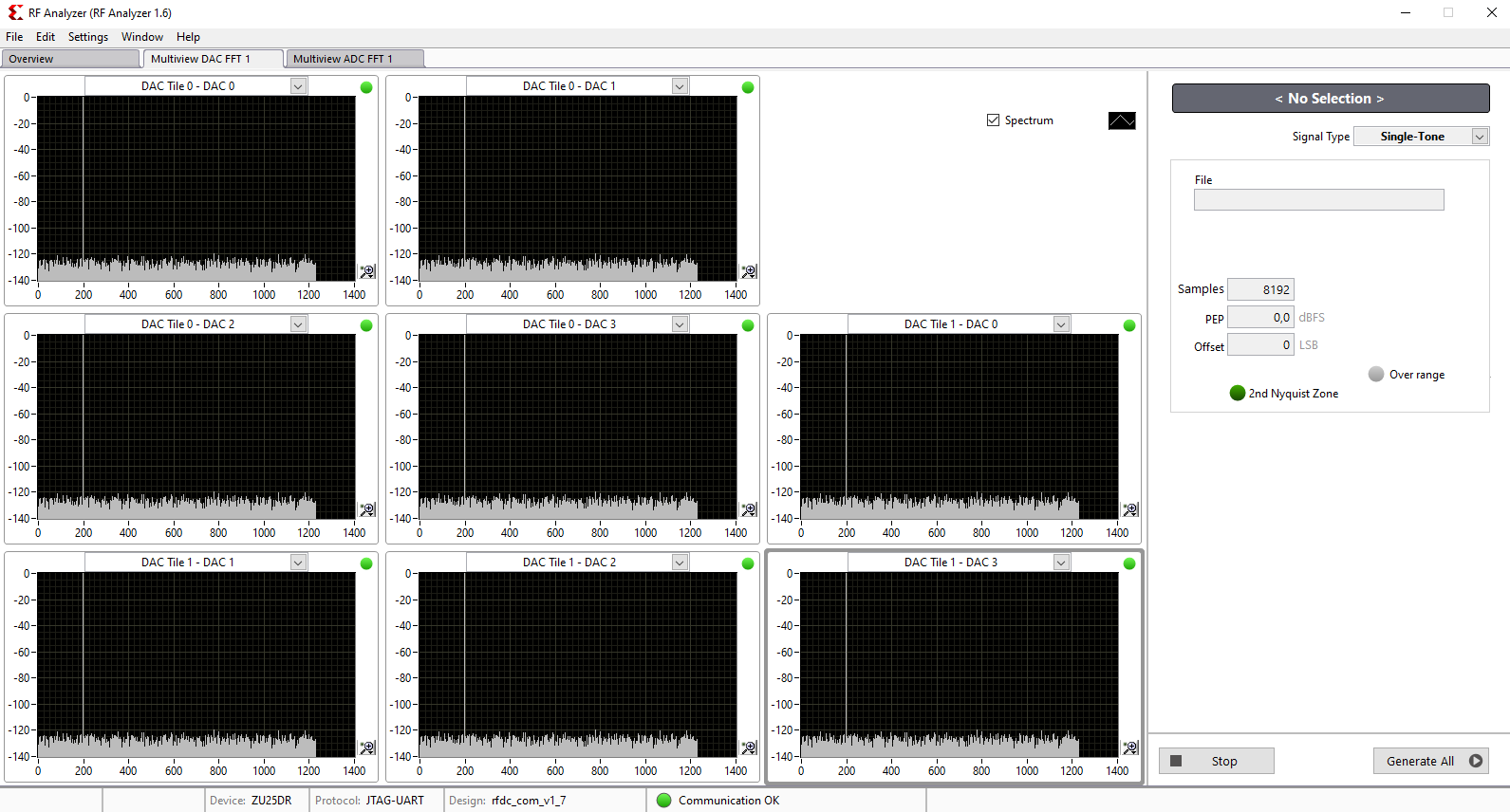

- Click on desired DAC tile and choose a DAC (for example DAC0)

- Adjust the desired DAC properties (for example output frequency)

- Click on Generate to generate the signal in output of DAC

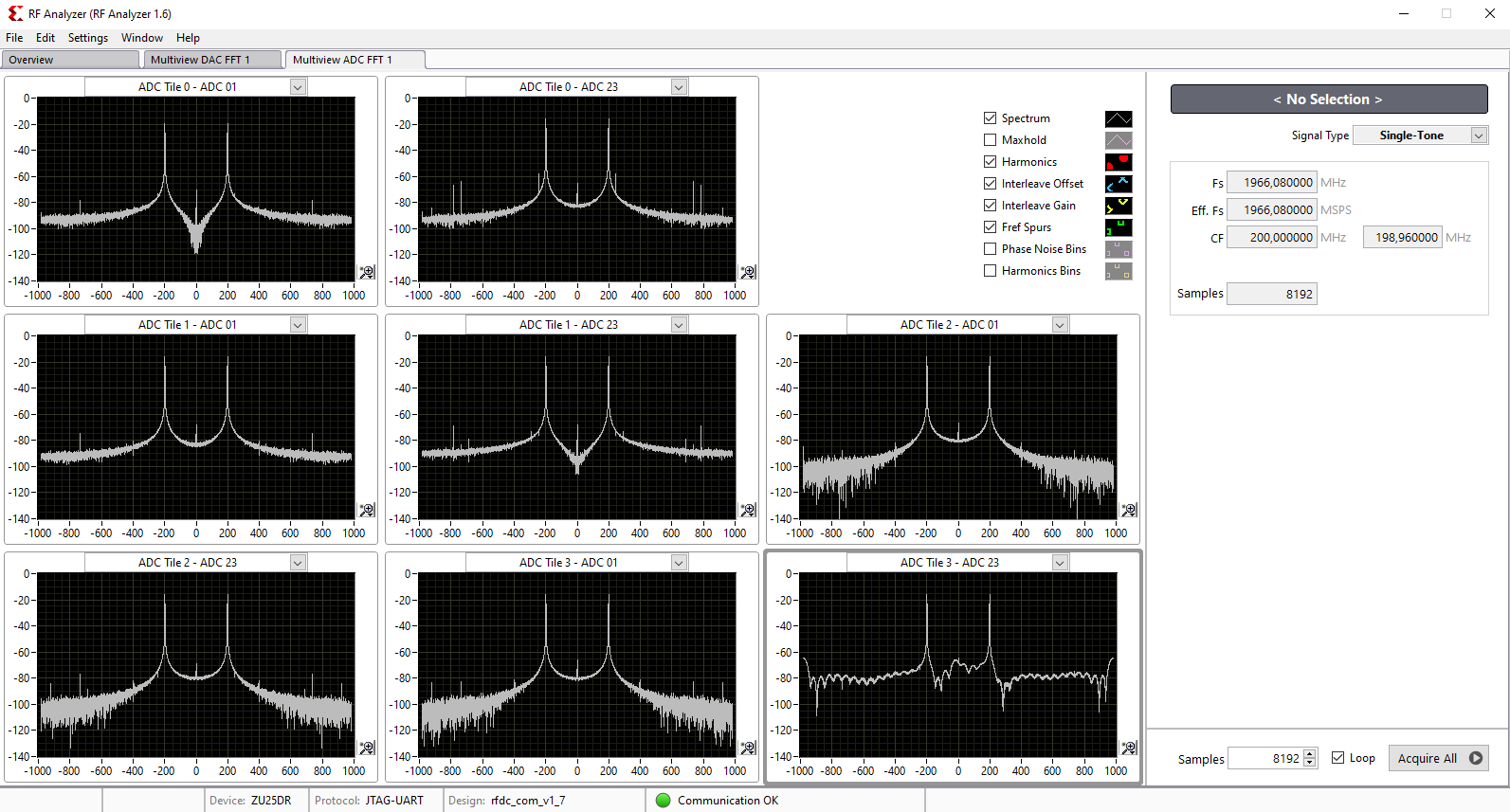

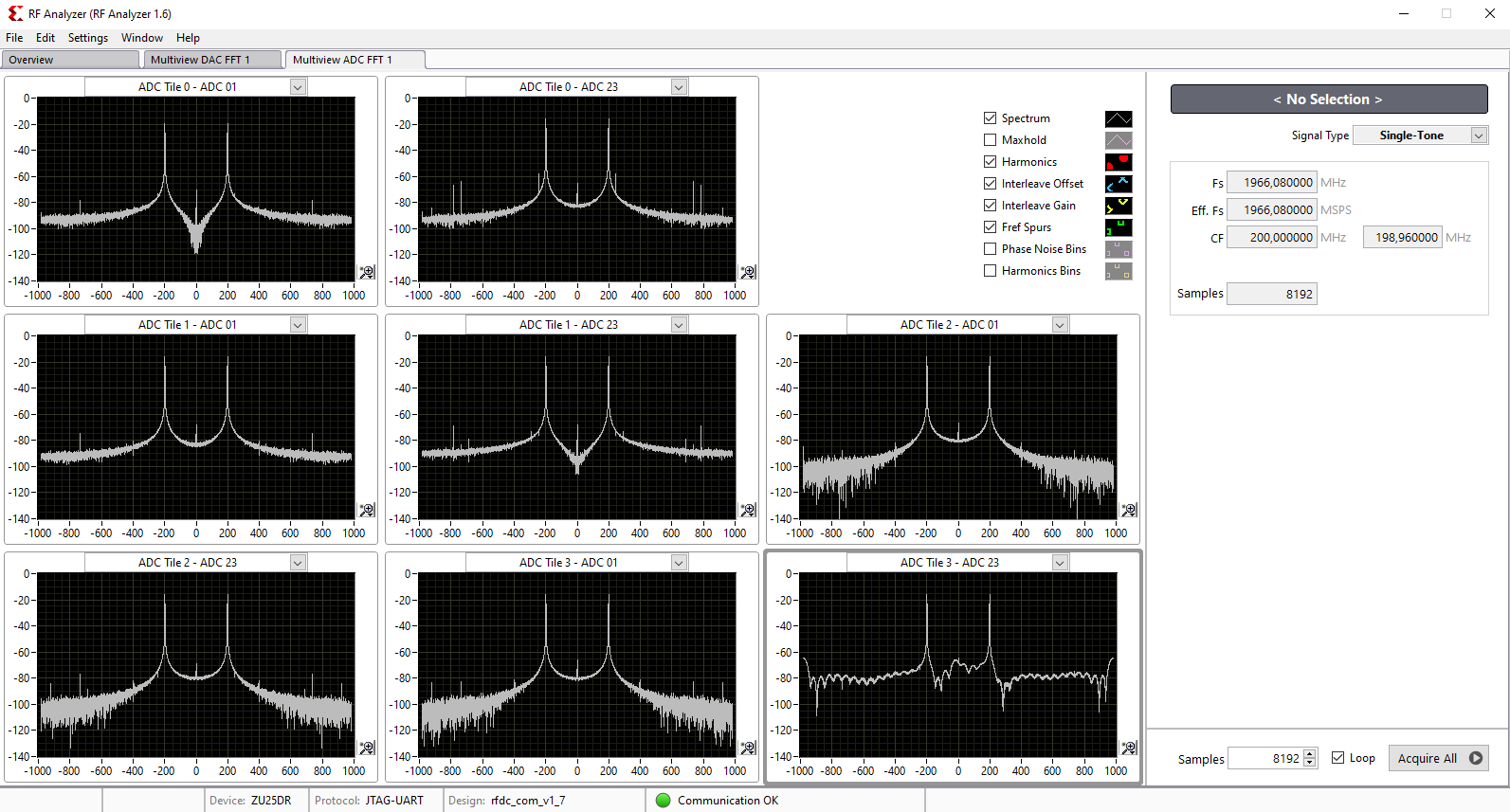

- Click on the related ADC tile and choose the related ADC (for example ADC0)

- Click on Acquire to aqcuire the input signal

- The spectum of the DAC output signal can be seen now. The signal can be visible in time domain too.

- Tip: In menu Window click on Multiview to see all of DACs and ADCs simultaneously.

| Expand |

|---|

|

Image Added Image Added

|

| Expand |

|---|

|

Image Added Image Added

|

| Expand |

|---|

|

Image Added Image Added

|

Linux

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:

- User Name: root

- Password: root

- You can use Linux shell now.

- I2C 0 Bus type: i2cdetect -y -r 0

- I2C 1 Bus type: i2cdetect -y -r 1

- RTC check: dmesg | grep rtc

- ETH0 works with udhcpc

- USB type "lsusb" or connect USB2.0 device

- Option Features

- Webserver to get access to Zynqmp RFSoC

- insert IP on web browser to start web interface

- init.sh scripts

- add init.sh script on SD, content will be load automatically on startup (template included in ./misc/SD)

...

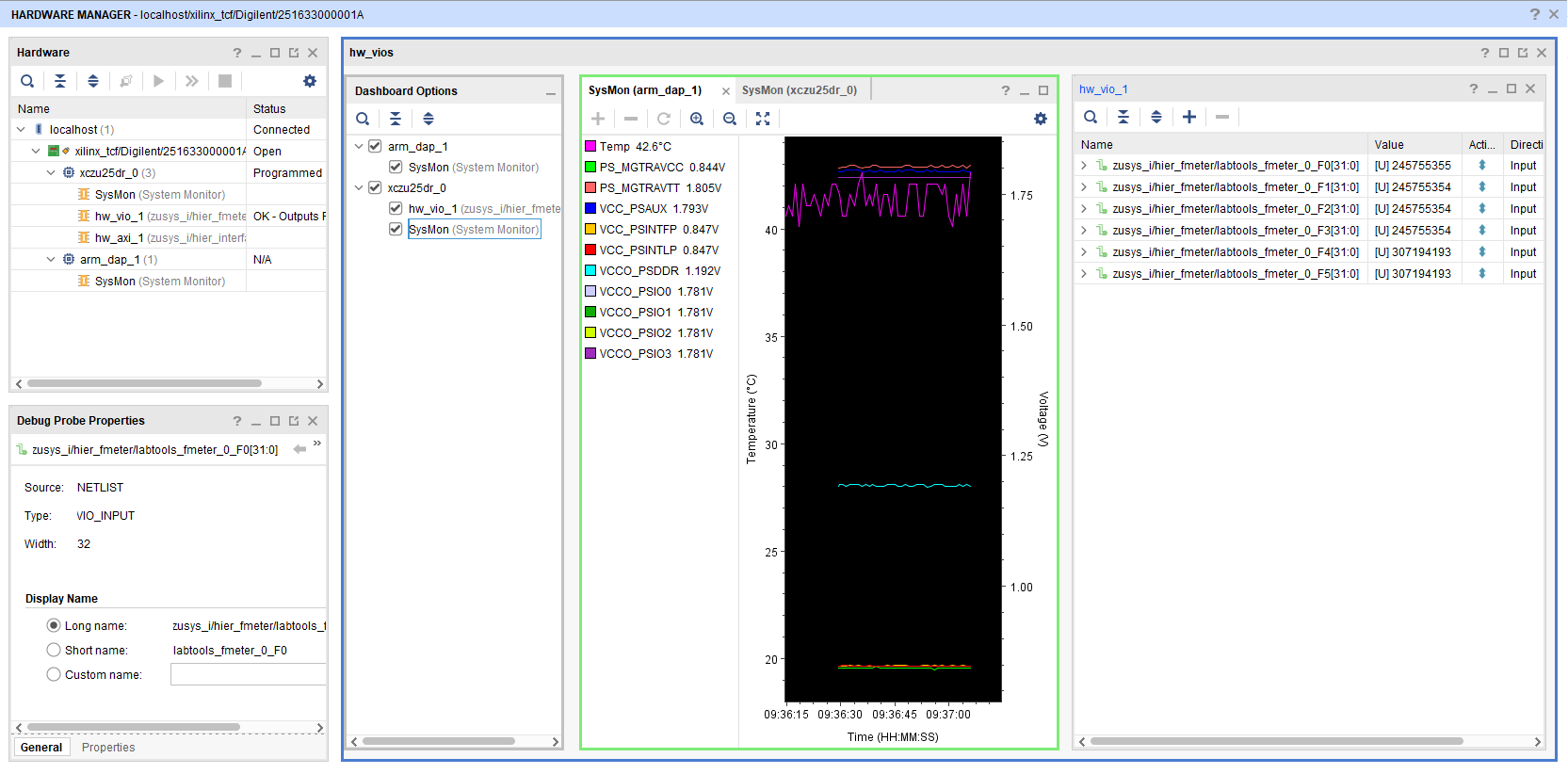

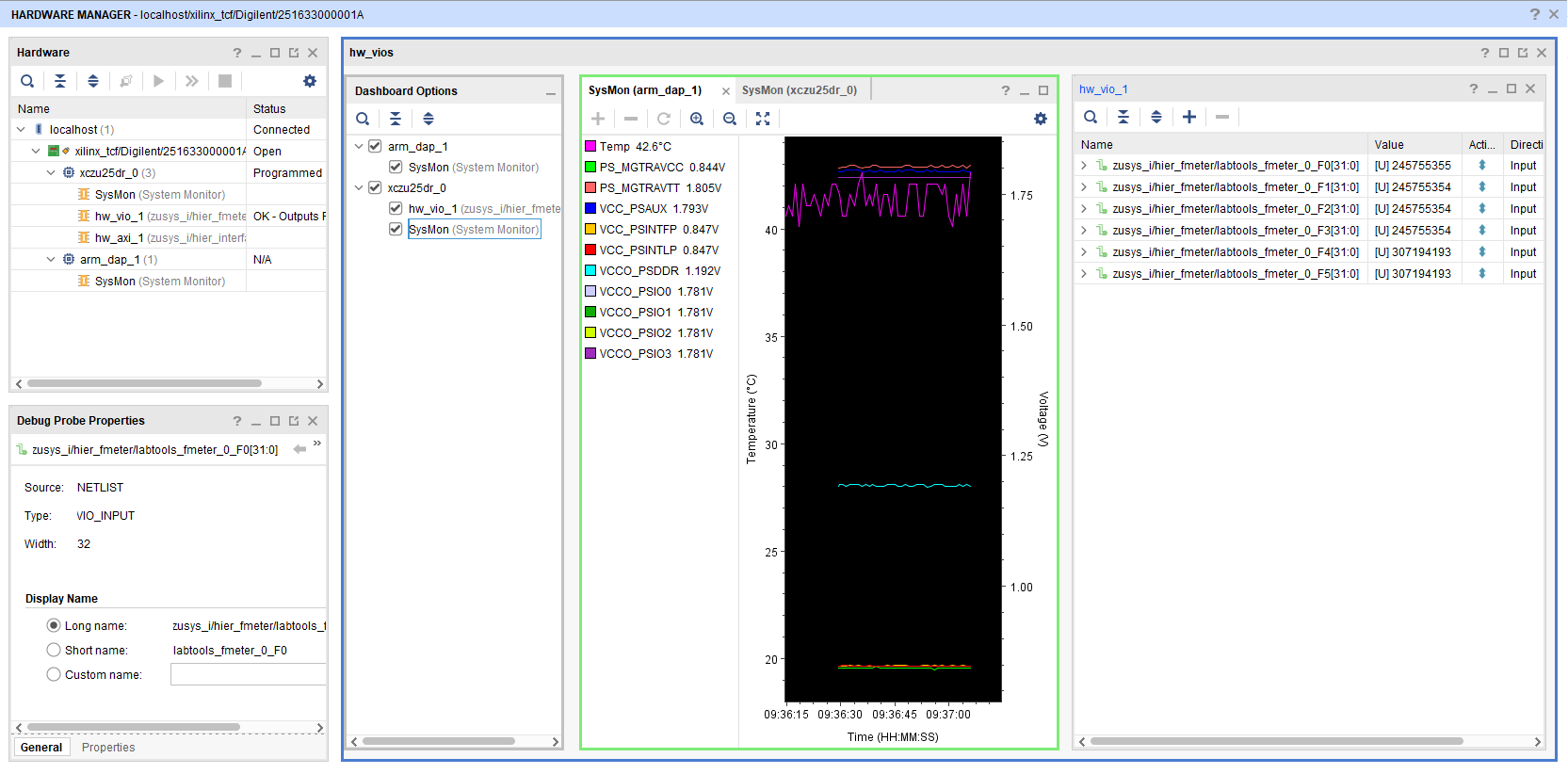

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title | Vivado Hardware Manager |

|---|

|

Image Added Image Added |

System Design - Vivado

Block Design

| Scroll Title |

|---|

|

| anchor | Figure_BD |

|---|

title |

Block Design

...

PS Interfaces

...