...

| Scroll Title |

|---|

| anchor | Table_DRH |

|---|

| title | Design Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Vivado | Project Built | Authors | Description |

|---|

| 2020-10-2627 | 2019.2 | TE0835-test_board_noprebuilt-vivado_2019.2-build_15_2020102612520520201027100145.zip

TE0835-test_board-vivado_2019.2-build_15_2020102612515120201027100128.zip | Mohsen Chamanbaz | |

|

...

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

...

| Scroll Title |

|---|

| anchor | Table_AHW |

|---|

| title | Additional Hardware |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Additional Hardware | Notes |

|---|

| Micro USB Cable for JTAG/UART |

| | Cooler | It's recommended to use cooler on Zynqmp RFSoC device | | SMA male connector cable | Some ADC inputs/DAC outouts have the SMA connector | | UFL female connector cable | Some ADC inputs/DAC outouts have the UFL connector | | Ethernet cable |

| | SD card | 16GB | | Signal generator (optional) | To feed a desired signal to the input of ADC | | Oscilloscope (optional) | To monitor the output signal of DACs. | | PC | with With ATX Powrer Power supply and PCIe X? X8 slot |

|

Content

...

- Plug the TE0835 module on the TEB0835 carrier board

- Install the cooler on the RFSoC chip

- Connect the micro USB cable to the J29 connector

- Plug the 12V power supply cable to the J19 connectorboard on the PCIe port of the PC

- Plug the prepared SD card on the SD card socket (J28)

- Connect a cable with SMA or UFL connector to one of the DAC connector( for example DAC0 J9) and feed it back to the related ADC input (for example ADC0 J1)

- (optional) A signal generator can be used to feed desired sinal to ADC input.

- (optional) An oscilloscope can be used to monitor the output signal of DAC.

...

- Open the RF Analyzer GUI

- Click on Connect button

- Adjust the desired JTAG frequency (for example 30MHZ)

- Give the generated bitstream file path

- Click on Download Bitstream button to load the Bitstream file on the FPGA

- When downloading is finished, click on Select Target button

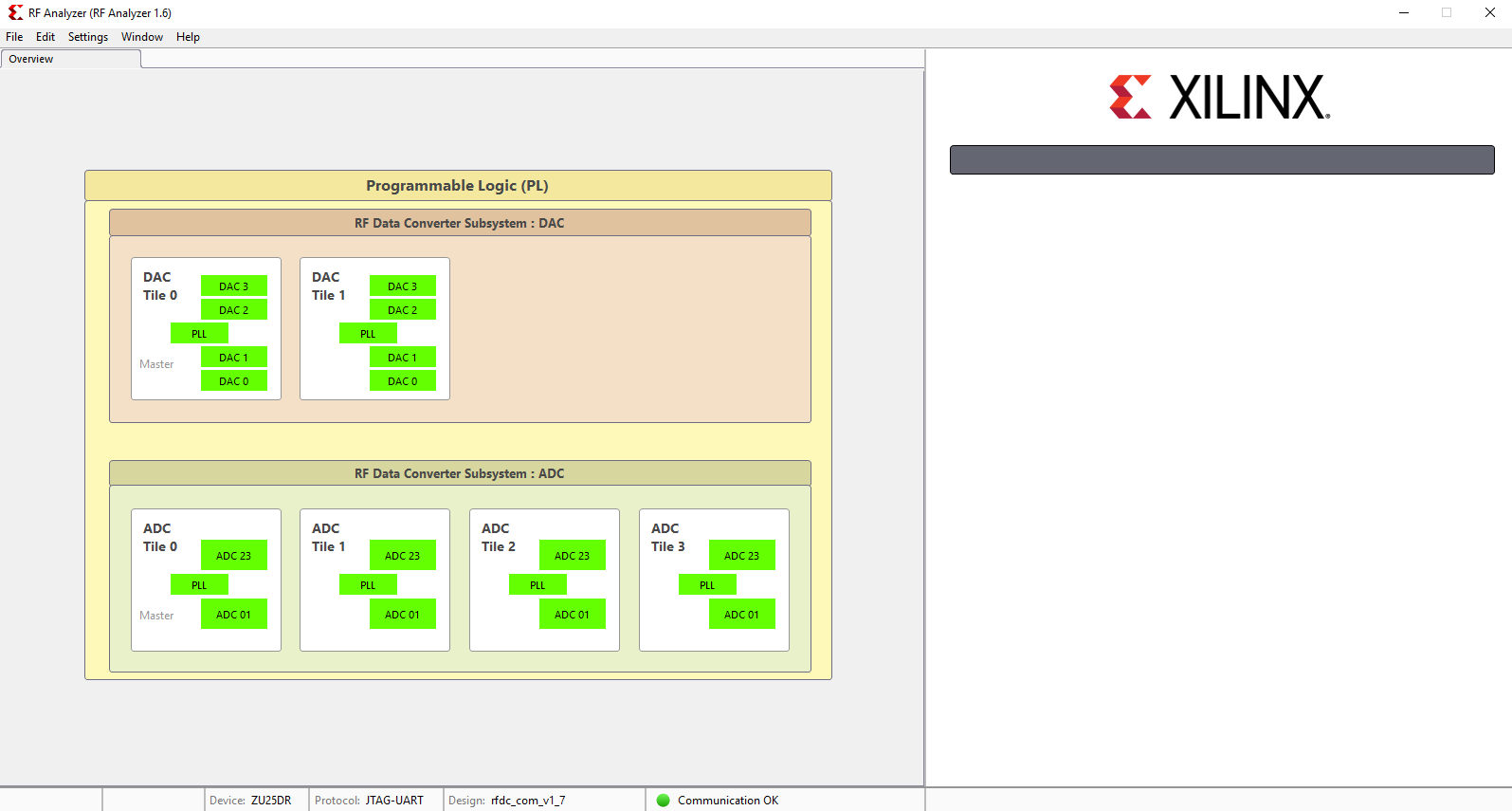

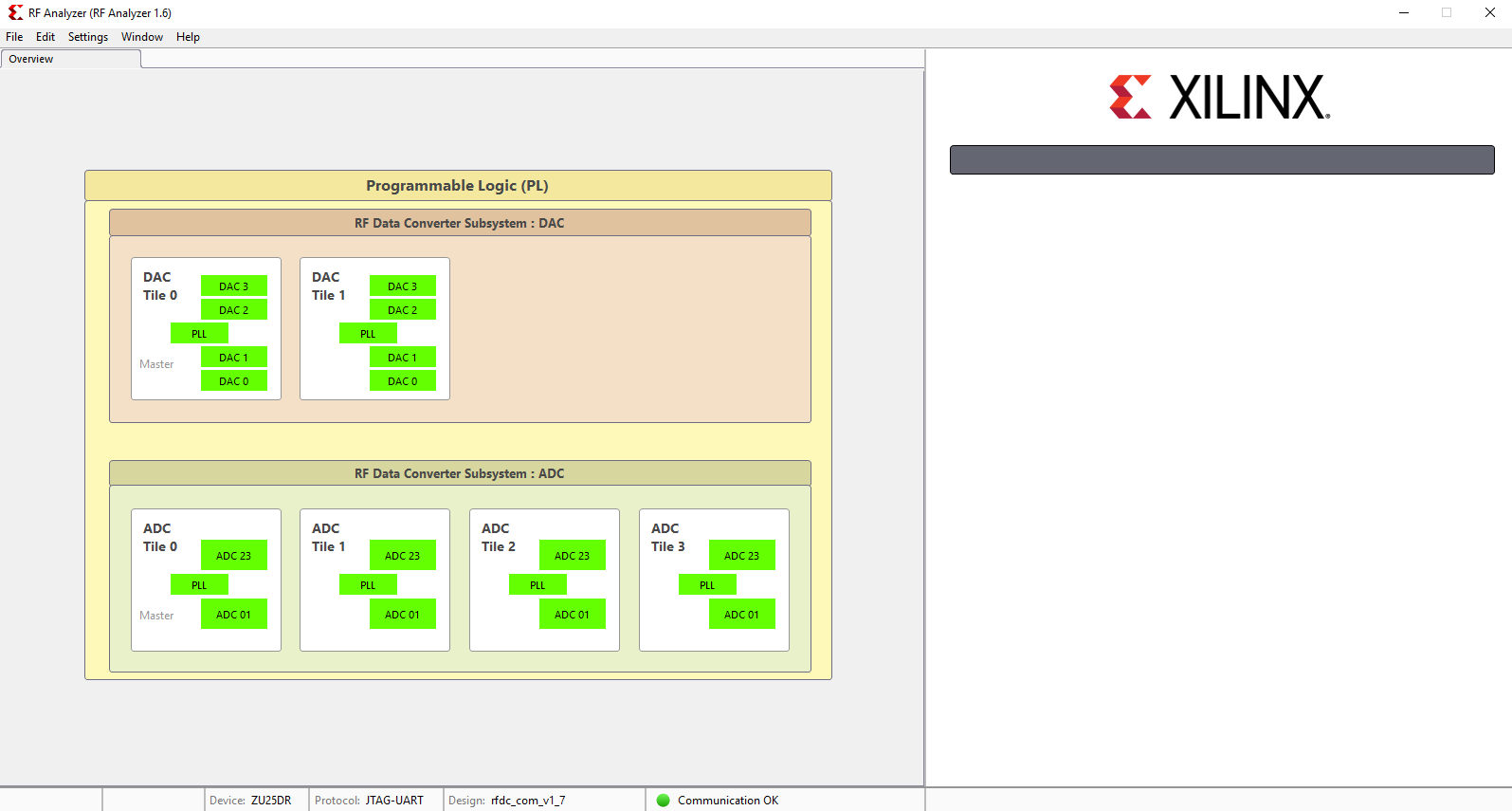

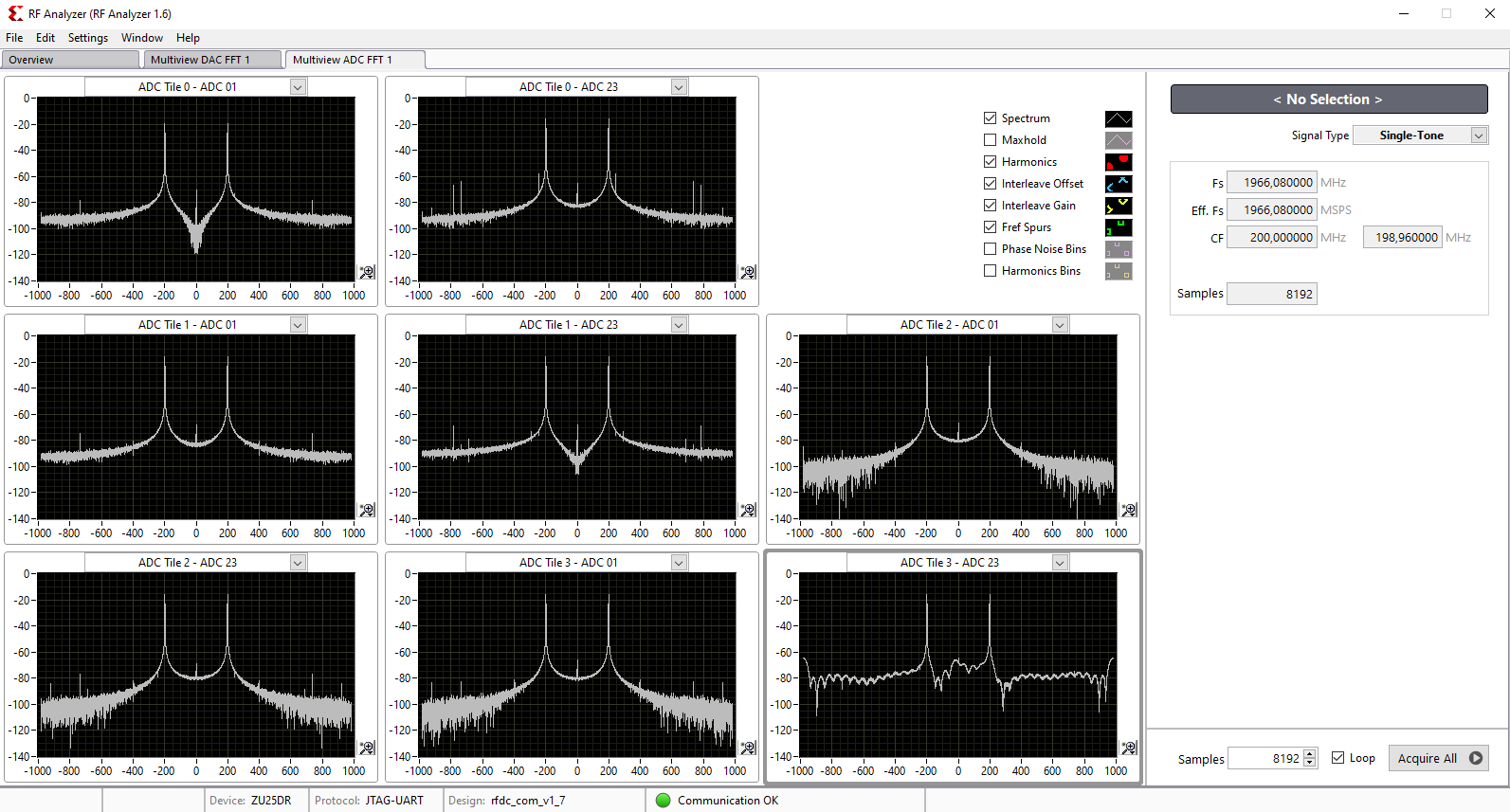

- After the initilalisation, all ADCs/DACs tiles are visible

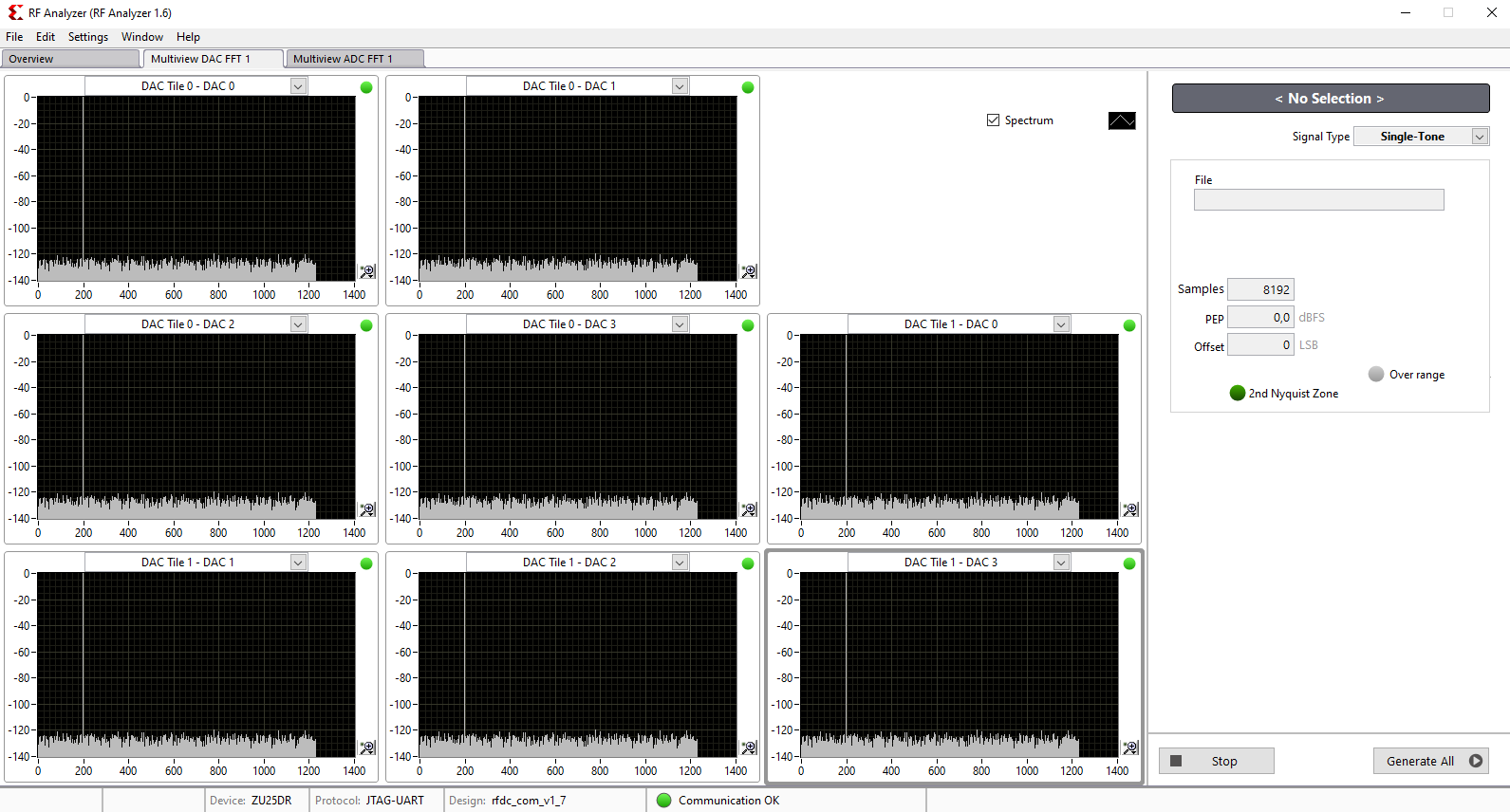

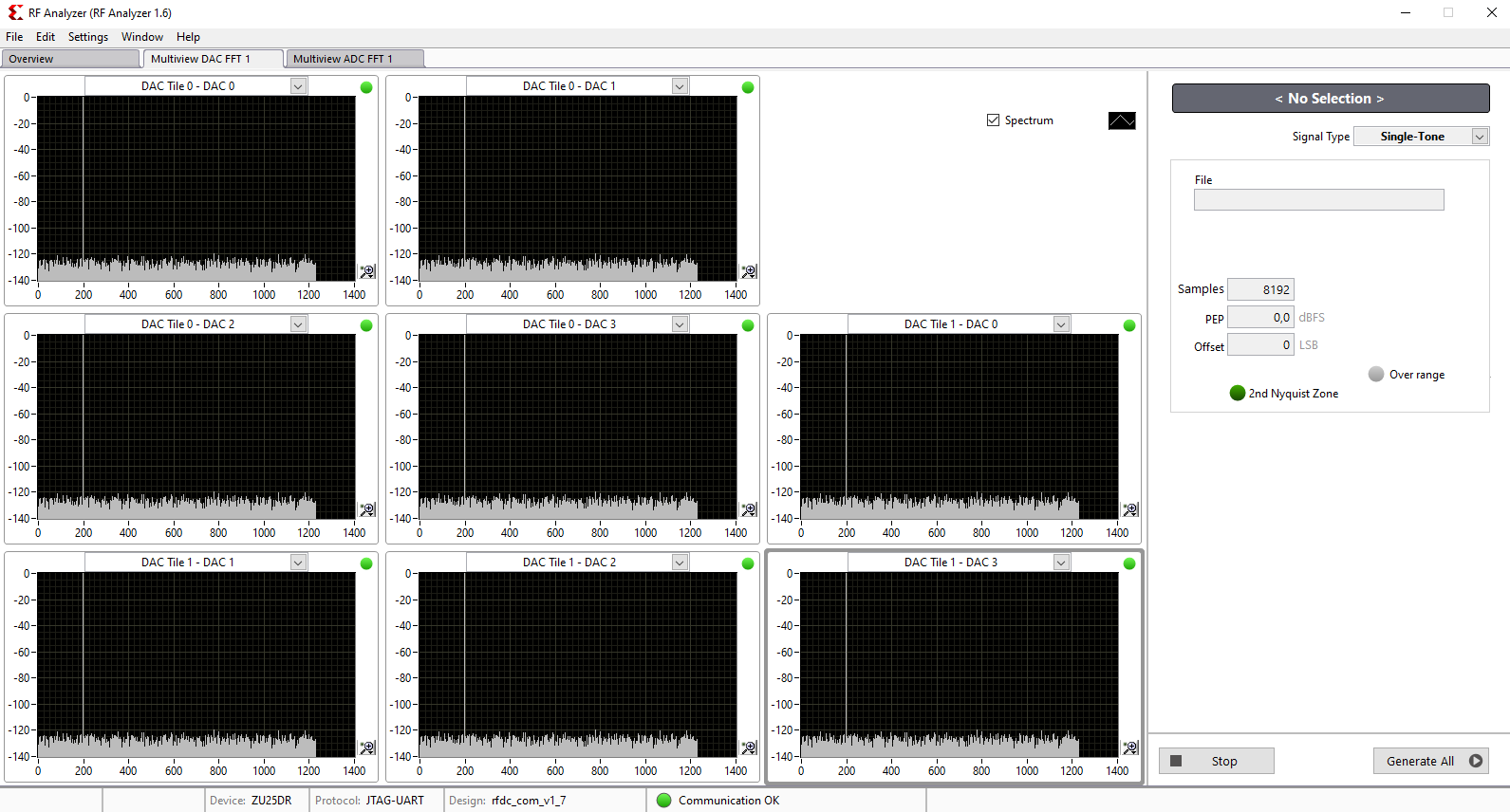

- Click on desired DAC tile and choose a DAC (for example DAC0)

- Adjust the desired DAC properties (for example output frequency)

- Click on Generate button to generate the signal in output of DAC

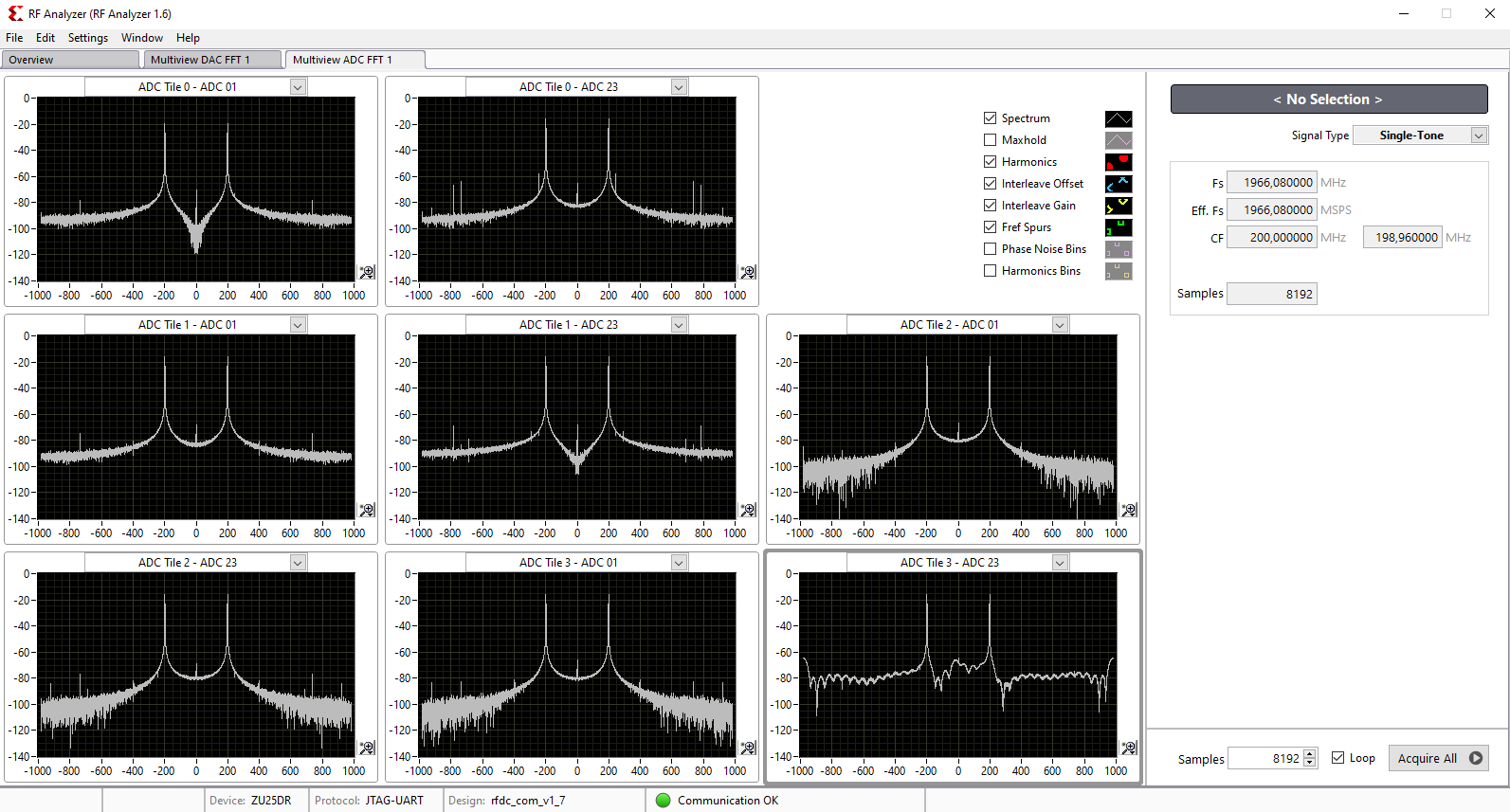

- Click on the related ADC tile and choose the related ADC (for example ADC0)

- Click on Acquire button to aqcuire the input signal

- The spectum of the DAC output signal can be seen now. The signal can be visible in time domain too.

- Tip: In menu Window click on Multiview to see all of DACs and ADCs simultaneously.

| RF Analyzer GUI | Board TE0835 ( RFSoC U1) |

| TEB0835 |

|---|

| Tile ADC /DACConverter | SoC Pin Name | SoC Pin Number | B2B | Signal Name | Connector Designator | Connector Type |

|---|

| ADC Tile 0 | -ADC 01 | ADC0_P/ADC0_N | AK2/AK1 | B2B | ADC0_P/ADC0_N | J1 | SMA |

| ADC Tile 0 | -ADC 23 | ADC1_P/ADC1_N | AH2/AH1 | B2B | ADC1_P/ADC1_N | J2 | UFL |

| ADC Tile 1 | -ADC 01 | ADC2_P/ADC2_N | AF2/AF1 | B2B | ADC2_P/ADC2_N | J3 | SMA |

| ADC Tile 1 | -ADC 23 | ADC3_P/ADC3_N | AD2/AD1 | B2B | ADC3_P/ADC3_N | J4 | UFL |

| ADC Tile 2 | -ADC 01 | ADC4_P/ADC4_N | AB2/AB1 | B2B | ADC4_P/ADC4_N | J5 | SMA |

| ADC Tile 2 | -ADC 23 | ADC5_P/ADC5_N | Y2/Y1 | B2B | ADC5_P/ADC5_N | J6 | UFL |

| ADC Tile 3 | -ADC 01 | ADC6_P/ADC6_N | V2/V1 | B2B | ADC6_P/ADC6_N | J7 | SMA |

| ADC Tile 3 | -ADC 23 | ADC7_P/ADC7_N | T2/T1 | B2B | ADC7_P/ADC7_N | J8 | UFL |

| DAC Tile 0 | -DAC 0 | DAC0_P/DAC0_N | N2/N1 | B2B | DAC0_P/DAC0_N | J9 | SMA |

| DAC Tile 0 | -DAC 1 | DAC1_P/DAC1_N | L2/L1 | B2B | DAC1_P/DAC1_N | J10 | UFL |

| DAC Tile 0 | -DAC 2 | DAC2_P/DAC2_N | J2/J1 | B2B | DAC2_P/DAC2_N | J11 | SMA |

| DAC Tile 0 | -DAC 3 | DAC3_P/DAC3_N | G2/G1 | B2B | DAC3_P/DAC3_N | J12 | UFL |

| DAC Tile 1 | -DAC 0 | DAC4_P/DAC4_N | E2/E1 | B2B | DAC4_P/DAC4_N | J13 | UFL |

| DAC Tile 1 | -DAC 1 | DAC5_P/DAC5_N | C2/C1 | B2B | DAC5_P/DAC5_N | J14 | UFL |

| DAC Tile 1 | -DAC 2 | DAC6_P/DAC6_N | B4/A4 | B2B | DAC6_P/DAC6_N | J15 | UFL |

| DAC Tile 1 | -DAC 3 | DAC7_P/DAC7_N | B6/A6 | B2B | DAC7_P/DAC7_N | J16 | UFL |

| Expand |

|---|

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title | Overview |

|---|

|

Image Modified Image Modified

|

| Scroll Title |

|---|

anchor | Figure_VHM

| Expand |

|---|

|

Image Modified Image Modified

|

| Expand |

|---|

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title | ADCs |

|---|

|

Image Modified Image Modified

|

System Design - Vivado

...

- Add Files: all TE Files start with te_*

- Si5395 on the TE0835 RFSoC module configuration

- Si5395 on the TEB0835 carrier board configuration

- ETH+OTG Reset over MIO

...