Page History

...

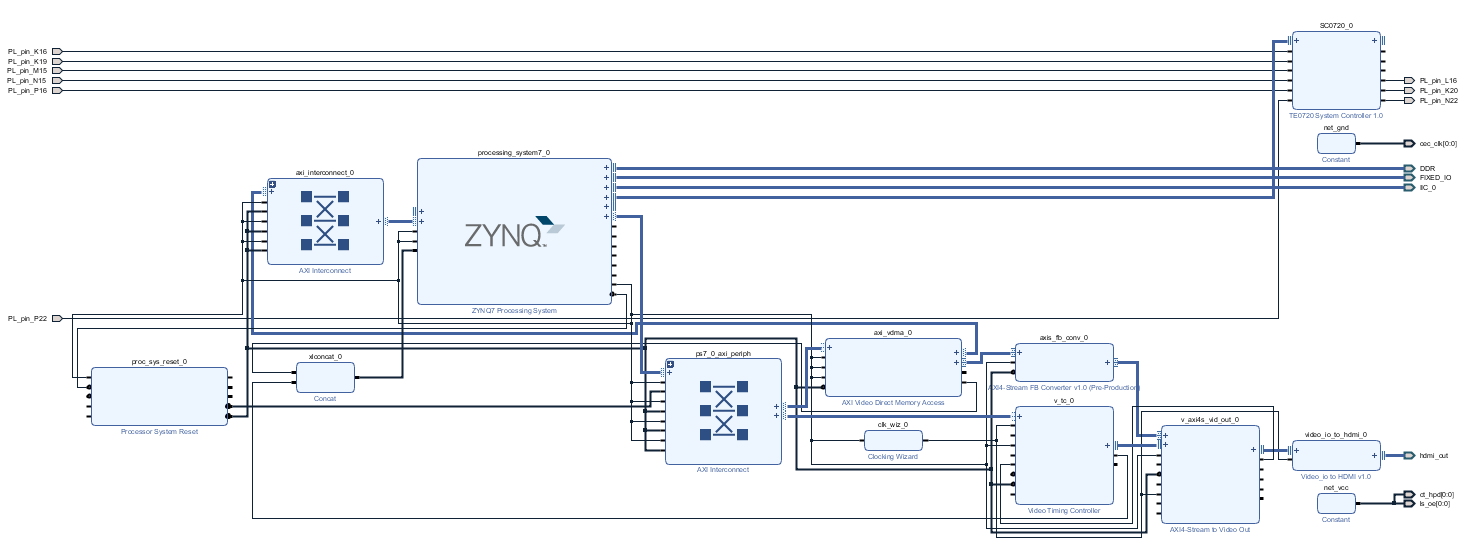

Block Design

PS Interfaces

| Type | Note |

|---|---|

| DDR | --- |

| QSPI | MIO |

| ETH0 | MIO |

| USB0 | MIO |

| SD0 | MIO |

| SD1 | MIO |

| UART0 | MIO |

| UART1 | MIO |

| I2C0 | EMIO TE0701 |

| I2C1 | EMIO TE0720 |

| GPIO | MIO |

| TTC | EMIO |

Constrains

Basic module constrains

...

| Code Block | ||||

|---|---|---|---|---|

| ||||

# # Constraints for System controller support logic # set_property PACKAGE_PIN K16 [get_ports PL_pin_K16] set_property PACKAGE_PIN K19 [get_ports PL_pin_K19] set_property PACKAGE_PIN K20 [get_ports PL_pin_K20] set_property PACKAGE_PIN L16 [get_ports PL_pin_L16] set_property PACKAGE_PIN M15 [get_ports PL_pin_M15] set_property PACKAGE_PIN N15 [get_ports PL_pin_N15] set_property PACKAGE_PIN N22 [get_ports PL_pin_N22] set_property PACKAGE_PIN P16 [get_ports PL_pin_P16] set_property PACKAGE_PIN P22 [get_ports PL_pin_P22] # # If Bank 34 is not 3.3V Powered need change the IOSTANDARD # set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_P22] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_P16] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_N22] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_N15] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_M15] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_L16] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_K20] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_K19] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_K16] # # TE0701 I2C Bus # set_property PACKAGE_PIN W20 [get_ports iic_0_scl_io] set_property PACKAGE_PIN W21 [get_ports iic_0_sda_io] set_property IOSTANDARD LVCMOS25 [get_ports iic_0_scl_io] set_property IOSTANDARD LVCMOS25 [get_ports iic_0_sda_io] # # ADV7511 Interface # set_property PACKAGE_PIN N20 [get_ports hdmi_out_clk] set_property PACKAGE_PIN N19 [get_ports hdmi_out_de] set_property PACKAGE_PIN R19 [get_ports hdmi_out_hsync] set_property PACKAGE_PIN T19 [get_ports hdmi_out_vsync] set_property PACKAGE_PIN T18 [get_ports {hdmi_out_data[0]}] set_property PACKAGE_PIN R18 [get_ports {hdmi_out_data[1]}] set_property PACKAGE_PIN R21 [get_ports {hdmi_out_data[2]}] set_property PACKAGE_PIN R20 [get_ports {hdmi_out_data[3]}] set_property PACKAGE_PIN M22 [get_ports {hdmi_out_data[4]}] set_property PACKAGE_PIN K21 [get_ports {hdmi_out_data[5]}] set_property PACKAGE_PIN M21 [get_ports {hdmi_out_data[6]}] set_property PACKAGE_PIN J20 [get_ports {hdmi_out_data[7]}] set_property PACKAGE_PIN T17 [get_ports {hdmi_out_data[8]}] set_property PACKAGE_PIN J22 [get_ports {hdmi_out_data[9]}] set_property PACKAGE_PIN T16 [get_ports {hdmi_out_data[10]}] set_property PACKAGE_PIN J21 [get_ports {hdmi_out_data[11]}] set_property IOSTANDARD LVCMOS25 [get_ports hdmi_*] set_property PACKAGE_PIN AB16 [get_ports {cec_clk[0]}] set_property PACKAGE_PIN AB17 [get_ports {ct_hpd[0]}] set_property PACKAGE_PIN AA16 [get_ports {ls_oe[0]}] set_property IOSTANDARD LVCMOS25 [get_ports {cec_clk[0]}] set_property IOSTANDARD LVCMOS25 [get_ports {ct_hpd[0]}] set_property IOSTANDARD LVCMOS25 [get_ports {ls_oe[0]}] |

Software Design - SDK/HSI

...

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

/ {

memory { // Reduce linux memory for framebuffers to place framebuffer in high part

device_type = "memory";

reg = <0x0 0x3FC00000>; // Modify it depending on board memory size

};

framebuffer0: framebuffer@0x3FC00000 { // HDMI out

compatible = "simple-framebuffer";

reg = <0x3FC00000 (1280 * 720 * 4)>; // 720p Modify it depending on board memory size

width = <1280>; // 720p

height = <720>; // 720p

stride = <(1280 * 4)>; // 720p

format = "a8b8g8r8";

};

};

/* Disable standard VDMA driver to prevent core reset on linux start */

&axi_vdma_0 {

status = "disabled";

};

/* Disable timing controller deriverdriver */

&v_tc_0 {

status = "disabled";

};

/* Flash */

&qspi {

flash0: flash@0 {

compatible = "w25q256";

};

};

/* ETH PHY */

&gem0 {

phy-handle = <&phy0>;

mdio {

#address-cells = <1>;

#size-cells = <0>;

phy0: phy@0 {

compatible = "marvell,88e1510";

device_type = "ethernet-phy";

reg = <0>;

};

};

};

/* USB PHY */

/{

usb_phy0: usb_phy@0 {

compatible = "ulpi-phy";

//compatible = "usb-nop-xceiv";

#phy-cells = <0>;

reg = <0xe0002000 0x1000>;

view-port = <0x0170>;

drv-vbus;

};

};

&usb0 {

dr_mode = "host";

//dr_mode = "peripheral";

usb-phy = <&usb_phy0>;

};

/* I2C need I2C1 connected to te0720 system controller ip */

&i2c1 {

iexp@20 { // GPIO in CPLD

#gpio-cells = <2>;

compatible = "ti,pcf8574";

reg = <0x20>;

gpio-controller;

};

iexp@21 { // GPIO in CPLD

#gpio-cells = <2>;

compatible = "ti,pcf8574";

reg = <0x21>;

gpio-controller;

};

rtc@6F { // Real Time Clock

compatible = "isl12022";

reg = <0x6F>;

};

};

|

...

Overview

Content Tools