Page History

...

| Excerpt |

|---|

|

Revision History

| HTML |

|---|

<!-- - Add changes from design - Export PDF to download, if vivado revision is changed! --> |

...

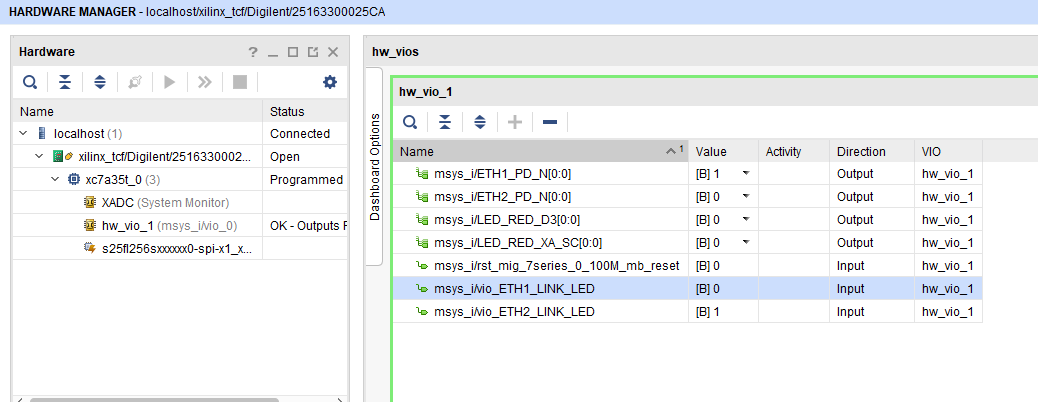

- Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder).

- todo user LED

- User LED Control

- ETH Control and Link Status

- MicroBlaze Reset Status

- todo user LED

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

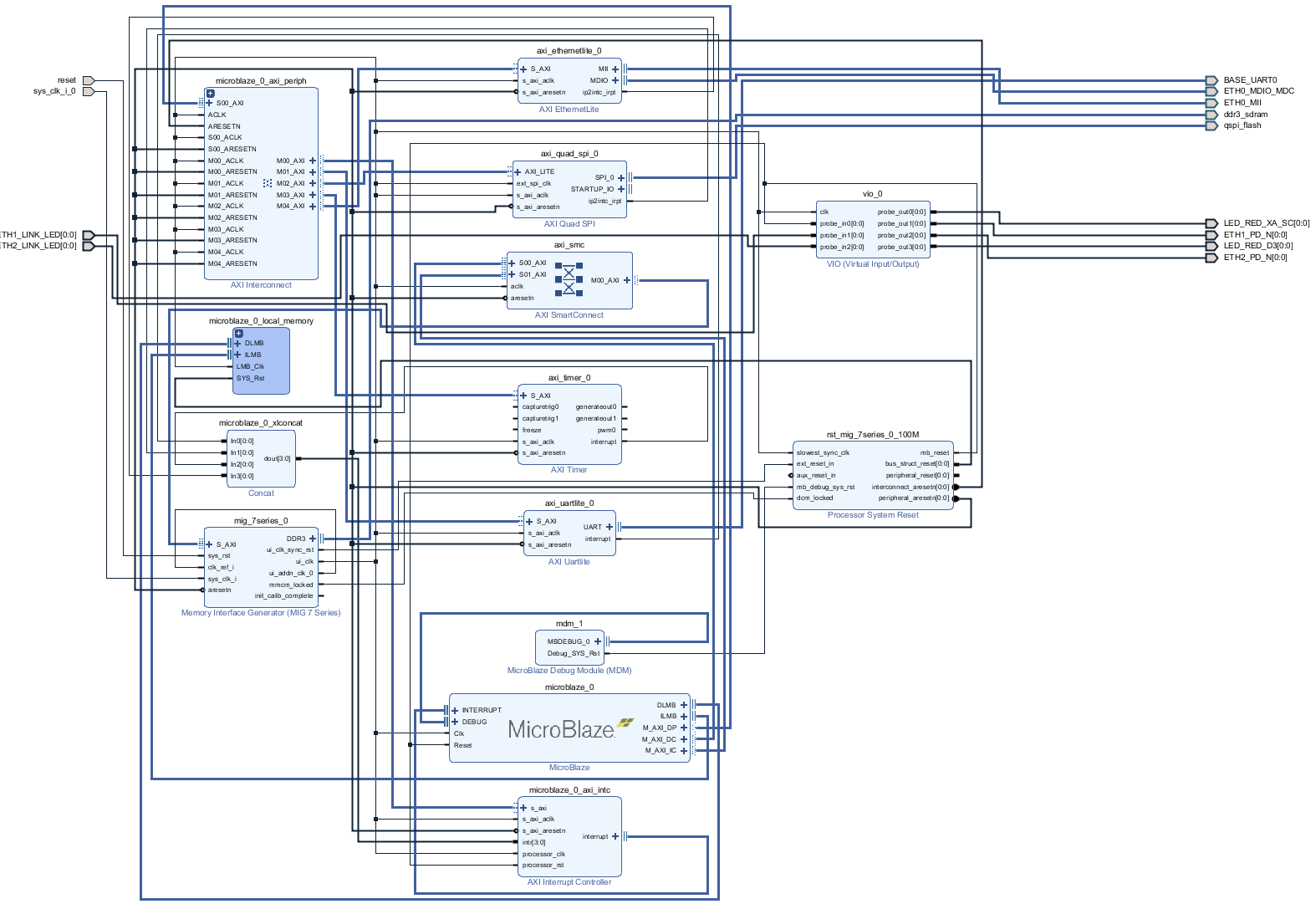

Block Design

to Bild

Constrains

Basic module constrains

...

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

todo |

Software Design - SDK/HSI

| HTML |

|---|

<!--

optional chapter

separate sections for different apps

--> |

For SDK project creation, follow instructions from:

Application

SREC SPI BootLoader

Add some Console outputs and changed Bootloader Read Address.

Template location: \sw_lib\sw_apps\srec_spi_bootloader

set_property PACKAGE_PIN G3 [get_ports {LED_RED_XA_SC[0]}]

set_property IOSTANDARD LVCMOS15 [get_ports {LED_RED_XA_SC[0]}]

set_property PACKAGE_PIN T10 [get_ports {ETH2_LINK_LED[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ETH2_LINK_LED[0]}]

set_property PACKAGE_PIN V15 [get_ports {ETH1_LINK_LED[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ETH1_LINK_LED[0]}]

set_property PACKAGE_PIN T18 [get_ports {ETH1_PD_N[0]}]

set_property PACKAGE_PIN D10 [get_ports {ETH2_PD_N[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ETH2_PD_N[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ETH1_PD_N[0]}]

set_property PACKAGE_PIN L15 [get_ports {LED_RED_D3[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_RED_D3[0]}] |

Software Design - SDK/HSI

| HTML |

|---|

<!--

optional chapter

separate sections for different apps

--> |

For SDK project creation, follow instructions from:

Application

SREC SPI BootLoader

Add some Console outputs and changed Bootloader Read Address.

Template location: \sw_lib\sw_apps\srec_spi_bootloader

xilisf_v5_xilisf_v5_9

Changed default Flash Typ to 5.

...

- Set kernel flash Address to 0x900000 and Kernel size to 0xA00000:

(--> Subsystem Auto Hardware Settings --> Flash Settings)Flash Settings)- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART0_SIZE = 0x400000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART1_SIZE = 0x4E0000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART0PART2_SIZE = 0x400000 0x20000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART1_SIZE = 0x4E0000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART2_SIZE = 0x20000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART3_SIZE = 0xA00000

U-Boot

- _PART3_SIZE = 0xA00000

U-Boot

| Code Block | ||

|---|---|---|

| ||

#include <configs/platform-auto.h>

#define CONFIG_SYS_BOOTM_LEN 0xF000000

#undef CONFIG_PHY_XILINX

#undef XILINX_EMACLITE_BASEADDR 0x40E00000

#undef CONFIG_MII

#undef CONFIG_PHY_GIGE

#undef CONFIG_PHY_MARVELL

#undef CONFIG_PHY_NATSEMI

#undef CONFIG_NET_MULTI

#undef CONFIG_BOOTP_MAY_FAIL

#undef CONFIG_NETCONSOLE 1

#undef CONFIG_SERVERIP 192.168.150.117

#undef CONFIG_IPADDR

/* PREBOOT */

#define CONFIG_PREBOOT "echo U-BOOT for petalinux;setenv preboot; echo; " | ||

| Code Block | ||

| ||

todo

|

Device Tree

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

/* ETH PHY */

&axi_ethernetlite_0 {

phy-handle = <&phy0>;

mdio {

#address-cells = <1>;

#size-cells = <0>;

phy0: phy@0 {

device_type = "ethernet-phy";

reg = <1>;

};

};

};

|

...

Overview

Content Tools