Page History

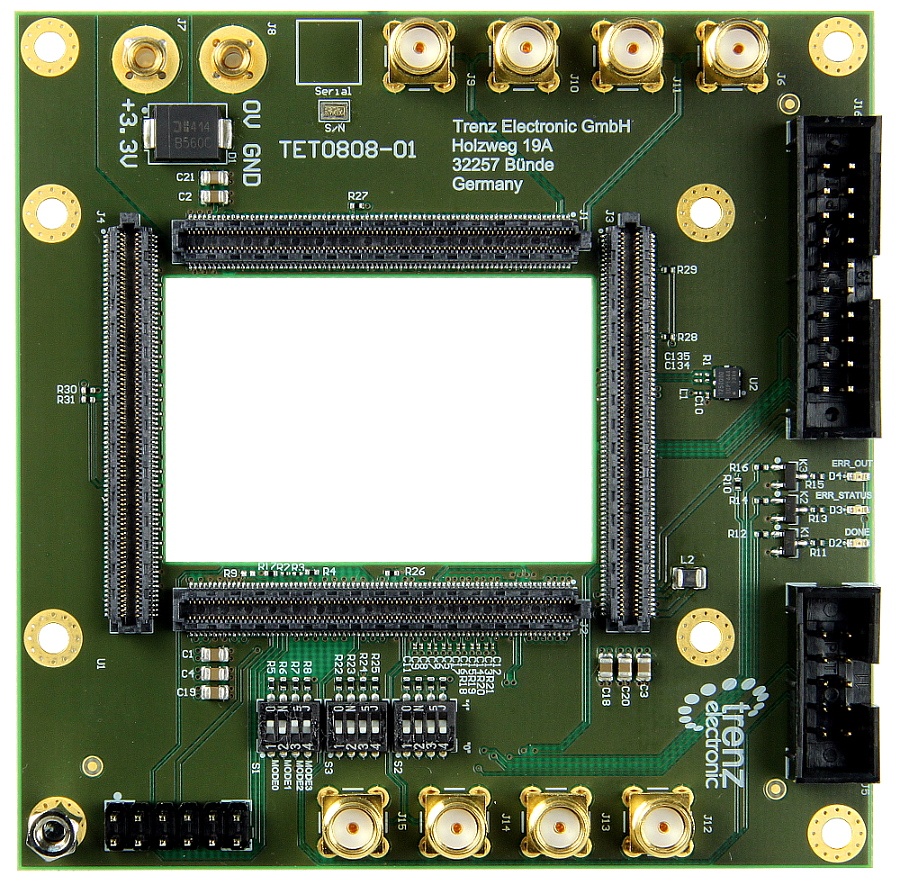

Features

- Single 3.3V input

- Header for TE0790 JTAG/UART Adapter

- 20 PIn ARM JTAG header (connected to MIO JTAG 0)

- 10 Pin I2C header for Silabs Clock Builder Field Programmer

- Done, Error/Status LEDs

- One PL GT with SMA connectors

- One PS GT with SMA connectors

- GT local loopback

- PL I/O loopbacks

- PS I/O loopbacks

- Boot Mode switches

- Power control switches to control TE0808 power domains

...

| Item | Name | Vendor | Separate Order | Comments | |||

|---|---|---|---|---|---|---|---|

| 1 | TE0808 or TE803TE0803 | Trenz | TE0808, TE0803 | ||||

| 3 | TE0790 USB JTAG/UART Adapter | Trenz | TE0790 | ||||

| 4 | SMA Cable (50 cm long), 4 pcs | ||||||

| 5 | mini USB Cable | ||||||

| 6 | Cables for power (2mm Banana Connector), 2 pcs | ||||||

| 7 | ClockBuilder Pro Programmer | SiLabs | digikey / mouser |

| Note |

|---|

NOTE: Kit Content may be different, depending on customer agreements. Positions 1 to 3 are always included. |

...

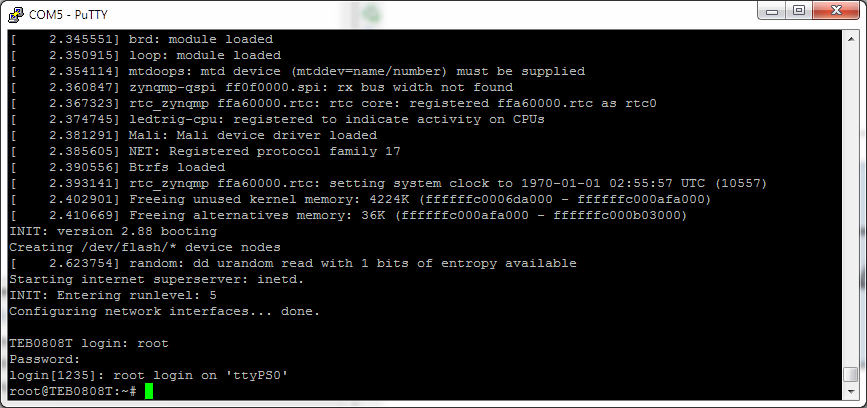

To restart the boot process press the small push-button on TE0790, it is wired to TE0808 Reset.

Manual test

TesKit808, mini-USB cable not connected, 3.3V power applied.

| TE0790 SW | TE0808 RLED | TE0790 GLED | TE0790 RLED | DONE | ERR |

|---|---|---|---|---|---|

| Pressed | OFF | ON | ON | OFF | OFF |

| Released | OFF | ON | ON | ON | ON |

...

Function Description

GT transceiver have either internal connection or loopbacks or are connected to SMA Connectors. Note that connections to SMA are not AC Coupled!

...

PL I/O has on-board internal loopback an all pins for connectivity testing.

UART

UART is available on MIO68, MIO69 via the supplied TE0790 USB Module. TE0808 and TE0803 board parts do not support this settings. They must be changed manually.

...

| M3 | M2 | M1 | M0 | Bootmode Hex | Bootmode | Notes |

|---|---|---|---|---|---|---|

| ON | ON | ON | ON | 0x0 | PS Main JTAG (TE0790 USB JTAG) | Needed for SPI Flash Programming |

| ON | ON | OFF | ON | 0x2 | SPI Flash (dual parallel, 4bit x 2, 32bit Addressing) | Default |

...

SPI Flash Programming

Flash programming is supported from SDK GUI, fsbl.elf that is needed is provided in common download area.

...

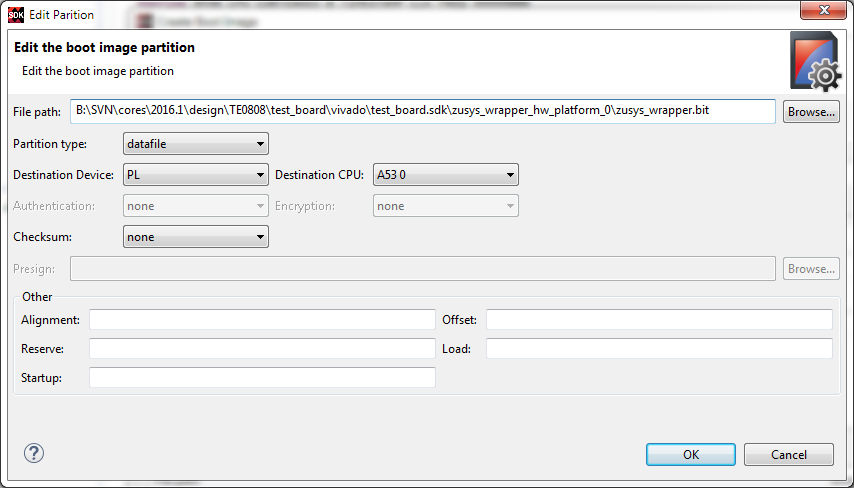

This works out of the box with Vivado/SDK 2016.1, if you only have EVAL license for ZU+ then it is necessary to export HDF without bitstream.

| Note |

|---|

| NOTE: 2016.1 Bootgen seems to have small bug, automatically generated BIF file has bitstream partition set to PS as destination device what results in BOOT.BIN that does not load correctly. Make sure it is set to PL. This problem has been fixed in 2016.2 |

...

| Note |

|---|

Important: BL31.ELF is needed or Linux would fail with kernel panic. PMU Fimware is not absolutely necessary, without it there would be warnings during Linux boot. |

Note: if there are no network drivers installed, then linux boot does stop on "Configuring network interfaces..." as workaround special "disable network" application can be installed into petalinux to allow booting with no network.

...

If Si5345 is not programmed then there is only 1 GT Clock available, from 125MHz oscillator on TEBT0808, it does clock B228 CLK0 input, with this clock up to 12 GT can be tested, including the GT that has SMA connectors.

IBERT with external Loopback on QUAD228, using 125MHz LVDS clock from TEBT0808 base.

...

Setup for Si5345 PLL Programming using SiLabs ClockBuilder Pro Field Programmer.

References

...

- Silabs ClockBuilder Pro Field Programmer

- TEBT0808 Documentation

- TE0808 Documentation

- Xilinx Zynq UltraScale MPSoC Base TRD

Document Change History

| Date | Revision | Contributors | Description |

|---|---|---|---|

| 2017-06-07 | John Hartfiel | Initial version. |

Disclaimer

| Include Page | ||||

|---|---|---|---|---|

|