Page History

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2ß18-07-11 | 2018.4 | TE0808-StarterKit_noprebuilt-vivado_2018.2-build_02_20180711091558.zip TE0808-StarterKit-vivado_2018.2-build_02_20180711091049.zip | John Hartfiel |

|

| 2018-05-24 | 2017.4 | TE0808-StarterKit_noprebuilt-vivado_2017.4-build_10_20180524091231.zip TE0808-StarterKit-vivado_2017.4-build_10_20180524091208.zip | John Hartfiel |

|

| 2018-03-29 | 2017.4 | TE0808-StarterKit_noprebuilt-vivado_2017.4-build_07_20180329145308.zip TE0808-StarterKit-vivado_2017.4-build_07_20180329145246.zip | John Hartfiel |

|

| 2018-02-06 | 2017.4 | TE0808-StarterKit_noprebuilt-vivado_2017.4-build_05_20180206082740.zip TE0808-StarterKit-vivado_2017.4-build_05_20180206082722.zip | John Hartfiel |

|

| 2018-02-05 | 2017.4 | TE0808-StarterKit_noprebuilt-vivado_2017.4-build_05_20180205083231.zip TE0808-StarterKit-vivado_2017.4-build_05_20180205083208.zip | John Hartfiel |

|

| 2018-01-17 | 2017.4 | TE0808-StarterKit-vivado_2017.4-build_05_20180117094213.zip TE0808-StarterKit_noprebuilt-vivado_2017.4-build_05_20180117094231.zip | John Hartfiel |

|

| 2018-01-15 | 2017.4 | TE0808-StarterKit-vivado_2017.4-build_03_20180115092306.zip | John Hartfiel |

|

| 2017-12-18 | 2017.2 | TE0808-StarterKit_noprebuilt-vivado_2017.2-build_07_20171219151749.zip TE0808-StarterKit-vivado_2017.2-build_07_20171219151728.zip | John Hartfiel |

|

...

| Software | Version | Note |

|---|---|---|

| Vivado | 20172018.42 | needed |

| SDK | 20172018.42 | needed |

| PetaLinux | 20172018.42 | needed |

Hardware

| HTML |

|---|

<!-- Hardware Support --> |

...

Reference Design is available on:

Design Flow

| HTML |

|---|

<!-- Basic Design Steps Add/ Remove project specific --> |

...

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0808" possible - Copy image.ub on Copy image.ub on SD-Card

- Insert SD-Card

SD

- Copy image.ub and Boot.bin on SD-Card.

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to SD-Boot.

- Insert SD-Card in SD-Slot.

...

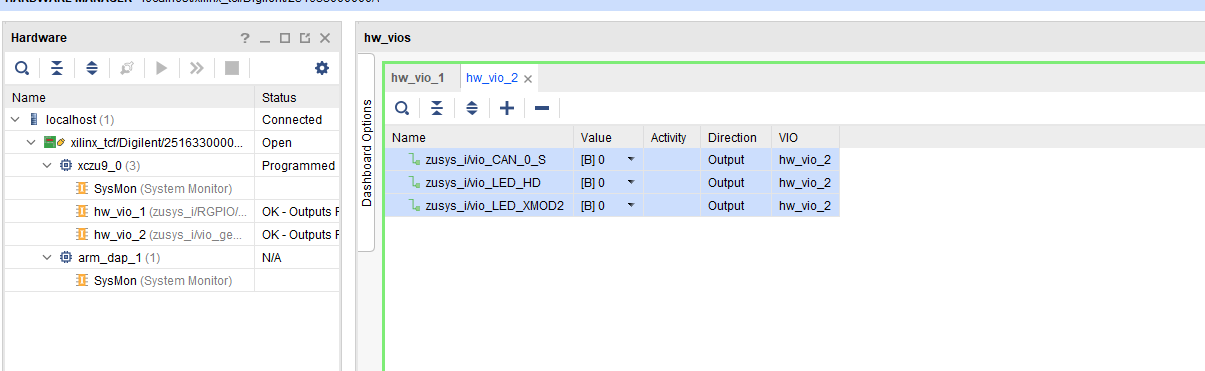

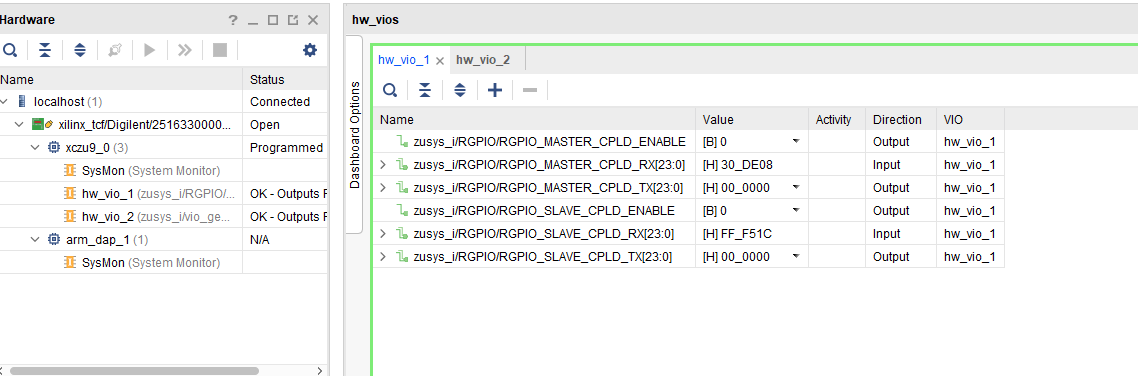

Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder).

RGPIO Interface:

- Set Bit 31-28 to "1010" to activat RGPIO Interface of Master or Slave CPLD.Enable to send Write date over RGPIO interface.

- Important, see description to set correct values

- Description: TEBF0808 Master CPLD#RGPIO, TEBF0808 Slave CPLD#RGPIO

- Set Bit 31-28 to "1010" to activat RGPIO Interface of Master or Slave CPLD.Enable to send Write date over RGPIO interface.

- LED Control +CAN_S:

- XMOD 2(without green dot) and HD LED are accessible.

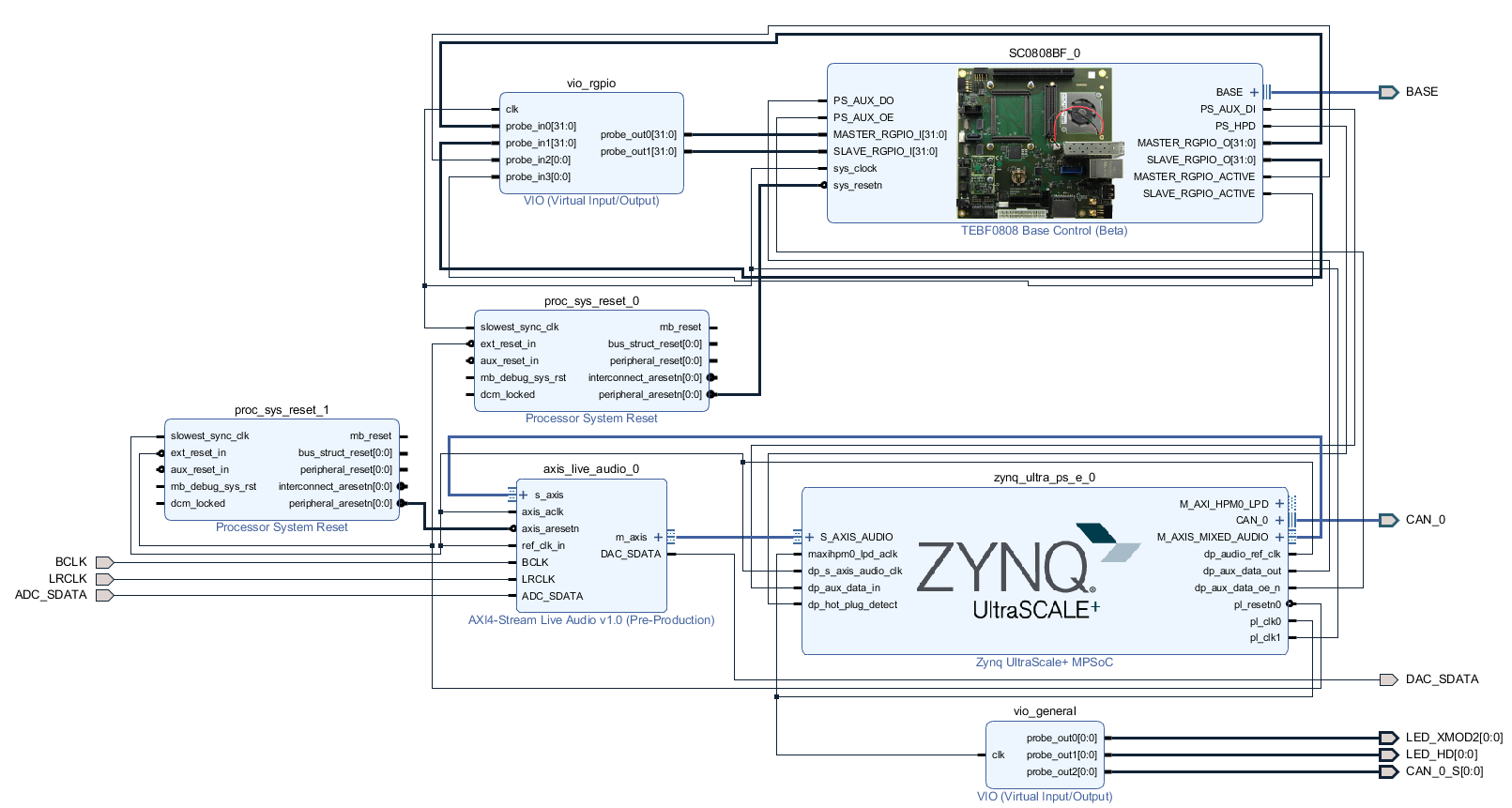

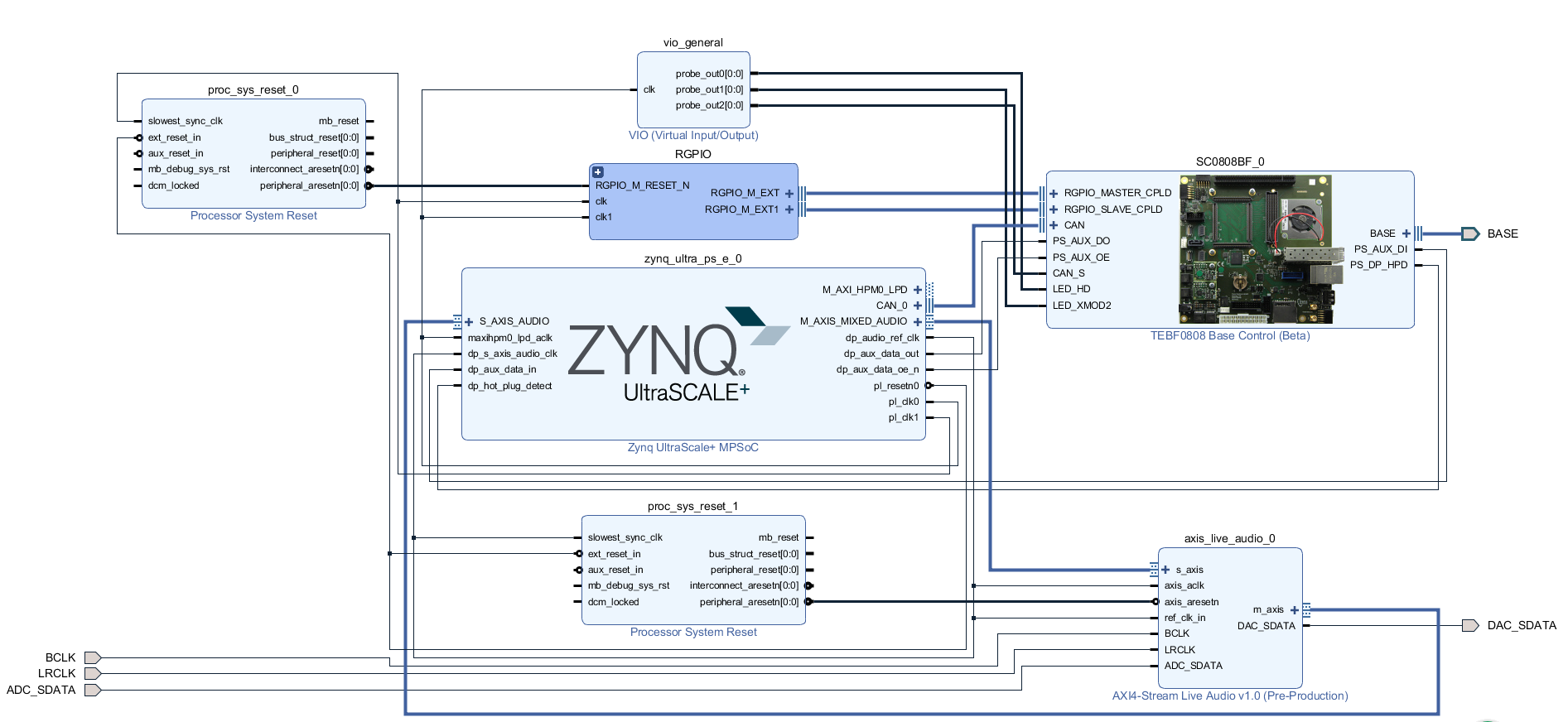

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

Block Design

PS Interfaces

Activated interfaces:

...

| Code Block | ||||

|---|---|---|---|---|

| ||||

#System Controller IP #LED_HD SC0 J3:31 set_property PACKAGE_PIN J14 [get_ports {LED_HD[0]}] set_property IOSTANDARD LVCMOS18 [get_ports {LED_HD[0]}] #LED_XMOD SC17 J3:48 #LED_XMOD SC17 J3:48 #CAN RX SC19 J3:52 B47_L2_P in #CAN TX SC18 J3:50 B47_L2_N out #CAN S SC16 J3:46 B47_L3_N out set_property PACKAGE_PIN B13J14 [get_ports {LED_XMOD2[0]}BASE_sc0] set_property IOSTANDARDPACKAGE_PIN LVCMOS18G13 [get_ports {LED_XMOD2[0]}] #System Controller IPBASE_sc5] set_property PACKAGE_PIN J15 [get_ports BASE_sc6] set_property PACKAGE_PIN K15 [get_ports BASE_sc7] set_property PACKAGE_PIN A15 [get_ports BASE_sc10_io] set_property PACKAGE_PIN B15 [get_ports BASE_sc11] set_property PACKAGE_PIN C13 [get_ports BASE_sc12] set_property PACKAGE_PIN C14 [get_ports BASE_sc13] set_property PACKAGE_PIN E13 [get_ports BASE_sc14] set_property PACKAGE_PIN E14 [get_ports BASE_sc15] set_property PACKAGE_PIN A13 [get_ports BASE_sc16] set_property PACKAGE_PIN G13B13 [get_ports BASE_sc5sc17] set_property PACKAGE_PIN J15A14 [get_ports BASE_sc6sc18] set_property PACKAGE_PIN K15 B14 [get_ports BASE_sc19] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc7sc0] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc5] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc6] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc7] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc10_io] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc11] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc12] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc13] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc14] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc15] # PLL #set_property set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc16] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc17] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc18] set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc19] # PLL #set_property PACKAGE_PIN AH6 [get_ports {si570_clk_p[0]}] #set_property IOSTANDARD LVDS [get_ports {si570_clk_p[0]}] #set_property IOSTANDARD LVDS [get_ports {si570_clk_n[0]}] # Clocks #set_property PACKAGE_PIN J8 [get_ports {B229_CLK1_clk_p[0]}] #set_property PACKAGE_PIN F25 [get_ports {B128_CLK0_clk_p[0]}] # SFP #set_property PACKAGE_PIN G8 [get_ports {B230_CLK0_clk_p}] # B230_RX3_P #set_property PACKAGE_PIN A4 [get_ports {SFP1_rxp}] # B230_TX3_P #set_property PACKAGE_PIN A8 [get_ports {SFP1_txp}] # B230_RX2_P #set_property PACKAGE_PIN B2 [get_ports {SFP2_rxp}] # B230_TX2_P #set_property PACKAGE_PIN B6 [get_ports {SFP2_txp}] # Audio Codec #LRCLK J3:49 B47_L9_N #BCLK J3:51 B47_L9_P #DAC_SDATA J3:53 B47_L7_N #ADC_SDATA J3:55 B47_L7_P set_property PACKAGE_PIN G14 [get_ports LRCLK ] set_property PACKAGE_PIN G15 [get_ports BCLK ] set_property PACKAGE_PIN E15 [get_ports DAC_SDATA ] set_property PACKAGE_PIN F15 [get_ports ADC_SDATA ] set_property IOSTANDARD LVCMOS18 [get_ports LRCLK ] set_property IOSTANDARD LVCMOS18 [get_ports BCLK ] set_property IOSTANDARD LVCMOS18 [get_ports DAC_SDATA ] set_property IOSTANDARD LVCMOS18 [get_ports ADC_SDATA ] # CAN #CAN RX SC19 J3:52 B47_L2_P #CAN TX SC18 J3:50 B47_L2_N #CAN S SC16 J3:46 B47_L3_N set_property PACKAGE_PIN A13 [get_ports CAN_0_S ] set_property IOSTANDARD LVCMOS18 [get_ports CAN_0_S ] set_property PACKAGE_PIN B14 [get_ports CAN_0_rx ] set_property IOSTANDARD LVCMOS18 [get_ports CAN_0_rx ] set_property PACKAGE_PIN A14 [get_ports CAN_0_tx ] set_property IOSTANDARD LVCMOS18 [get_ports CAN_0_tx ] |

Software Design - SDK/HSI

| HTML |

|---|

<!--

optional chapter

separate sections for different apps

--> |

For SDK project creation, follow instructions from:

Application

FSBL

TE modified 2017.4 FSBL

Changes:

- Si5345Configuration, PCIe Reset over GPIO see xfsbl_board.c and xfsbl_board.h

- Add Si5345-Registers.h, si5345.c, si5345.h

zynqmp_fsbl_flash

TE modified 2017.4 FSBL

Changes:

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

PMU

Xilinx default PMU firmware.

Hello TE0808

Hello TE0808 is a Xilinx Hello World example as endless loop instead of one console output.

U-Boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

Software Design - PetaLinux

| HTML |

|---|

<!--

optional chapter

Add "No changes." or "Activate: List"

--> |

For PetaLinux installation and project creation, follow instructions from:

Config

No changes.

U-Boot

- Change platform-top.h

Software Design - SDK/HSI

| HTML |

|---|

<!--

optional chapter

separate sections for different apps

--> |

For SDK project creation, follow instructions from:

Application

SDK template in ./sw_lib/sw_apps/ available.

zynqmp_fsbl

TE modified 2017.4 FSBL

Changes:

- Si5345Configuration, PCIe Reset over GPIO

- see xfsbl_board.c and xfsbl_board.h, xfsbl_main.c

- Add Si5345-Registers.h, si5345.c, si5345.h

Note: Remove compiler flags "-Os -flto -ffat-lto-objects" on 2018.2 SDK to generate FSBL

zynqmp_fsbl_flash

TE modified 2017.4 FSBL

Changes:

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

Note: Remove compiler flags "-Os -flto -ffat-lto-objects" on 2018.2 SDK to generate FSBL

zynqmp_pmufw

Xilinx default PMU firmware.

Hello TE0808

Hello TE0808 is a Xilinx Hello World example as endless loop instead of one console output.

U-Boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

Software Design - PetaLinux

| HTML |

|---|

<!--

optional chapter

Add "No changes." or "Activate: List"

--> |

For PetaLinux installation and project creation, follow instructions from:

Config

Activate:

- SUBSYSTEM_PRIMARY_SD_PSU_SD_1_SELECT

U-Boot

- Change platform-top.h

| Code Block | ||

|---|---|---|

| ||

#include <configs/platform-auto.h>

#define CONFIG_SYS_BOOTM_LEN 0xF000000

#define DFU_ALT_INFO_RAM \

"dfu_ram_info=" \

"setenv dfu_alt_info " \

"image.ub ram $netstart 0x1e00000\0" \

"dfu_ram=run dfu_ram_info && dfu 0 ram 0\0" \

"thor_ram=run dfu_ram_info && thordown 0 ram 0\0" | ||

| Code Block | ||

| ||

#include <configs/platform-auto.h> #define CONFIG_SYS_BOOTM_LEN 0xF000000 #define DFU_ALT_INFO_RAMMMC \ "dfu_rammmc_info=" \ "setenvset dfu_alt_info " \ "image.ub ram $netstart 0x1e00000\0${kernel_image} fat 0 1\\\\;" \ "dfu_rammmc=run dfu_rammmc_info && dfu 0 ram 0\0" \ "thor_ram=run dfu_ram_info && thordown 0 ram 0\0" #define DFU_ALT_INFO \ mmc 0\0" \ "thor_mmc=run dfu_mmc_info && thordown 0 DFU_ALT_INFO_RAMmmc 0\0" /*Required for uartless designs */ #ifndef CONFIG_BAUDRATE #define CONFIG_BAUDRATE 115200 #ifdef CONFIG_DEBUG_UART #undef CONFIG_DEBUG_UART #endif #endif /*select sd instead of mmc for autoboot */ Define CONFIG_ZYNQMP_EEPROM here and its necessaries in u-boot menuconfig if you had EEPROM memory. */ #ifdef CONFIG_ZYNQMP_EEPROM #define CONFIG_SYS_I2C_EEPROM_ADDR_LEN 1 #define CONFIG_CMD_EEPROM #define CONFIG_BOOTCOMMANDZYNQ_EEPROM_BUS "run uenvboot; mmcinfo && fatload mmc 1 ${netstart} ${kernel_img};bootm ${netstart}"5 #define CONFIG_ZYNQ_GEM_EEPROM_ADDR 0x54 #define CONFIG_ZYNQ_GEM_I2C_MAC_OFFSET 0x20 #endif |

Device Tree

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

/* default */

/* SD */

&sdhci1 {

// disable-wp;

no-1-8-v;

};

/* USB */

&dwc3_0 {

status = "okay";

dr_mode = "host";

};

/* ETH PHY */

&gem3 {

phy-handle = <&phy0>;

phy0: phy0@1 {

device_type = "ethernet-phy";

reg = <1>;

};

};

/* QSPI */

&qspi {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

flash0: flash@0 {

compatible = "jedec,spi-nor";

reg = <0x0>;

#address-cells = <1>;

#size-cells = <1>;

};

};

/* I2C */

&i2c0 {

i2cswitch@73 { // u

compatible = "nxp,pca9548";

#address-cells = <1>;

#size-cells = <0>;

reg = <0x73>;

i2c-mux-idle-disconnect;

i2c@2 { // PCIe

#address-cells = <1>;

#size-cells = <0>;

reg = <2>;

};

i2c@3 { // i2c SFP

#address-cells = <1>;

#size-cells = <0>;

reg = <3>;

};

i2c@4 { // i2c SFP

#address-cells = <1>;

#size-cells = <0>;

reg = <4>;

};

i2c@5 { // i2c EEPROM

#address-cells = <1>;

#size-cells = <0>;

reg = <5>;

};

i2c@6 { // i2c FMC

#address-cells = <1>;

#size-cells = <0>;

reg = <6>;

si570_2: clock-generator3@5d {

#clock-cells = <0>;

compatible = "silabs,si570";

reg = <0x5d>;

temperature-stability = <50>;

factory-fout = <156250000>;

clock-frequency = <78800000>;

};

};

i2c@7 { // i2c USB HUB

#address-cells = <1>;

#size-cells = <0>;

reg = <7>;

};

};

i2cswitch@77 { // u

compatible = "nxp,pca9548";

#address-cells = <1>;

#size-cells = <0>;

reg = <0x77>;

i2c-mux-idle-disconnect;

i2c@0 { // i2c PMOD

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

};

i2c@1 { // i2c Audio Codec

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

/*

adau1761: adau1761@38 {

compatible = "adi,adau1761";

reg = <0x38>;

};

*/

};

i2c@2 { // i2c FireFly A

#address-cells = <1>;

#size-cells = <0>;

reg = <2>;

};

i2c@3 { // i2c FireFly B

#address-cells = <1>;

#size-cells = <0>;

reg = <3>;

};

i2c@4 { // i2c PLL

#address-cells = <1>;

#size-cells = <0>;

reg = <4>;

};

i2c@5 { // i2c SC

#address-cells = <1>;

#size-cells = <0>;

reg = <5>;

};

i2c@6 { // i2c

#address-cells = <1>;

#size-cells = <0>;

reg = <6>;

};

i2c@7 { // i2c

#address-cells = <1>;

#size-cells = <0>;

reg = <7>;

};

};

};

/* UNUSED DMA disable */

&lpd_dma_chan1 {

status = "disabled";

};

&lpd_dma_chan2 {

status = "disabled";

};

&lpd_dma_chan3 {

status = "disabled";

};

&lpd_dma_chan4 {

status = "disabled";

};

&lpd_dma_chan5 {

status = "disabled";

};

&lpd_dma_chan6 {

status = "disabled";

};

&lpd_dma_chan7 {

status = "disabled";

};

&lpd_dma_chan8 {

status = "disabled";

};

|

...

See: \os\petalinux\project-spec\meta-user\recipes-apps\startup\files

adau1761init

Audio initialisation.

Additional Software

| HTML |

|---|

<!-- Add Description for other Software, for example SI CLK Builder ... --> |

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| v.21 | John Hartfiel |

| |||||||||||||||||||||||

| v.19 | John Hartfiel |

| |||||||||||||||||||||||

| v.18 | John Hartfiel |

| |||||||||||||||||||||||

| 2018-02-08 | v.16 | John Hartfiel |

| ||||||||||||||||||||||

| 2018-01-29 | v.10 | John Hartfiel |

| ||||||||||||||||||||||

| 2018-01-18 | v.8 | John Hartfiel |

| ||||||||||||||||||||||

| 2018-01-17 | v.7 | John Hartfiel |

| ||||||||||||||||||||||

| 2018-01-15 | v.4 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-12-20 | v.2 | John Hartfiel |

| ||||||||||||||||||||||

| All |

|

...