Page History

...

| HTML |

|---|

<!-- General Design description --> |

Zynq PS Design with DDR Less FSBL Example.

Key Features

| HTML |

|---|

<!-- Add Basic Key Features of the design (should be tested) --> |

...

| HTML |

|---|

<!-- - Add changes from design - Export PDF to download, if vivado revision is changed! --> |

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-08-14 | 2018.2 | TE0722-test_board-vivado_2018.2-build_02_20180815123557.zip TE0722-test_board_noprebuilt-vivado_2018.2-build_02_20180815123610.zip | John Hartfiel | initial release |

Release Notes and Know Issues

...

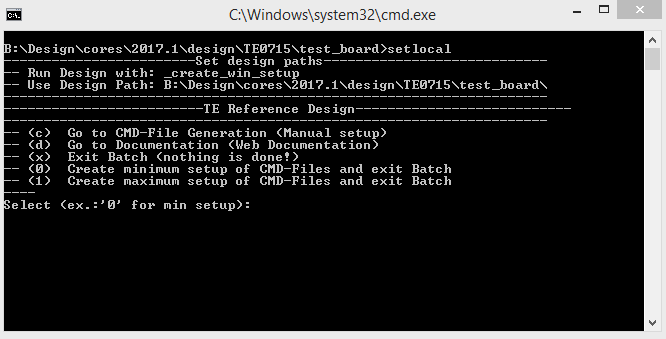

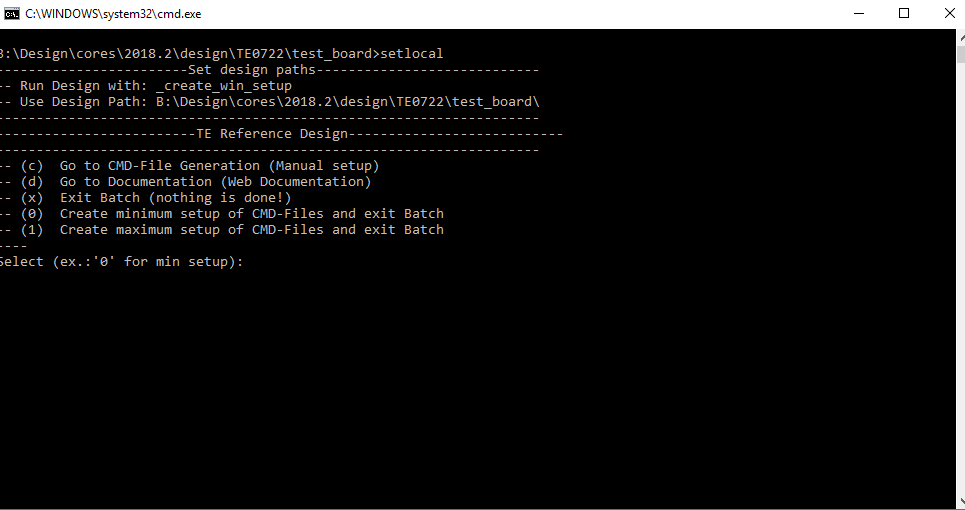

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter for minimum setup

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

- Run on Vivado TCL: TE::sw_run_hsi

Launch

Basic Information, see TE0722 Getting Started

Programming

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

...

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-bootfsbl_app

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

...

- Prepare HW like described on section Programming

- Connect UART USB (most cases same as JTAG)

- Power On PCB

Note: 1. Zynq Boot ROM loads FSBL from SD QSPI into OCM, 2. FSBL loads U-boot from SD into DDR, 3. U-boot load Linux from SD into DDR

...

- bitfile from qsi, 3. FSBL starts application

Baremetal App

Note: UART over J2 is used, this is only available, if PL part is configured.

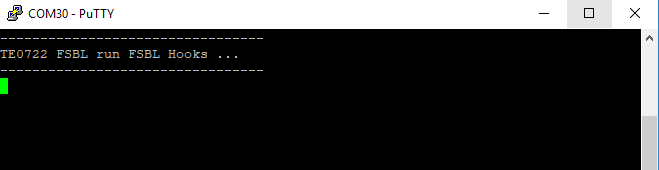

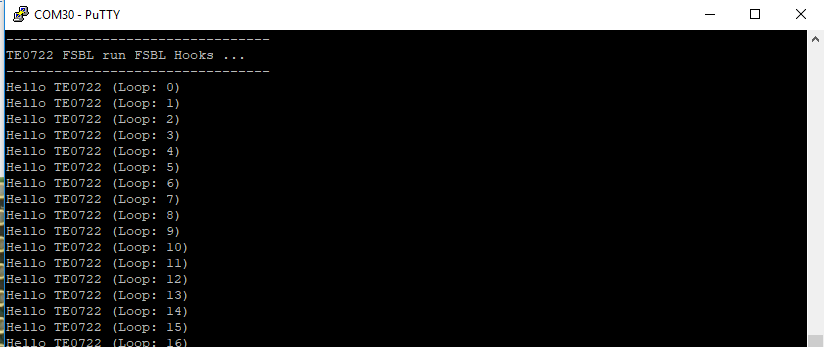

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Output:

- TODO

- Default output appears only one time. Reboot device: force ResN Pin to GND for short time, location see: TE0722 Getting Started

- alternately Hello TE0722 loop (for 100sec): uncomment loop in fsbl example (fsbl_hooks.c) and regenerate FSBL and Boot.bin

- TODO

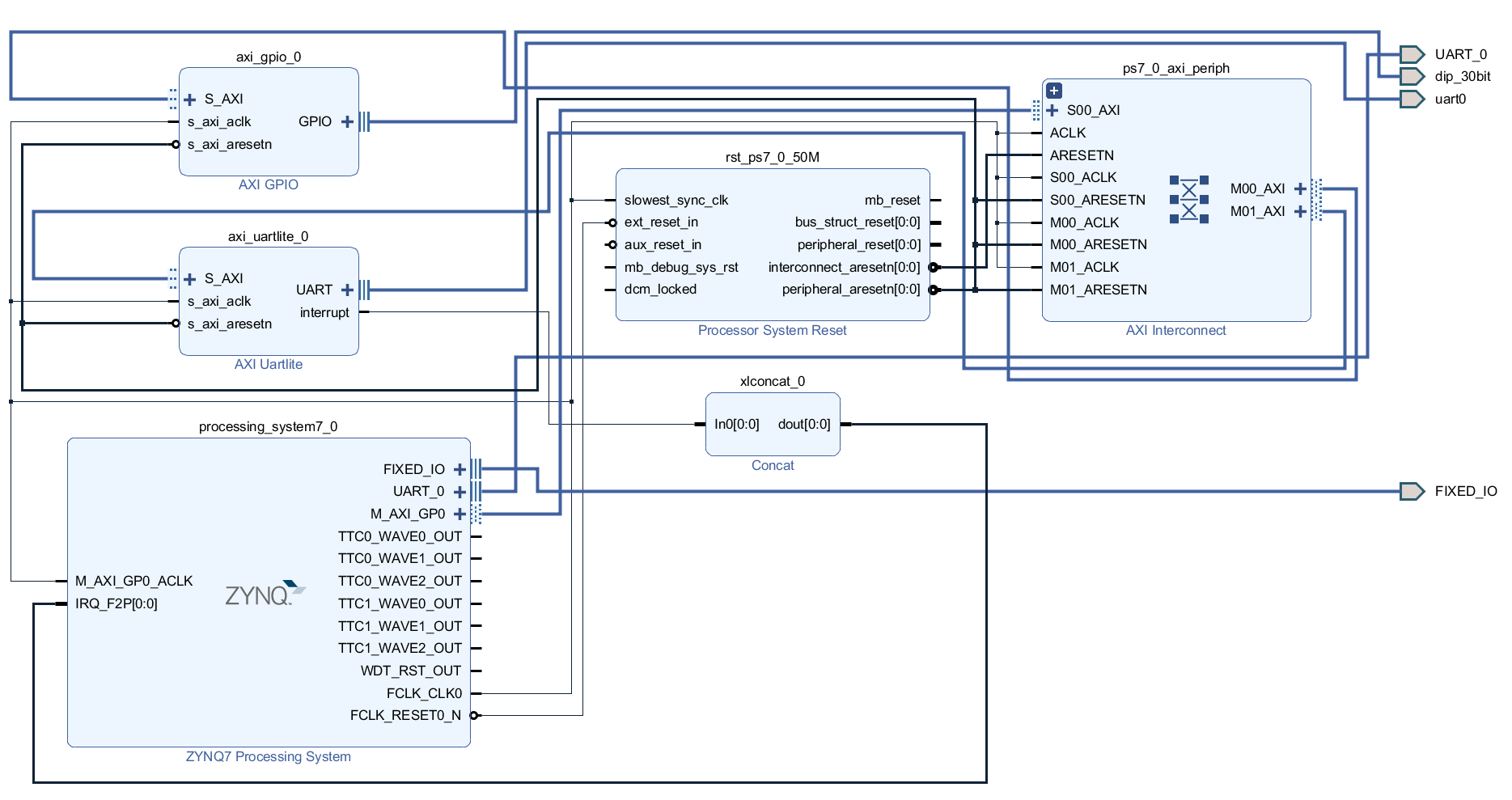

System Design - System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

Block Design

PS Interfaces

Constrains

Basic module constrains

...

| language | ruby |

|---|---|

| title | _i_bitgen_common.xdc |

| Type | Note |

|---|---|

| DDR | Disabled! |

| QSPI | MIO |

| SD | MIO |

| UART0 | EMIO |

| I2C1 | MIO |

| GPIO | MIO |

| SWDT0 | EMIO |

| TTC0..1 | EMIO |

Constrains

Basic module constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

#

# Common BITGEN related settings for TE0722

#

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design] |

Design specific constrain

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property PACKAGE_PIN K15 [get_ports UART_0_txd]

set_property PACKAGE_PIN L13 [get_ports UART_0_rxd]

set_property IOSTANDARD LVCMOS33 [get_ports UART_0_*] |

Design specific constrain

| Code Block | |

|---|---|

| language | ruby | title | _i_io.xdc

Software Design - SDK/HSI

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| 2018-10-14 | v.1 |

|

| ||||||||||||||||||||||

| All |

|

...

Overview

Content Tools