Page History

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-09-05 | 2018.2 | John Hartfiel |

| |

| 2018-05-25 | 2017.4 | te0712-test_board-vivado_2017.4-build_10_20180525155402.zip te0712-test_board_noprebuilt-vivado_2017.4-build_10_20180525155555.zip | John Hartfiel |

|

| 2018-04-12 | 2017.4 | te0712-test_board-vivado_2017.4-build_07_20180412081225.zip te0712-test_board_noprebuilt-vivado_2017.4-build_07_20180412081253.zip | John Hartfiel |

|

| 2018-03-28 | 2017.4 | te0712-test_board-vivado_2017.4-build_07_20180328145151.zip te0712-test_board_noprebuilt-vivado_2017.4-build_07_20180328145135.zip | John Hartfiel |

|

| 2018-01-08 | 2017.4 | te0712-test_board-vivado_2017.4-build_02_20180108155712.zip te0712-test_board_noprebuilt-vivado_2017.4-build_02_20180108155735.zip | John Hartfiel |

|

| 2017-12-15 | 2017.2 | te0712-test_board-vivado_2017.2-build_07_20171215172447.zip te0712-test_board_noprebuilt-vivado_2017.2-build_07_20171215172514.zip | John Hartfiel |

|

| 2017-11-07 | 2017.2 | te0712-test_board-vivado_2017.2-build_05_20171107172917.zip te0712-test_board_noprebuilt-vivado_2017.2-build_05_20171107172939.zip | John Hartfiel |

|

| 2017-10-05 | 2017.2 | te0712-test_board-vivado_2017.2-build_03_20171005082148.zip te0712-test_board_noprebuilt-vivado_2017.2-build_03_20171005082225.zip | John Hartfiel |

|

...

| Software | Version | Note |

|---|---|---|

| Vivado | 20172018.42 | needed |

| SDK | 20172018.42 | needed |

| PetaLinux | 20172018.42 | needed |

Hardware

| HTML |

|---|

<!-- Hardware Support --> |

...

Reference Design is available on:

Design Flow

| HTML |

|---|

<!-- Basic Design Steps Add/ Remove project specific --> |

...

- Connect JTAG and power on PCB

- (if not done) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd" or open with "vivado_open_project_guimode.cmd", if generated.

- Type on Vivado Console: TE::pr_program_flash_mcsfile -swapp u-boot

Note: Alternative use SDK or setup Flash on Vivado manually

optional "TE::pr_program_flash_binfile -swapp hello_te0712" possible - Reboot (if not done automatically)

...

Boot process takes a while, please wait.

Linux

Note: Linux boot process is slower on Microblaze.

...

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

set_property PULLDOWN true [get_ports reset] |

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

#I2C

#set_property PACKAGE_PIN W21 [get_ports PLL_I2C_scl_io]

#set_property IOSTANDARD LVCMOS33 [get_ports PLL_I2C_scl_io]

#set_property PACKAGE_PIN T20 [get_ports PLL_I2C_sda_io]

#set_property IOSTANDARD LVCMOS33 [get_ports PLL_I2C_sda_io]

set_property PACKAGE_PIN W21 [get_ports PLL_I2C_ext_scl_o]

set_property IOSTANDARD LVCMOS33 [get_ports PLL_I2C_ext_scl_o]

set_property PACKAGE_PIN T20 [get_ports PLL_I2C_ext_sda]

set_property IOSTANDARD LVCMOS33 [get_ports PLL_I2C_ext_sda]

#Reset

set_property PACKAGE_PIN T3 [get_ports reset]

set_property IOSTANDARD LVCMOS15 [get_ports reset]

#CLKS

set_property PACKAGE_PIN R4 [get_ports {CLK1B[0]}]

set_property IOSTANDARD LVCMOS15 [get_ports {CLK1B[0]}]

set_property PACKAGE_PIN K4 [get_ports {CLK0_clk_p[0]}]

set_property IOSTANDARD DIFF_SSTL15 [get_ports {CLK0_clk_p[0]}]

#ETH PHY

set_property PACKAGE_PIN N17 [get_ports phy_rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports phy_rst_n |

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

create_clock -period 8.000 -name mgt_clk0_clk_p -waveform {0.000 4.000} [get_ports mgt_clk0_clk_p]

create_clock -period 10.000 -name {CLK0_clk_p[0]} -waveform {0.000 5.000} [get_ports {CLK0_clk_p[0]}]

create_clock -period 20.000 -name {CLK1B[0]} -waveform {0.000 10.000} [get_ports {CLK1B[0]}]

create_clock -period 15.152 -name msys_i/axi_quad_spi_0/U0/ CFGMCLK -waveform {0.000 7.576} [get_pins -hierarchical -filter {NAME =~*NO_DUAL_QUAD_MODE.QSPI_NORMAL/QSPI_LEGACY_MD*STARTUP_7SERIES_GEN.QSPISTARTUP2_CORE7SERIES_INTERFACE_I/LOGIC_FOR_MD_12_GEN.SCK_MISO_STARTUP_USED.QSPI_STARTUP_BLOCK_I/cfgmclk -waveform {0.000 7.576}inst/CFGMCLK}]

set_false_path -from [get_clocks {CLK0_clk_p[0]}] -to [get_clocks clk_pll_i]

set_false_path -from [get_clocks mgt_clk0_clk_p] -to [get_clocks clk_pll_i]

set_false_path -from [get_pins {msys_i/axiSC0712_quad_spi_0/U0/NOrst_DUALdelay_QUAD_MODE.QSPI_NORMAL/QSPI_LEGACY_MD_GEN.QSPI_CORE_INTERFACE_I/LOGIC_FOR_MD_12_GEN.SCK_MISO_STARTUP_USED.QSPI_STARTUP_BLOCK_I/STARTUP_7SERIES_GEN.STARTUP2_7SERIES_inst/CFGMCLK]

set_false_path -from [get_clocks {CLK0_clk_p[0]}i_reg[3]/C}] -to [get_pins -hierarchical -filter {NAME =~*u_msys_mig_7series_0_0_mig/u_ddr3_infrastructure/rstdiv0*/PRE}]

set_false_path -from [get_clocks -of_objects [get_pins msys_i/mig_7series_0/u_msys_mig_7series_0_0_mig/u_ddr3_infrastructure/gen_ui_extra_clocks.mmcm_i/CLKFBOUT]] -to [get_clocks mgt_clk0_clk_pll_ip]

set_false_path -from [get_clocks mgtclk_clk0pll_clk_pi] -to [get_clocks clk_pll_i{msys_i/util_ds_buf_0/U0/IBUF_OUT[0]}]

set_false_path -from [get_clockspins {msys_i/axilabtools_quadfmeter_spi_0/U0/NO_DUAL_QUAD_MODE.QSPI_NORMAL/QSPI_LEGACY_MD_GEN.QSPI_CORE_INTERFACE_I/LOGIC_FOR_MD_12_GEN.SCK_MISO_STARTUP_USED.QSPI_STARTUP_BLOCK_I/cfgmclkF_reg[*]/C}] -to [get_pins {msys_i/vio_0/inst/PROBE_IN_INST/probe_in_reg_reg[*]/D}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/COUNTER_REFCLK_inst/bl.DSP48E_2/CLK] -to [get_clocks clk_pll_i]

pins {msys_i/vio_0/inst/PROBE_IN_INST/probe_in_reg_reg[*]/D}]

set_false_path -from [get_clocks -of_objects [get_pins pins {msys_i/miglabtools_7seriesfmeter_0/u_msys_mig_7series_0_0_mig/u_ddr3_infrastructure/gen_ui_extra_clocks.mmcm_i/CLKFBOUT]U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CLK}] -to [get_clocks mgt_clk0_clk_p]

set_false_path -from [get_clocks clk_pll_i] -to [get_clocks {msys_i/util_ds_buf_0/U0/IBUF_OUT[0]}]

set_false_path -from [get_pins {msys_i/labtools_fmeter_0/U0/F_reg[*]/C}] -to [get_pins {msys_i/vio_0/inst/PROBE_IN_INST/probe_in_reg_reg[*]/D}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/COUNTER_REFCLK_inst/bl.DSP48E_2/CLK] -to [get_pins {msys_i/vio_0/inst/PROBE_IN_INST/probe_in_reg_reg[*]/D}]

set_false_path -from [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CLK}] -to [get_pins {msys_i/labtools_fmeter_0/U0/F_reg[*]/D}]

|

Software Design - SDK/HSI

| HTML |

|---|

<!--

optional chapter

separate sections for different apps

--> |

For SDK project creation, follow instructions from:

Application

SCU

MCS Firmware to configure SI5338 and Reset System.

Template location: \sw_lib\sw_apps\scu

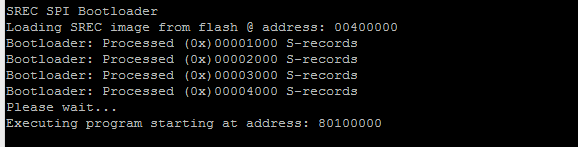

SREC SPI BootLoader

Add some Console outputs and changed Bootloader Read Address.

Template location: \sw_lib\sw_apps\srec_spi_bootloader

xilisf_v5_9

Changed default Flash Typ to 5.

Template location: \sw_lib\sw_services

U-Boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate u-boot.srec. Vivado to generate *.mcs

Software Design - PetaLinux

| HTML |

|---|

<!--

optional chapter

--> |

Description currently not available.

Config

- Set kernel flash Address to 0x900000 and Kernel size to 0xA00000:

(--> Subsystem Auto Hardware Settings --> Flash Settings)- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART0_SIZE = 0x5E0000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART1_SIZE = 0x300000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART2_SIZE = 0x20000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART3_SIZE = 0xA00000

U-Boot

| Code Block | ||

|---|---|---|

| ||

#include <configs/platform-auto.h>

#undef CONFIG_PHY_XILINX

#undef XILINX_EMACLITE_BASEADDR 0x40E00000

#undef CONFIG_MII

#undef CONFIG_PHY_GIGE

#undef CONFIG_PHY_MARVELL

#undef CONFIG_PHY_NATSEMI

#undef CONFIG_NET_MULTI

#undef CONFIG_BOOTP_MAY_FAIL

#undef CONFIG_NETCONSOLE 1

#undef CONFIG_SERVERIP 192.168.150.117

#undef CONFIG_IPADDR

/* PREBOOT */

#define CONFIG_PREBOOT "echo U-BOOT for petalinux;setenv preboot; echo; "

|

Device Tree

pins {msys_i/labtools_fmeter_0/U0/F_reg[*]/D}]

|

Software Design - SDK/HSI

| HTML |

|---|

<!--

optional chapter

separate sections for different apps

--> |

For SDK project creation, follow instructions from:

Application

Template location: ./sw_lib/sw_apps/

scu

MCS Firmware to configure SI5338 and Reset System.

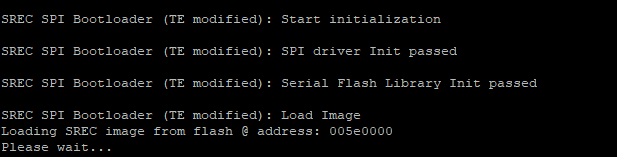

srec_spi_bootloader

Boadloader to load app or second bootloader from flash into DDR

Changes:

- Add some vonsole outputs and changed bootloader read address.

- Add bugfix for 2018.2 qspi flash

xilisf_v5_11

- Changed default Flash Typ to 5.

hello_te0712

Hello TE0712 is a Xilinx Hello World example as endless loop instead of one console output.

u-boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate u-boot.srec. Vivado to generate *.mcs

Software Design - PetaLinux

| HTML |

|---|

<!--

optional chapter

--> |

Description currently not available.

Config

- Set kernel flash Address to 0x900000 and Kernel size to 0xA00000:

(--> Subsystem Auto Hardware Settings --> Flash Settings)- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART0_SIZE = 0x5E0000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART1_SIZE = 0x300000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART2_SIZE = 0x20000

- SUBSYSTEM_FLASH_AXI_QUAD_SPI_0_BANKLESS_PART3_SIZE = 0xA00000

U-Boot

| Code Block | ||

|---|---|---|

| ||

#include <configs/platform-auto.h>

#define CONFIG_SYS_BOOTM_LEN 0xF000000

/* ethernet - axi_ethernetlite_0 */

#undef CONFIG_PHY_XILINX

#undef XILINX_EMACLITE_BASEADDR 0x40E00000

#undef CONFIG_MII

#undef CONFIG_NET_MULTI

#undef CONFIG_NETCONSOLE 1

#undef CONFIG_SERVERIP 192.168.150.127

#undef CONFIG_IPADDR

/* PREBOOT */

#define CONFIG_PREBOOT "echo U-BOOT for petalinux;setenv preboot; echo;"

|

Device Tree

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

/* QSPI PHY */

&axi_quad_spi_0 {

#address-cells = <1>;

#size-cells = <0>;

flash0: flash@0 {

compatible = "jedec,spi-nor";

spi-tx-bus-width=<1>;

spi-rx-bus-width=<4>;

reg = <0x0>;

#address-cells = <1>;

#size-cells = <1>;

spi-max-frequency = <25000000>;

};

};

| ||

| Code Block | ||

| ||

/include/ "system-conf.dtsi"

/ {

};

/* ETH PHY */

&axi_ethernetlite_0 {

phy-handle = <&phy0>;

mdio {

#address-cells = <1>;

#size-cells = <0>;

phy0: phy@0 {

device_type = "ethernet-phy";

reg = <1>;

};

};

};

|

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| v.28 | John Hartfiel |

| |||||||||||||||||||||||

| v.27 | John Hartfiel |

| |||||||||||||||||||||||

| v.23 | John Hartfiel |

| |||||||||||||||||||||||

| v.22 | John Hartfiel |

| |||||||||||||||||||||||

| 2018-02-13 | v.19 | John Hartfiel |

| ||||||||||||||||||||||

| 2018-01-08 | v.16 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-12-15 | v.15 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-11-07 | v.11 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-06 | v.10 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-05 | v.8 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-09-11 | v.1 |

|

| ||||||||||||||||||||||

| All |

|

...