Page History

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-09-05 | 2018.2 | te0712-test_board-vivado_2018.2-build_03_20180906071356.zip te0712-test_board_noprebuilt-vivado_2018.2-build_03_20180906071434.zip | John Hartfiel |

|

| 2018-05-25 | 2017.4 | te0712-test_board-vivado_2017.4-build_10_20180525155402.zip te0712-test_board_noprebuilt-vivado_2017.4-build_10_20180525155555.zip | John Hartfiel |

|

| 2018-04-12 | 2017.4 | te0712-test_board-vivado_2017.4-build_07_20180412081225.zip te0712-test_board_noprebuilt-vivado_2017.4-build_07_20180412081253.zip | John Hartfiel |

|

| 2018-03-28 | 2017.4 | te0712-test_board-vivado_2017.4-build_07_20180328145151.zip te0712-test_board_noprebuilt-vivado_2017.4-build_07_20180328145135.zip | John Hartfiel |

|

| 2018-01-08 | 2017.4 | te0712-test_board-vivado_2017.4-build_02_20180108155712.zip te0712-test_board_noprebuilt-vivado_2017.4-build_02_20180108155735.zip | John Hartfiel |

|

| 2017-12-15 | 2017.2 | te0712-test_board-vivado_2017.2-build_07_20171215172447.zip te0712-test_board_noprebuilt-vivado_2017.2-build_07_20171215172514.zip | John Hartfiel |

|

| 2017-11-07 | 2017.2 | te0712-test_board-vivado_2017.2-build_05_20171107172917.zip te0712-test_board_noprebuilt-vivado_2017.2-build_05_20171107172939.zip | John Hartfiel |

|

| 2017-10-05 | 2017.2 | te0712-test_board-vivado_2017.2-build_03_20171005082148.zip te0712-test_board_noprebuilt-vivado_2017.2-build_03_20171005082225.zip | John Hartfiel |

|

...

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

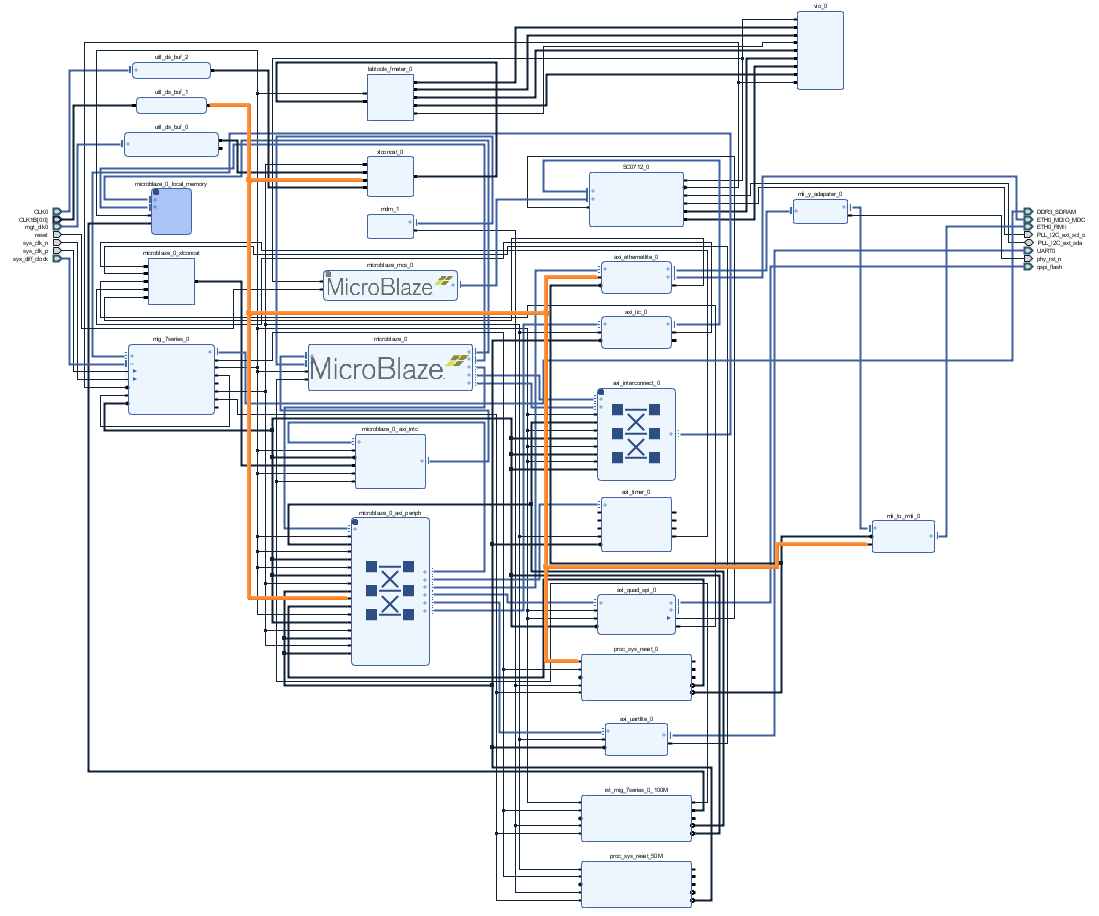

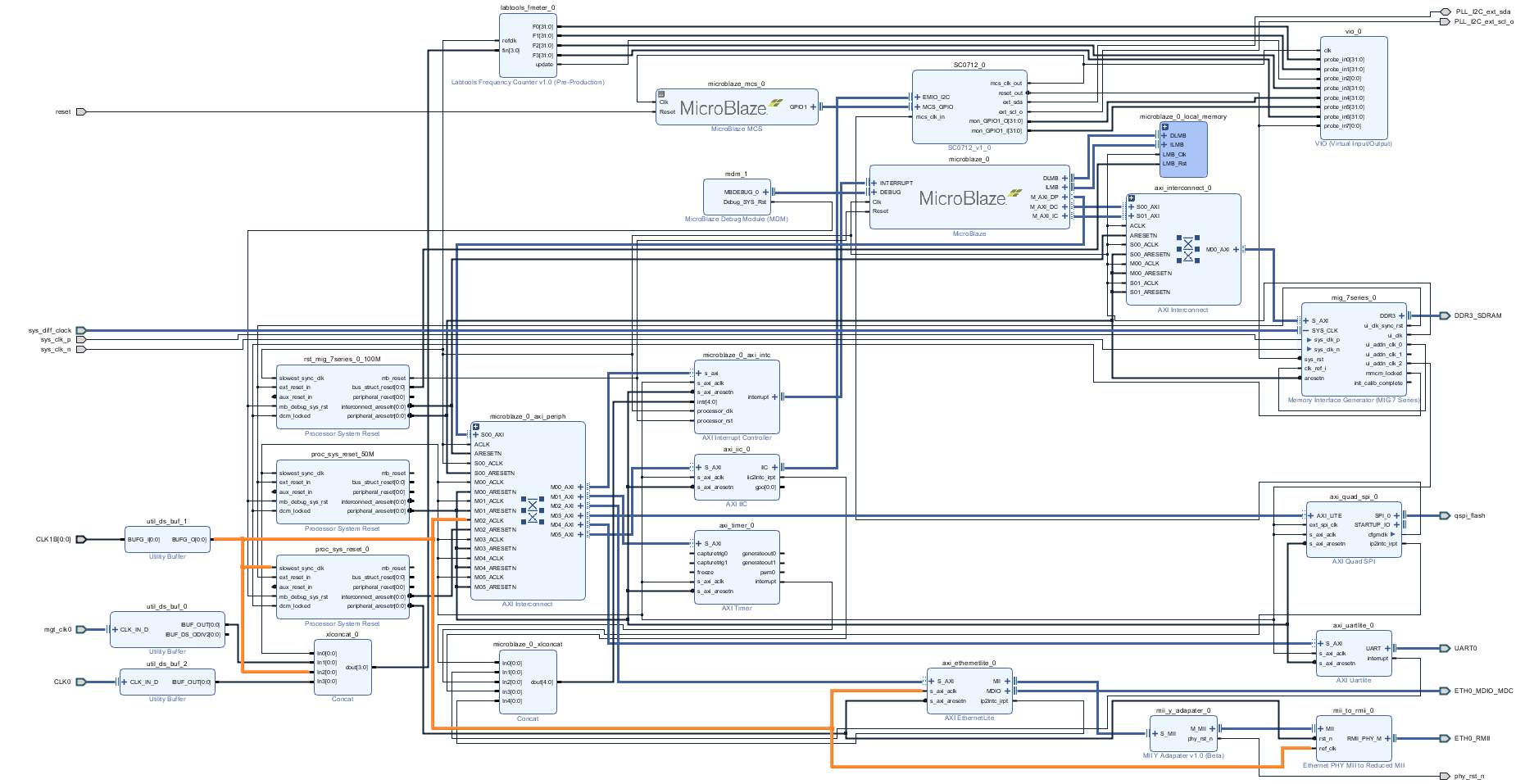

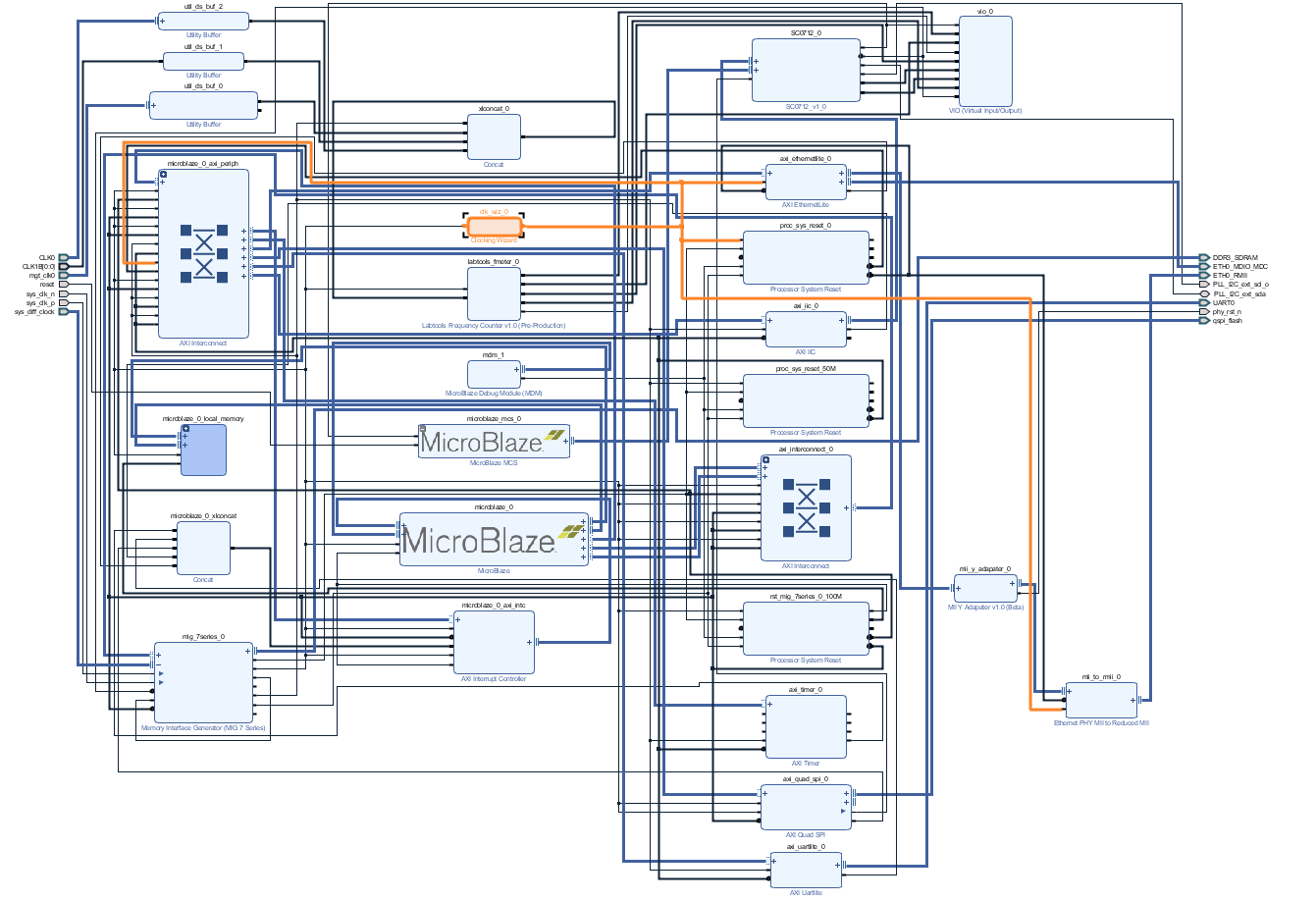

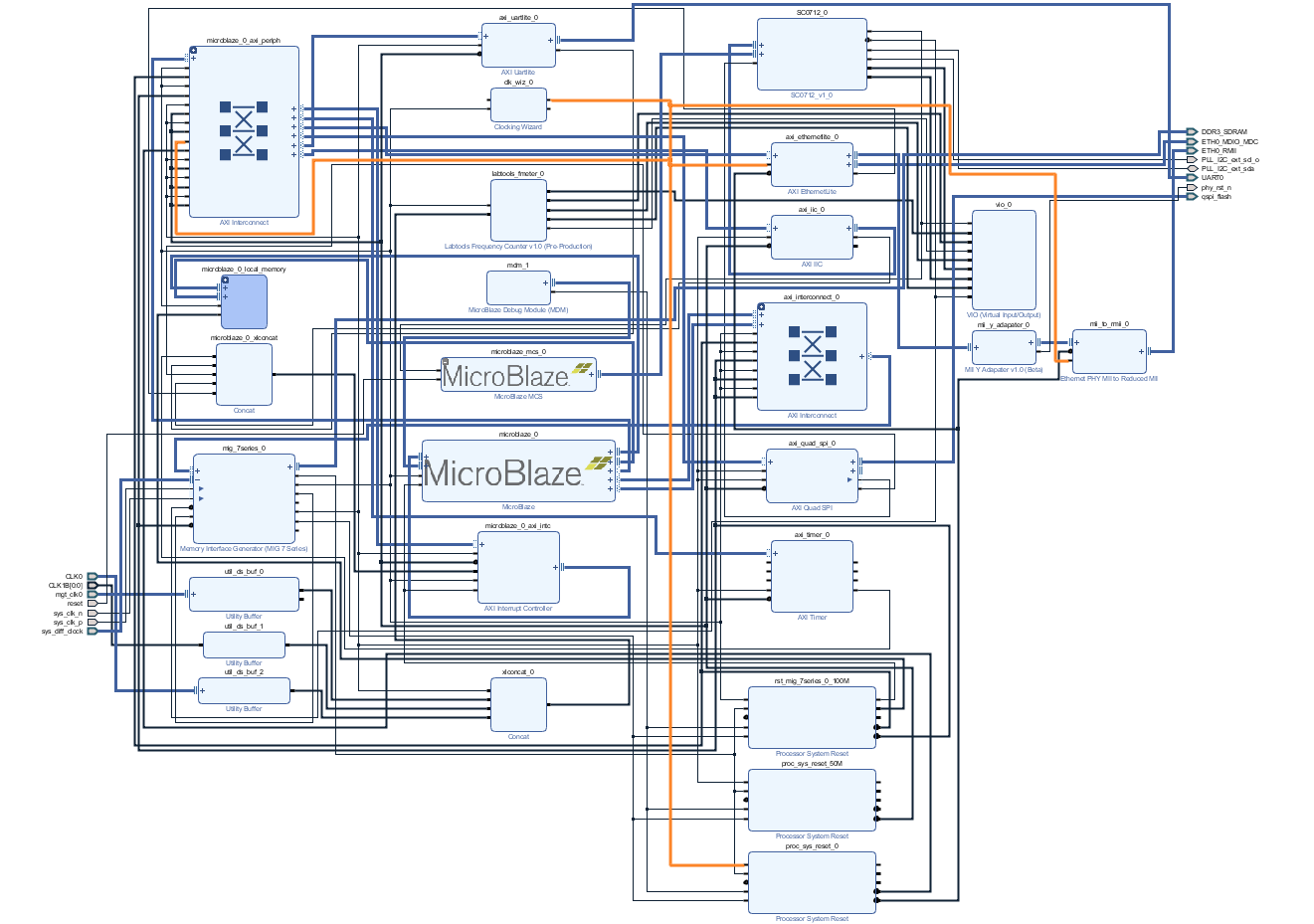

Block Design

REV02

REV01

Same as REV02 but 50 MHz ETH REV CLK is generated from MIG output with 180° Phase shift.

Constrains

Basic module constrains

...

U-Boot

| Code Block | ||

|---|---|---|

| ||

#include <configs/platform-auto.h>

#define CONFIG_SYS_BOOTM_LEN 0xF000000

/* ethernet - axi_ethernetlite_0 */

#undef CONFIG_PHY_XILINX

#undef XILINX_EMACLITE_BASEADDR 0x40E00000

#undef CONFIG_MII

#undef CONFIG_NET_MULTI

#undef CONFIG_NETCONSOLE 1

#undef CONFIG_SERVERIP 192.168.150.127

#undef CONFIG_IPADDR

/* PREBOOT */

#define CONFIG_PREBOOT "echo U-BOOT for petalinux;setenv preboot; echo;"

|

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| v.28 | John Hartfiel |

| |||||||||||||||||||||||

| v.27 | John Hartfiel |

| |||||||||||||||||||||||

| v.23 | John Hartfiel |

| |||||||||||||||||||||||

| v.22 | John Hartfiel |

| |||||||||||||||||||||||

| 2018-02-13 | v.19 | John Hartfiel |

| ||||||||||||||||||||||

| 2018-01-08 | v.16 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-12-15 | v.15 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-11-07 | v.11 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-06 | v.10 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-05 | v.8 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-09-11 | v.1 |

|

| ||||||||||||||||||||||

| All |

|

...

Overview

Content Tools