Page History

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

...

| Scroll Title | |||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||

|

Hardware

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

...

| Page properties | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Notes :

|

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

...

Reference Design is available on:

Design Flow

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

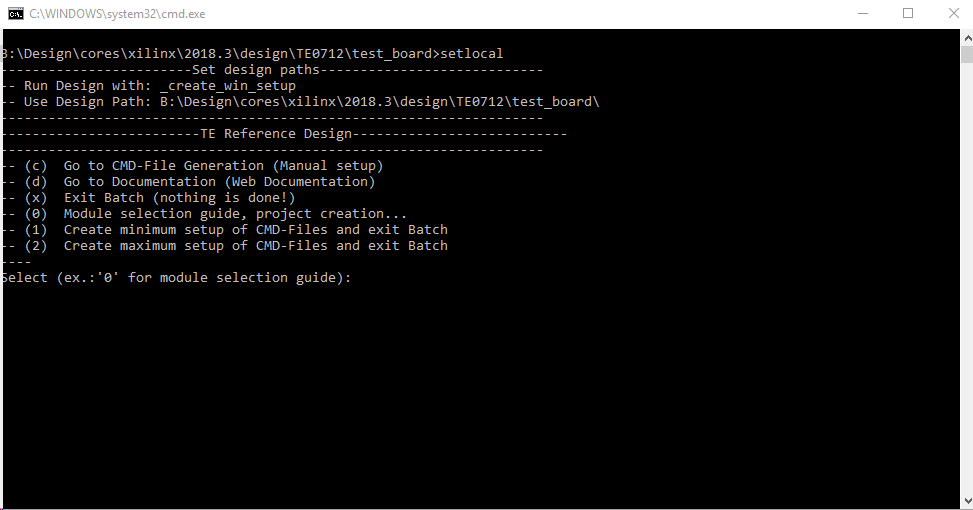

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF XSA and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Create Linux (uboot.elf and image.ub) with exported HDFXSA

- HDF XSA is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

Note: run init_config.sh before you start petalinux config. This will set correct temporary path variable.

Important Note: Select correct Flash partition offset on petalinux-config: Subsystem Auto HW Settings → Flash Settings, FPGA+Boot+bootenv=0x900000 (increase automatically generate Boot partition), increas increase image size to A:, see 54395771

- Use TE Template from /os/petalinux

- HDF XSA is exported to "prebuilt\hardware\<short name>"

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

"prebuilt\os\petalinux\

default<ddr size>" or "prebuilt\os\petalinux\<short name>"

default"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\

- (not longer needed manually: This will be done with Step 10.a automatically with newer scripts (2017.4.10) ) Generate UBoot SREC:

- Create SDK Project with TE Scripts on Vivado TCL: TE::sw_run_sdk

- Create "uboot-dummy" application

Note: Use Hello World Example - Copy u-boot.elf into "\workspace\sdk\uboot-dummy\Debug"

- Open "uboot-dummy" properties → C/C++ Build → Settings and go into Build Steps Tap.

- Add to Post-build steps: mb-objcopy -O srec u-boot.elf u-boot.srec

- Press Apply or regenerate project

Note: SREC is generated on "\workspace\sdk\uboot-dummy\Debug\u-boot.srec"

- Generate MCS Firmware (optional):

- Create SDK Project with TE Scripts on Vivado TCL: TE::sw_run_sdk

- Create "SCU" application

Note: Select MCS Microblaze and SCU Application - Select Release Built

- Regenerate App

<DDR size>" of the selected device

- Generate Programming Files with Vitis

- Run on Vivado TCL

- Run on Vivado TCL: TE::sw_run_hsivitis -all

Note: Depending of PC performance this can take several minutes. Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" and open Vitis - (alternative) Start SDK Vitis with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdkvitis

Note: See SDK Projects TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

- Copy "\prebuilt\software\<short name>\srec_spi_bootloader.elf" into "\firmware\microblaze_0\"

- (optional) Copy "\\workspace\sdk\scu\Release\scu.elf" into "\firmware\microblaze_mcs_0\"

- Regenerate Vivado Project or Update Bitfile only with "srec_spi_bootloader.elf" and "scu.elf"

Launch

Programming

- _bootloader.elf" and "scu.elf"

Launch

Programming

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

| ||||

| HTML | ||||

| <!--

Description of Block Design, Constrains...

BD Pictures from Export...

--> |

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

...

- Prepare HW like described on section 54395771

- Connect UART USB (most cases same as JTAG)

- Power on PCB

Note: FPGA Loads Bitfile from Flash,MCS Firmware configure SI5338 and starts Microblaze, SREC Bootloader from Bitfile Firmware loads U-Boot into DDR (This takes a while), U-boot loads Linux from QSPI Flash into DDRwhile), U-boot loads Linux from QSPI Flash into DDR - Open Serial Console (e.g. putty)

- Speed: 9600

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

Boot process takes a while, please wait.

...

| Code Block | ||||||

|---|---|---|---|---|---|---|

| ||||||

create_clock -period 8.000 -name mgt_clk0_clk_p -waveform {0.000 4.000} [get_ports mgt_clk0_clk_p]

create_clock -period 10.000 -name {CLK0_clk_p[0]} -waveform {0.000 5.000} [get_ports {CLK0_clk_p[0]}]

create_clock -period 20.000 -name {CLK1B[0]} -waveform {0.000 10.000} [get_ports {CLK1B[0]}]

create_clock -period 15.152 -name CFGMCLK -waveform {0.000 7.576} [get_pins -hierarchical -filter {NAME =~*NO_DUAL_QUAD_MODE.QSPI_NORMAL/*STARTUP_7SERIES_GEN.STARTUP2_7SERIES_inst/CFGMCLK}]

set_false_path -from [get_clocks {CLK0_clk_p[0]}] -to [get_clocks clk_pll_i]

set_false_path -from [get_clocks mgt_clk0_clk_p] -to [get_clocks clk_pll_i]

set_false_path -from [get_pins {msys_i/SC0712_0/U0/rst_delay_i_reg[3]/C}] -to [get_pins -hierarchical -filter {NAME =~*u_msys_mig_7series_0_0_mig/u_ddr3_infrastructure/rstdiv0*/PRE}]

set_false_path -from [get_clocks -of_objects [get_pins msys_i/mig_7series_0/u_msys_mig_7series_0_0_mig/u_ddr3_infrastructure/gen_ui_extra_clocks.mmcm_i/CLKFBOUT]] -to [get_clocks mgt_clk0_clk_p]

set_false_path -from [get_clocks clk_pll_i] -to [get_clocks {msys_i/util_ds_buf_0/U0/IBUF_OUT[0]}]

set_false_path -from [get_pins {msys_i/labtools_fmeter_0/U0/F_reg[*]/C}] -to [get_pins {msys_i/vio_0/inst/PROBE_IN_INST/probe_in_reg_reg[*]/D}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/COUNTER_REFCLK_inst/bl.DSP48E_2/CLK] -to [get_pins {msys_i/vio_0/inst/PROBE_IN_INST/probe_in_reg_reg[*]/D}]

set_false_path -from [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CLK}] -to [get_pins {msys_i/labtools_fmeter_0/U0/F_reg[*]/D}]

|

Software Design -

...

Vitis

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

...

For SDK project creation, follow instructions from:SDK Projects

Application

Template location: ./sw_lib/sw_apps/

...

srec_spi_bootloader

TE modified 20182019.3 2 SREC

Bootloader to load app or second bootloader from flash into DDR

...

- Modified Files: blconfig.h, bootloader.c

- Changes:

- Add some console outputs and changed bootloader read address.

- Add bugfix for 2018.2 qspi flash (some reinitialisation)

xilisf_v5_

...

14

TE modified 20182019.3 2 xilisf_v5_1114

- Changed default Flash type to 5.

...

Start with petalinux-config -c u-boot

Changes:

- CONFIG_ENV_IS_NOWHERE=y

- # CONFIG_ENV_IS_IN_SPI_FLASH is not set

# CONFIG_NETCONSOLE is not set

- # CONFIG_NET_TFTP_VARS is not set

- # CONFIG_PHY_ATHEROS is not set

- # CONFIG_PHY_BROADCOM is not set

- # CONFIG_PHY_DAVICOM is not set

- # CONFIG_PHY_LXT is not set

- # CONFIG_PHY_MARVELL is not set# CONFIG_PHY_MICREL is not set

# CONFIG_PHY_NATSEMI is not set

- # CONFIG_PHY_REALTEK _KSZ90X1 is not set

CONFIG_PHY_TI=y

- # CONFIG_PHY_XILINX=yMICREL is not set

- # CONFIG_DMPHY_ETH NATSEMI is not set

- # CONFIG_NETDEVICES PHY_REALTEK is not set

- CONFIG_RGMII=y

Change platform-top.h:

| Code Block | ||

|---|---|---|

| ||

#include <configs/platform-auto.h> #define CONFIG_SYS_BOOTM_LEN 0xF000000 |

...

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

/* QSPI PHY */

&axi_quad_spi_0 {

#address-cells = <1>;

#size-cells = <0>;

flash0: flash@0 {

compatible = "jedec,spi-nor";

spi-tx-bus-width=<1>;

spi-rx-bus-width=<4>;

reg = <0x0>;

#address-cells = <1>;

#size-cells = <1>;

spi-max-frequency = <25000000>;

};

};

/* ETH PHY */

&axi_ethernetlite_0 {

phy-handle = <&phy0>;

mdio {

#address-cells = <1>;

#size-cells = <0>;

phy0: phy@0 {

device_type = "ethernet-phy";

reg = <1>;

};

};

};

|

Kernel

Start with petalinux-config -c kernel

Changes:

- No changes.

Rootfs

Start with petalinux-config -c rootfs

Changes:

- No changes.

Kernel

Start with petalinux-config -c kernel

Changes:

- No changes.

Rootfs

Start with petalinux-config -c rootfs

Changes:

- # CONFIG_dropbear is not set

- # CONFIG_dropbear-dev is not set

- # CONFIG_dropbear-dbg is not set

- # CONFIG_packagegroup-core-ssh-dropbear is not set

- # CONFIG_packagegroup-core-ssh-dropbear-dev is not set

- # CONFIG_packagegroup-core-ssh-dropbear-dbg is not set

- # CONFIG_imagefeature-ssh-server-dropbear is not set

Applications

No additional application.

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

...