Page History

Template Revision 2.1 - on construction

...

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

...

| hidden | true |

|---|---|

| id | Comments |

Important General Note:

...

Export PDF to download, if vivado revision is changed!

Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro

...

...

Figure template (note: inner scroll ignore/only only with drawIO object):

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

|

...

Table template:

- Layout macro can be use for landscape of large tables

- Set column width manually(can be used for small tables to fit over whole page) or leave empty (automatically)

...

| anchor | Table_xyz |

|---|---|

| title | Text |

...

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of contents

|

Overview

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

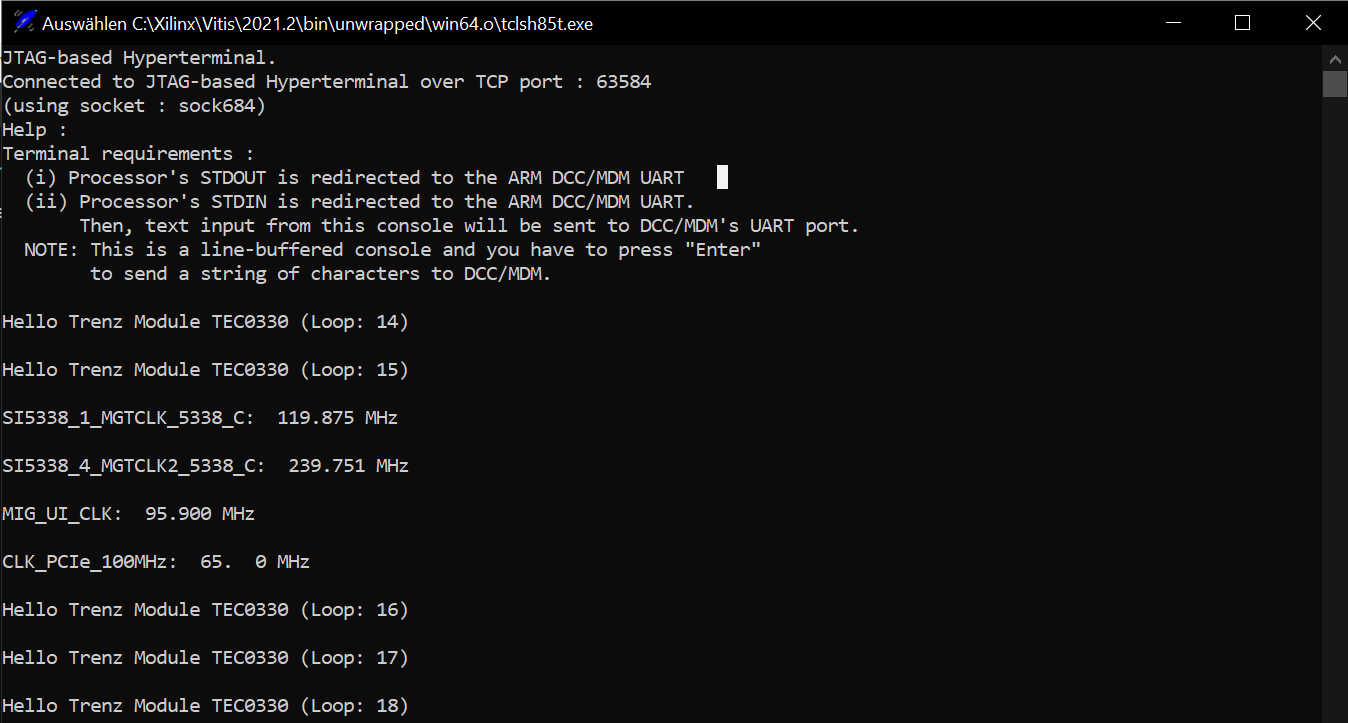

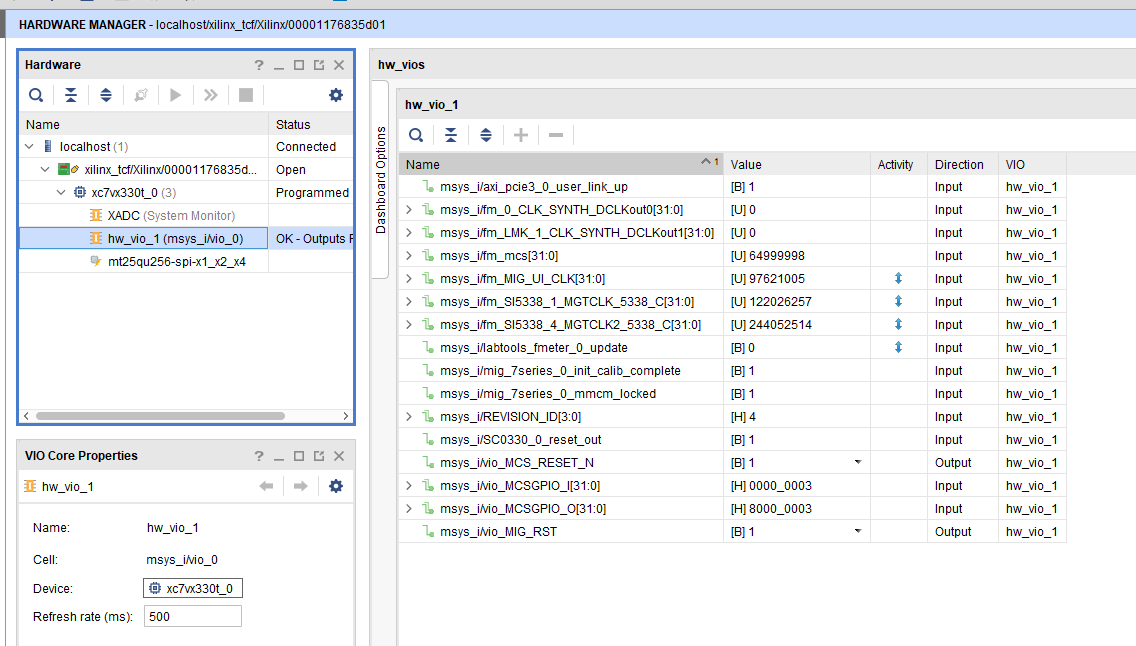

TEC0330 SI5338 Configuration, DDR Configuration and PCIe Core Example Design.

Refer to http://trenz.org/tec0330-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

Revision History

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_DRH |

|---|---|

| title | Design Revision History |

...

...

...

...

- initial release

...

...

| anchor | Table_KI |

|---|---|

| title | Known Issues |

...

Disable ECC:

- for Block Design MIG with AXI Interface, create 64Bit MIG

- for RTL MIG with Native Interface, disable ECC on MIG configuration and use 72Bit for Data

...

Requirements

Software

...

| hidden | true |

|---|---|

| id | Comments |

Notes :

...

...

...

...

...

...

...

Hardware

...

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

Design supports following modules:

- list of software which was used to generate the design

...

...

...

- DDR configured for AW24P7228BLK0M (8GB)

Design supports following carriers:

...

...

- TE0790 with TE0791 for CPLD or FPGA

- Xilinx compatible JTAG programmer for FPGA

...

- for example:

- AW24P7228BLK0M (max. 8GB)

Content

...

Additional HW Requirements:

...

| anchor | Table_AHW |

|---|---|

| title | Additional Hardware |

- content of the zip file

For general structure and of the reference design, see Project Delivery - Xilinx devices

...

...

...

...

...

...

...

...

...

Prebuilt

...

| hidden | true |

|---|---|

| id | Comments |

Notes :

...

...

...

...

File

...

File-Extension

...

Description

...

Debian SD-Image

...

*.img

...

Debian Image for SD-Card

...

MCS-File

...

*.mcs

...

Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only)

...

MMI-File

...

*.mmi

...

File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only)

...

...

SREC-File

...

*.srec

...

...

...

...

...

...

...

MCS-File

...

*.mcs

...

Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only)

...

MMI-File

...

*.mmi

...

File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only)

...

SREC-File

...

*.srec

...

Converted Software Application for MicroBlaze Processor Systems

Download

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

Reference Design is available on:

Design Flow

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Note |

|---|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

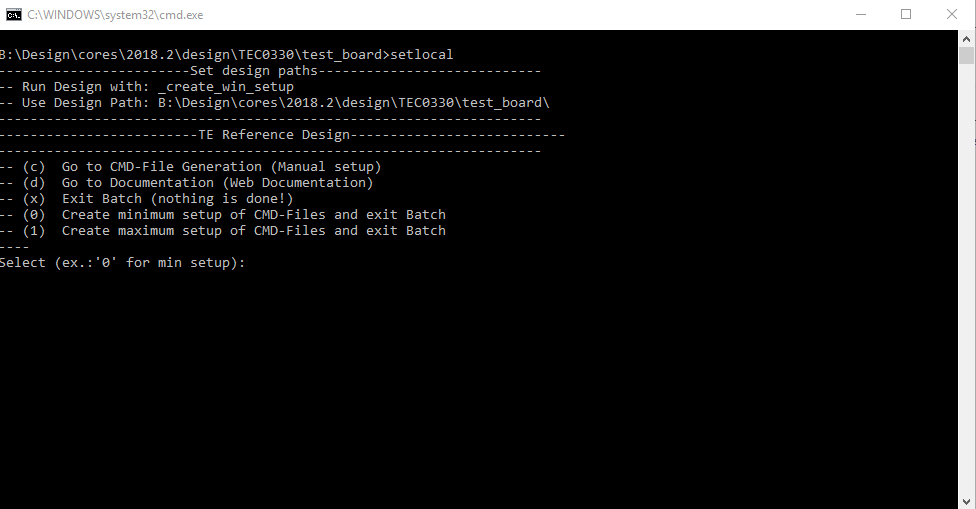

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter for minimum setup

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Generate Programming Files with HSI/SDK

- Start with TE Scripts on Vivado TCL: TE::sw_run_hsi

(optional) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk to generate files manually

Note: See SDK Projects - (optional ) Copy "prebuilt\software\<short dir>\srec_spi_bootloader.elf" into "\firmware\microblaze_0" (replace shipped one) and regenerate design again (HW (Step5)+SW(Step6 only a.))

- (optional ) for SI5338 reprogramming with MCS:

- Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk to generate files manually

- New Application with Project Name "SCU" and Processor "microblaze_mcs_0_microblaze_I", select TE Application "SCU-Firmware"

- Create elf file

- Copy "workspace\sdk\SCU\<release or debug>\SCU.elf" into "\firmware\microblaze_mcs_0" (replace shipped one) and regenerate design again (HW (Step5)+SW(Step6 only a.))

- Start with TE Scripts on Vivado TCL: TE::sw_run_hsi

Launch

Programming

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

...

...

...

...

...

...

...

...