Page History

Test Platforms Supported by the design

| SoM | Base | Vivado | Status |

|---|---|---|---|

| TE0720-02-2IF | TE0701-05 | 2014.4 | released |

| TE0715-15 | TE0701-05 | 2015.2 | planned |

Block Design

IP Cores used

| Vendor | License | Description | |

|---|---|---|---|

| axis_fb_conv | TE | Free | Remap axi_vdma into linux framebuffer color format for axi4s_video_out |

| video_io_to_hdmi | TE | Free | |

| axi_vdma | Xilinx | Free | |

| axi4s_video_out | Xilinx | Free | |

| VTC | Xilinx | Free | Video timing generator, with AXI Control. Can be converted to fixed timing version to save resources |

| TPG | Xilinx | Free | Test pattern generator. Optional, can be removed from design |

Software support

All initialization is done in FSBL, there is no extra software or drivers needed later. Linux simple framebuffer has to be enabled in devicetree.

...

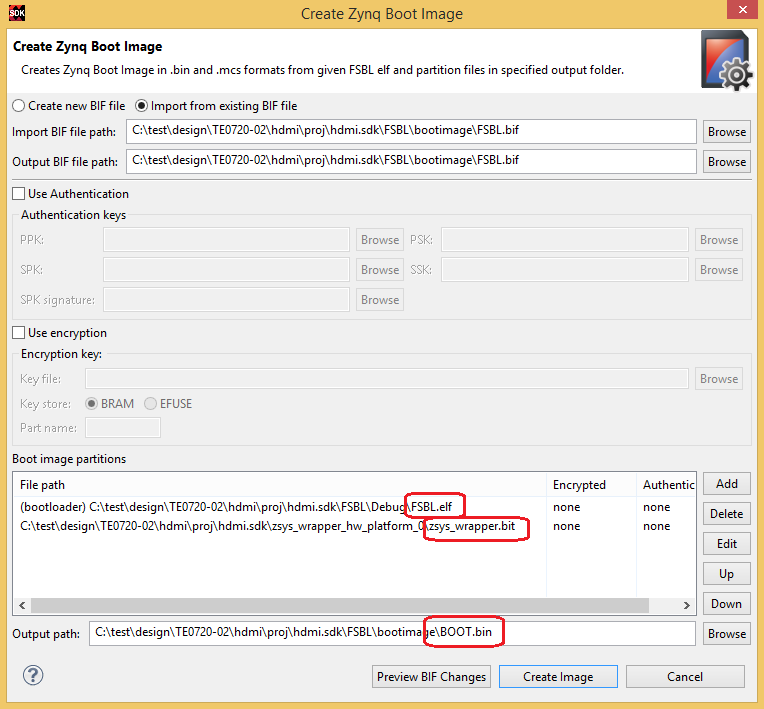

Use the .elf file to create boot image.

Image format

This design configures the framebuffer in Linux simple framebuffer format a8r8g8b8, screen size 1280x720. Images can be converted to this format with ImageMagick.

...

Overview

Content Tools