...

Key Features

- Xilinx Zynq-7000 XC7Z035, XC7Z045 or XC7Z100 SoC

- Rugged for shock and high vibration

- Large number of configurable I/Os are provided via rugged high-speed stacking strips

- Dual ARM Cortex-A9 MPCore

- 1 GByte RAM (32bit wide DDR3)

- 32 MByte QSPI Flash memory

- 2 x Gigabit (10/100/1000 Mbps) Ethernet transceiver PHY

- 4 GByte eMMC (optional up to 64 GByte)

- 2 x MAC-address EEPROMs

- Optional 2x 64 MByte HyperFLASH or 2x 8 MByte HyperRAM (max 2x 32 MByte HyperRAM)

- Temperature compensated RTC (real-time clock)

- Si5338A programmable quad PLL clock generator for GTX transceiver clocks

- Plug-on module with 3 x 160-pin high-speed strips

- 16 GTX high-performance transceiver

- 2x GT transceiver clock inputs

- 254 FPGA I/O's (125 LVDS pairs)

- On-board high-efficiency switch-mode DC-DC converters

- System management

- eFUSE bit-stream encryption

- AES bit-stream encryption

- Evenly-spread supply pins for good signal integrity

- User LED

...

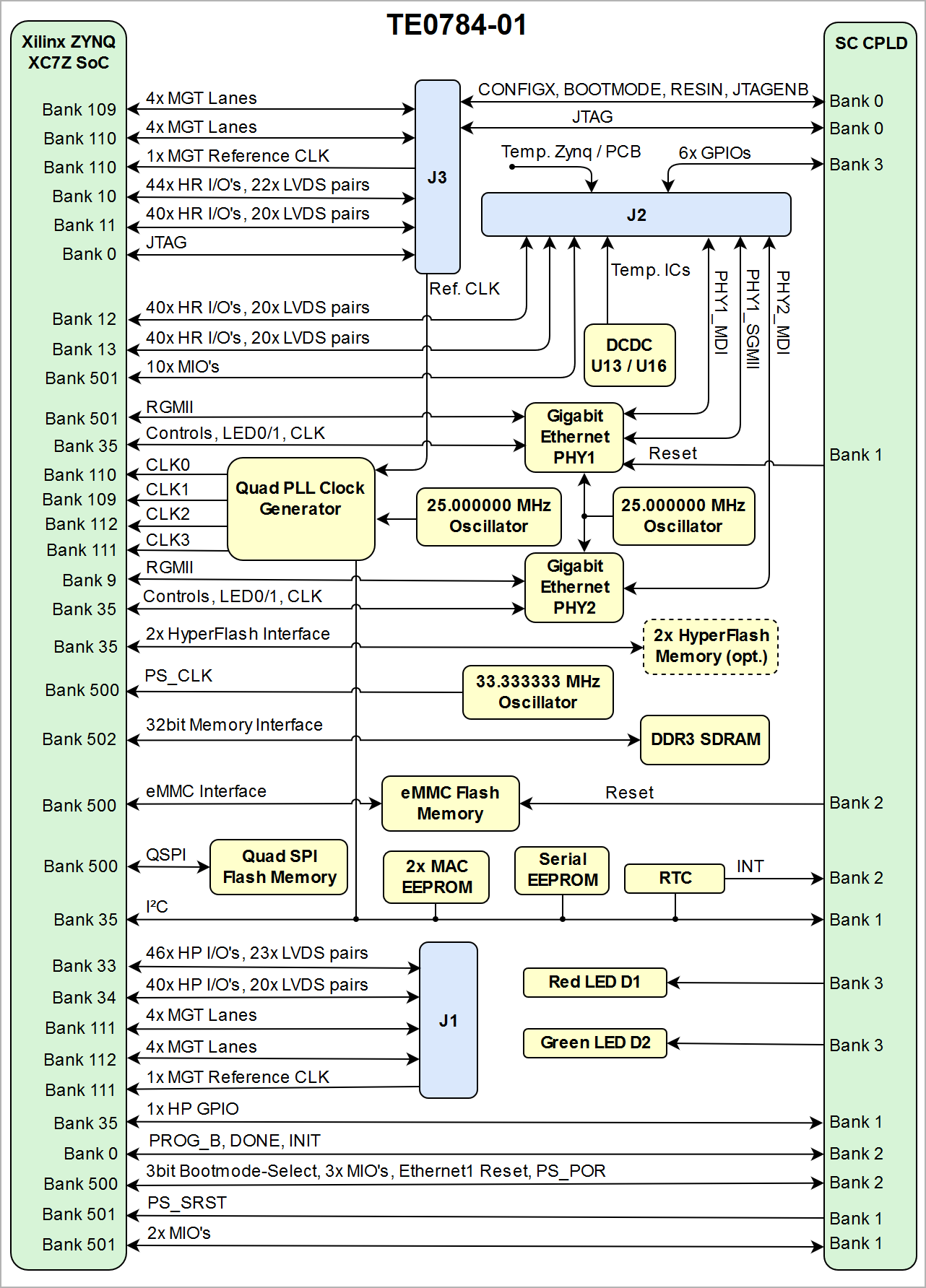

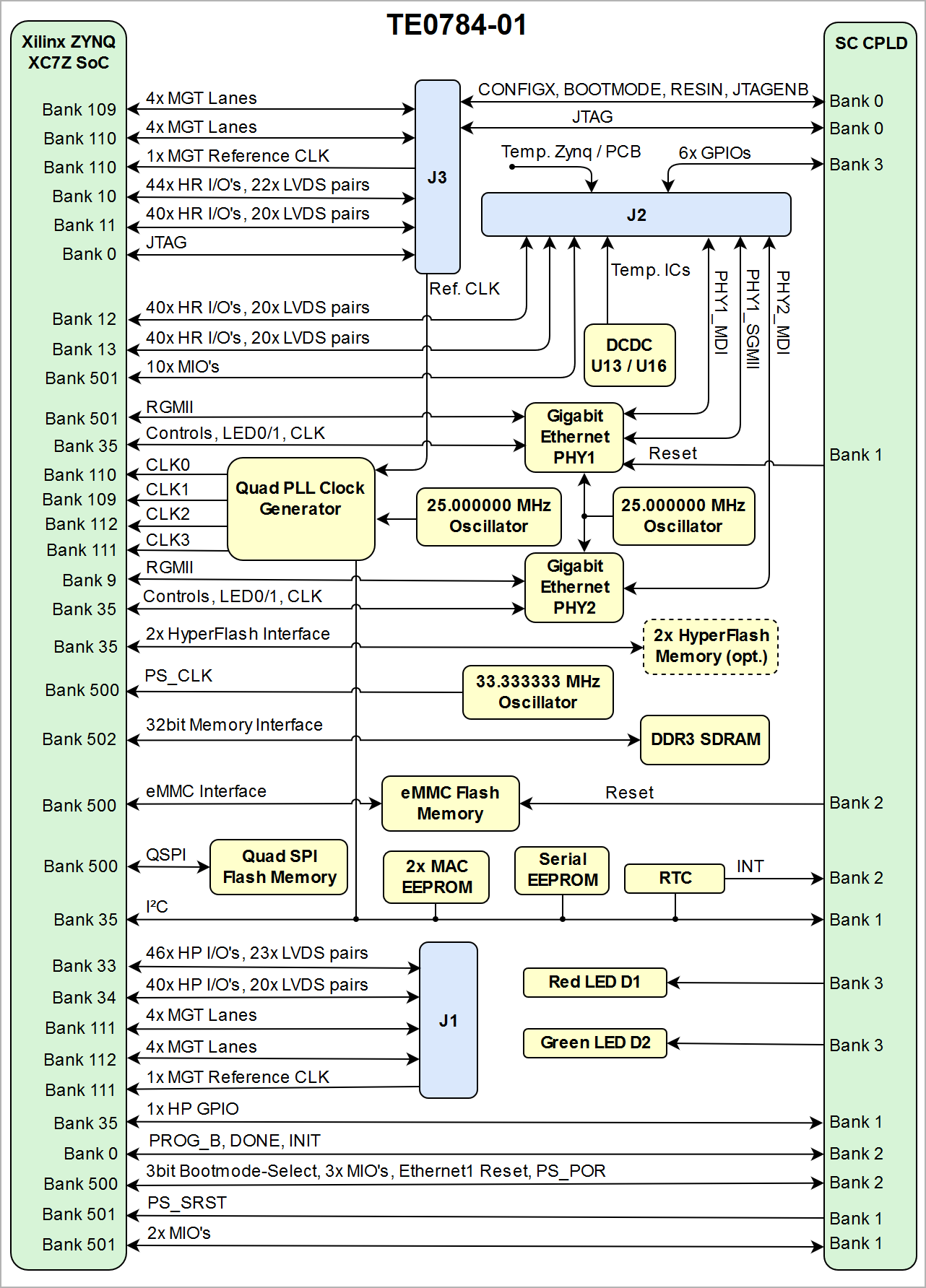

| Scroll Title |

|---|

| anchor | Figure_1 |

|---|

| title | Figure 1: TE0782-02 block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 34 |

|---|

| diagramName | TE0784-01 block diagram |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 629641 |

|---|

|

|

| Scroll Only |

|---|

|

|

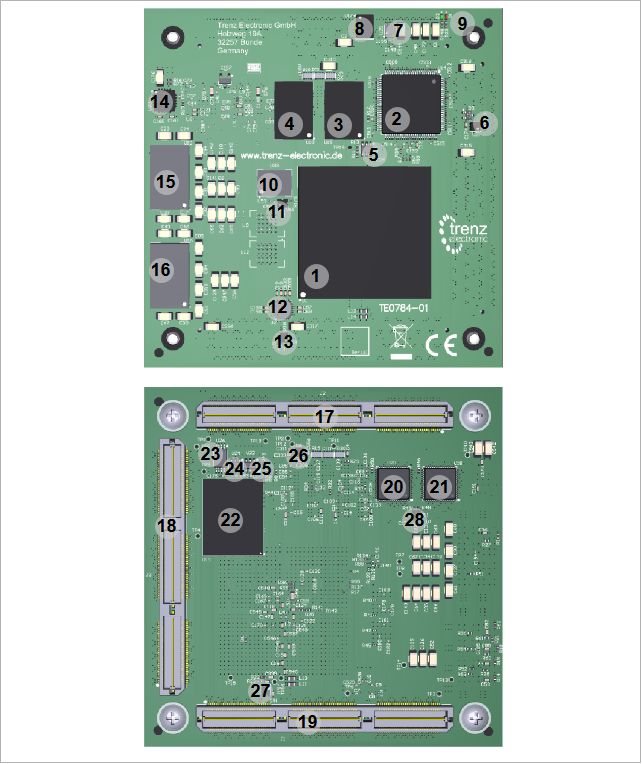

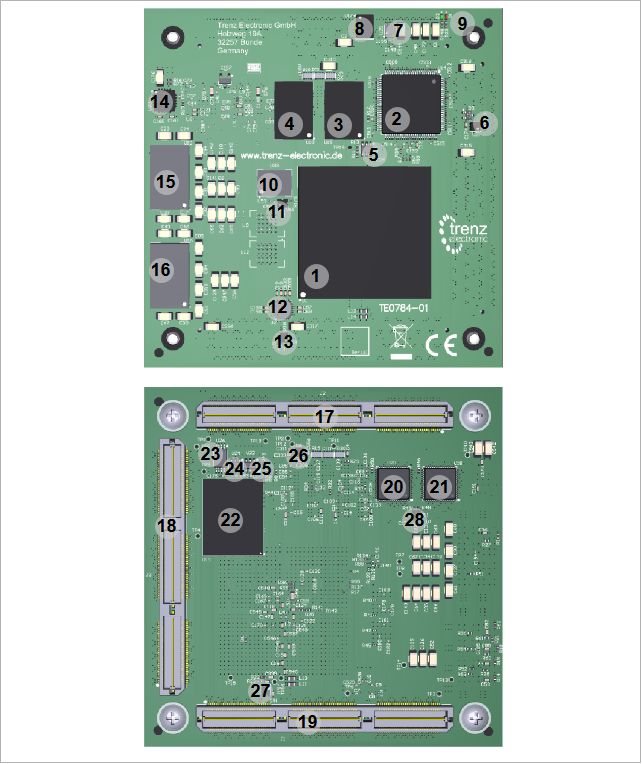

Main Components

| Scroll Title |

|---|

| anchor | Figure_2 |

|---|

| title | Figure 2: TE0782-02 main components |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 13 |

|---|

| diagramName | TE0784-01 main components |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641642 |

|---|

|

|

| Scroll Only |

|---|

Image Removed Image Removed

|

|

Fotos müssen ausgetauscht werden, hier noch TE0782 als Platzhalter

- Xilinx Zynq-7000 SoC, U1

- Lattice Semiconductor MachXO2 1200HC CPLD, U14

- 4Gbit DDR3L SDRAM, U19

- 4Gbit DDR3L SDRAM, U10

- TI TPS3106 voltage monitor circuit, U4

- TI TPS78018 LDO, U21

- I²C voltage translator, U25

- Intersil ISL12020MIRZ Real Time Clock, U17SiTime

- SiT8008 52.000000 MHz oscillator, U7Red LED D1, Green LED D2

- 32 MByte QSPI Flash memory, U38

- SiTime SiT8008 33.333333 MHz oscillator, U61

- SI5338A programmable quad PLL clock generator, U2

- SiTime SiT8008 25.000000 MHz oscillator, U3

- TPS74801 LDO @1.5V, U23

- LT quad 4A PowerSoC DC-DC converter (@1.0V), U13

- LT quad 4A PowerSoC DC-DC converter (@3.3V, @1,8V, @1.2V_MGT, @1.0V_MGT), U16

- Samtec ASP-122952-01 160-pin stacking strip (2 rows a 80 positions), J2

- Samtec ASP-122952-01 160-pin stacking strip (2 rows a 80 positions), J3

- Samtec ASP-122952-01 160-pin stacking strip (2 rows a 80 positions), J1

- Marvell Alaska 88E1512 Gigabit Ethernet PHY, 20

- Marvell Alaska 88E1512 Gigabit Ethernet PHY, U18

- Micron Technology 4 GByte eMMC, U15

- Microchip 128Kbit I²C EEPROM, U26

- Microchip 2Kbit I²C MAC EEPROM, U24

- Microchip 2Kbit I²C MAC EEPROM, U22

- TPS51206 DDR reference voltage and termination regulator, U6

- TPS799 LDO @1.8V_MGT, U5

- SiTime SiT8008 25.000000 MHz oscillator, U11

...

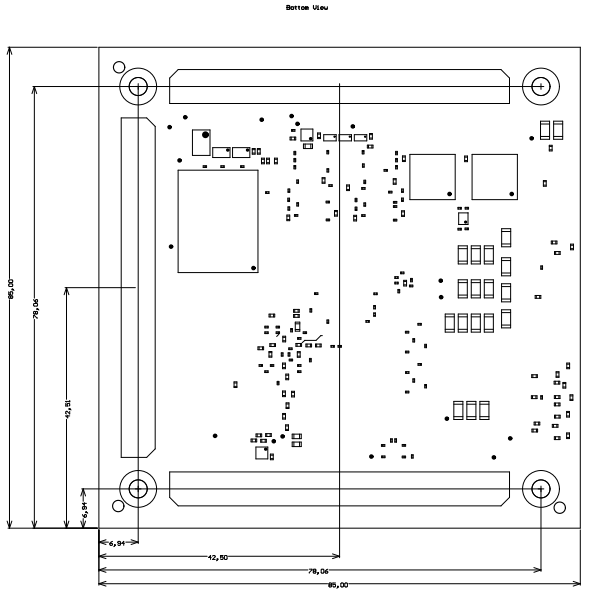

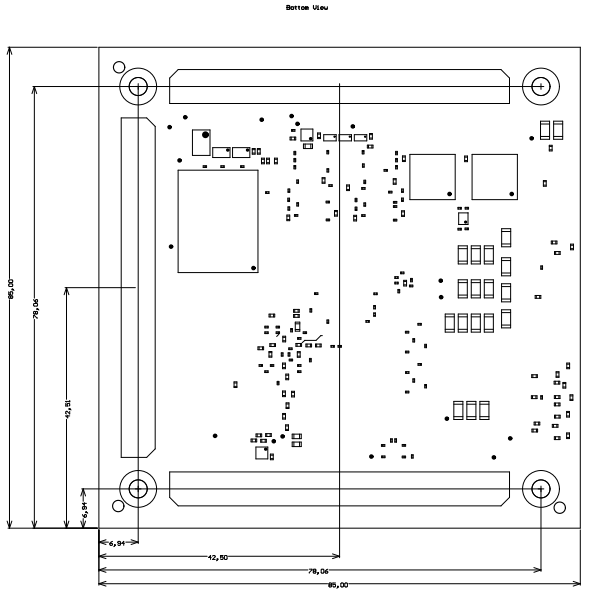

| Scroll Title |

|---|

| anchor | Figure_6 |

|---|

| title | Figure 6: Module physical dimensions drawing |

|---|

|

Image Added Image Added

|

Revision History

Hardware Revision History

...

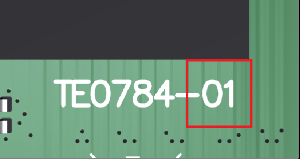

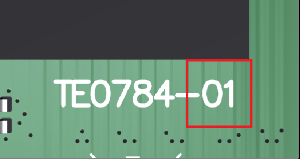

| Scroll Title |

|---|

| anchor | Figure_7 |

|---|

| title | Figure 7: Module hardware revision number |

|---|

|

Image Added Image Added

|

Document Change History

| HTML |

|---|

<!--

Generate new entry:

1.add new row below first

2.Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number

3.Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description.

--> |

...