Page History

Template Revision 2.6 - on construction

...

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

...

| hidden | true |

|---|---|

| id | Comments |

Important General Note:

...

Export PDF to download, if vivado revision is changed!

Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro

...

Figure template (note: inner scroll ignore/only only with drawIO object):

...

| anchor | Figure_xyz |

|---|---|

| title | Text |

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, use |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

...

Table template:

- Layout macro can be use for landscape of large tables

- Set column width manually(can be used for small tables to fit over whole page) or leave empty (automatically)

...

| anchor | Table_xyz |

|---|---|

| title | Text |

...

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of contents

|

Overview

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Refer to http://trenz.org/te0xyz-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

Revision History

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_DRH |

|---|---|

| title | Design Revision History |

...

- initial release

Release Notes and Know Issues

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_KI |

|---|---|

| title | Known Issues |

...

...

...

...

...

Requirements

...

| anchor | Table_SW |

|---|---|

| title | Software |

...

Hardware

- list of software which was used to generate the design

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

Design supports following modules:

- list of software which was used to generate the design

...

...

...

TE0802-02-2AEV2-A

...

Design supports following carriers:

...

| anchor | Table_HWC |

|---|---|

| title | Hardware Carrier |

...

Additional HW Requirements:

...

| anchor | Table_AHW |

|---|---|

| title | Additional Hardware |

...

- content of the zip file

For general structure and of the reference design, see Project Delivery - Xilinx devices

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

File

...

File-Extension

...

Description

...

Debian SD-Image

...

*.img

...

Debian Image for SD-Card

...

MCS-File

...

*.mcs

...

Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only)

...

MMI-File

...

*.mmi

...

File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only)

...

...

SREC-File

...

*.srec

...

...

...

...

File

...

File-Extension

...

Description

...

Download

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

Reference Design is available on:

Design Flow

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Note |

|---|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Create Linux (uboot.elf and image.ub) with exported HDF

- HDF is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

- HDF is exported to "prebuilt\hardware\<short name>"

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\<ddr size>" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

- Run on Vivado TCL: TE::sw_run_hsi

Launch

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

Optional for Boot.bin on QSPI Flash and image.ub on SD.

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0802" possible - Copy image.ub on SD-Card

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to QSPI-Boot and insered SD.

- Depends on Carrier, see carrier TRM.

SD

- Copy image.ub, Boot.bin and init.sh(optional on /misc/sd) on SD-Card.

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to SD-Boot.

- Depends on Carrier, see carrier TRM.

- Insert SD-Card in SD-Slot.

JTAG

Not used on this Example.

Usage

- Prepare HW like described on section 43680037

- Connect UART USB (most cases same as JTAG)

- Connect Monitors, ETH, M2...

- Select SD Card as Boot Mode (or QSPI - depending on step 1)

Note: See TRM of the Carrier, which is used. - Power On PCB

Note: 1. Zynq Boot ROM loads FSBL from SD into OCM, 2. FSBL loads U-boot from SD into DDR, 3. U-boot load Linux from SD into DDR

Linux

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:- User Name: root

- Password: root

- You can use Linux shell now.

- I2C 0 Bus type: i2cdetect -y -r 0

- RTC check: dmesg | grep rtc

- ETH0 works with udhcpc

- USB type "lsusb" or connect USB device

- PCIe (M2 SSD) type "lspci"

- VGA connect Monitor (it show test screen)

- DP: second console will be shown on the monitor, when boot process is finished. (conneced keyboard to USB, to interact with the second console)

- Audio type: aplay /run/media/mmcblk0p1/<filename>.wav Note: DP must be connected to activate audio drivers. Use .wav or other aplay supported formate

- Option Features

- Webserver to get access to Zynq

- insert IP on web browser to start web interface

- init.sh scripts

- add init.sh script on SD, content will be load automatically on startup (template included in ./misc/SD)

- add init.sh script on SD, content will be load automatically on startup (template included in ./misc/SD)

- Webserver to get access to Zynq

- All button cross will be reset LEDs with values from DIP

- LCD is connected to counter

Vivado HW Manager

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

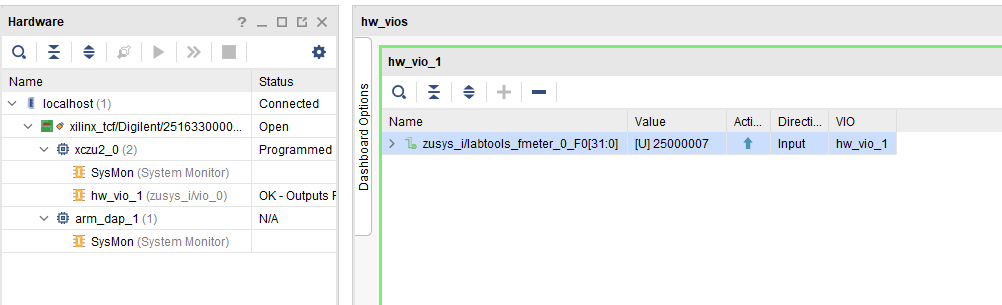

Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder)

- Monitoring:

- 25MHz CLK Set radix from VIO signals to unsigned integer. Note: Frequency Counter is inaccurate and displayed unit is Hz)

- 25MHz CLK Set radix from VIO signals to unsigned integer. Note: Frequency Counter is inaccurate and displayed unit is Hz)

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

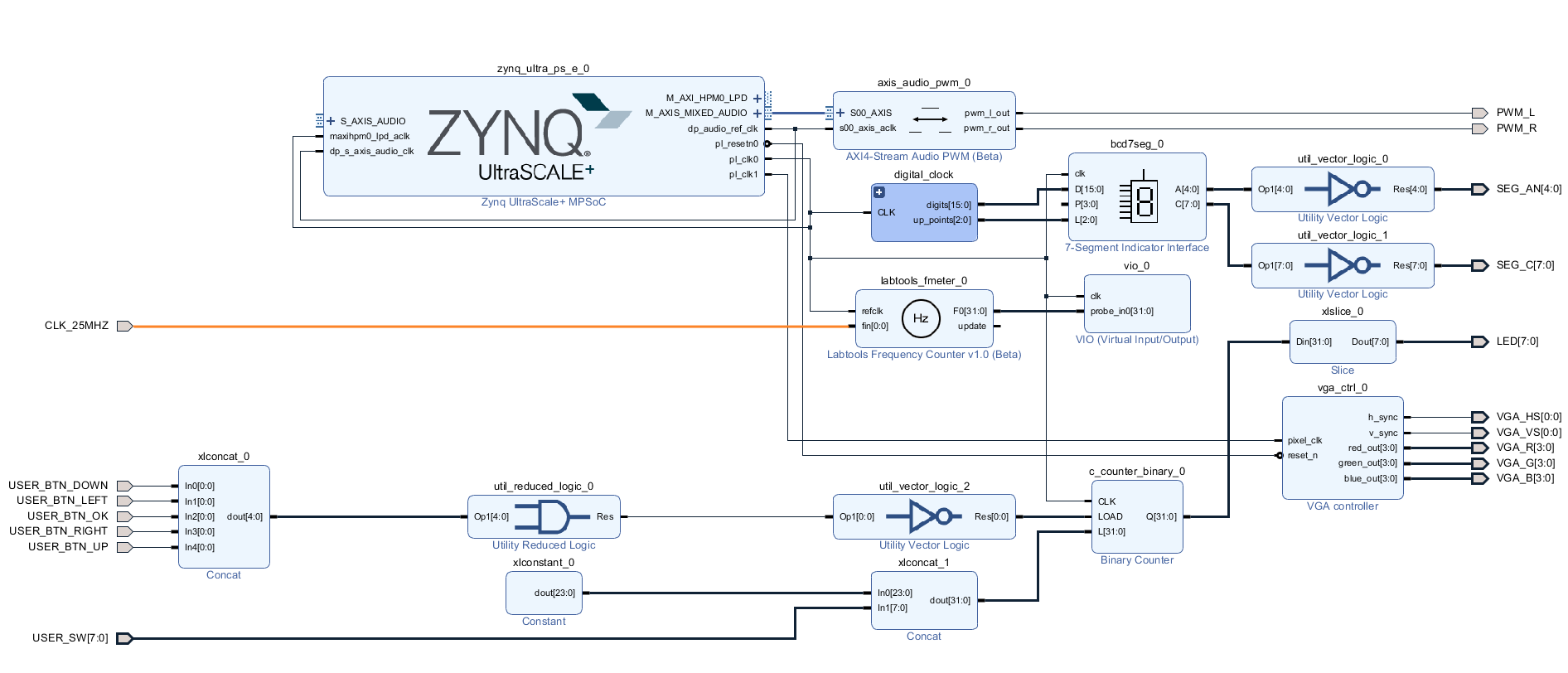

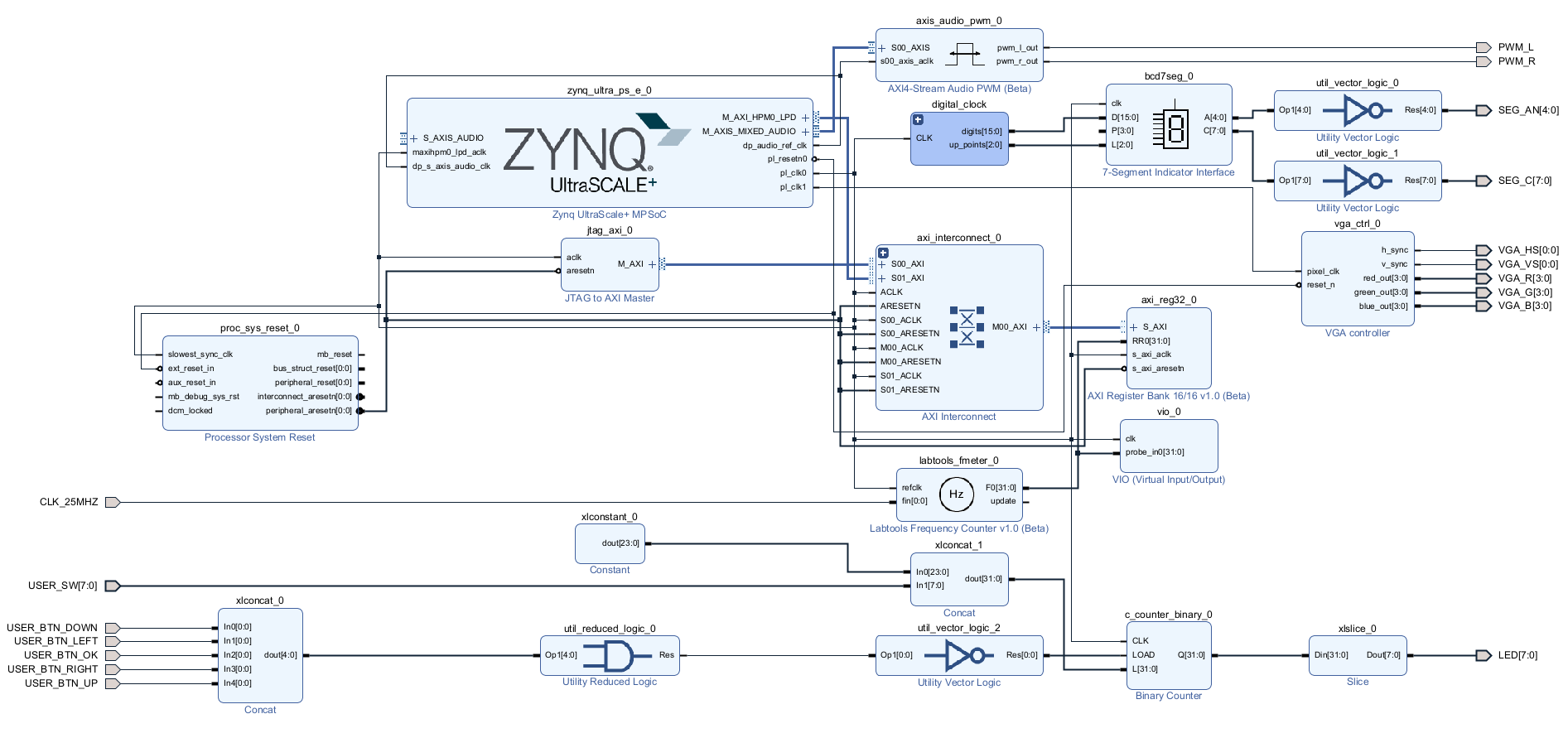

System Design - Vivado

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Block Design

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

...

...

Note:

optional for Zynq / ZynqMP only

- add basic PS configuration

Activated interfaces:

...

| anchor | Table_PSI |

|---|---|

| title | PS Interfaces |

...

Constrains

Basic module constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLNONE [current_design] |

Design specific constrain

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property PACKAGE_PIN E3 [get_ports PWM_L]

set_property PACKAGE_PIN F4 [get_ports PWM_R]

set_property IOSTANDARD LVCMOS18 [get_ports PWM_*]

#set_property PACKAGE_PIN T2 [ get_ports USER_BTN_DOWN ]

#set_property PACKAGE_PIN U2 [ get_ports USER_BTN_UP ]

#set_property PACKAGE_PIN U1 [ get_ports USER_BTN_RIGHT ]

#set_property PACKAGE_PIN R1 [ get_ports USER_BTN_LEFT ]

#set_property PACKAGE_PIN T1 [ get_ports USER_BTN_OK ]

#set_property IOSTANDARD LVCMOS18 [ get_ports USER_BTN_* ]

set_property PACKAGE_PIN P3 [get_ports {USER_SW[0]}]

set_property PACKAGE_PIN P2 [get_ports {USER_SW[1]}]

set_property PACKAGE_PIN M1 [get_ports {USER_SW[2]}]

set_property PACKAGE_PIN L1 [get_ports {USER_SW[3]}]

set_property PACKAGE_PIN K1 [get_ports {USER_SW[4]}]

set_property PACKAGE_PIN J2 [get_ports {USER_SW[5]}]

set_property PACKAGE_PIN M4 [get_ports {USER_SW[6]}]

set_property PACKAGE_PIN M5 [get_ports {USER_SW[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports USER_SW*]

set_property PACKAGE_PIN U2 [get_ports {USER_BTN_UP}]

set_property PACKAGE_PIN U1 [get_ports {USER_BTN_RIGHT}]

set_property PACKAGE_PIN T2 [get_ports {USER_BTN_DOWN}]

set_property PACKAGE_PIN R1 [get_ports {USER_BTN_LEFT}]

set_property PACKAGE_PIN T1 [get_ports {USER_BTN_OK}]

set_property IOSTANDARD LVCMOS18 [get_ports USER_BTN*]

set_property PACKAGE_PIN P1 [get_ports {LED[0]}]

set_property PACKAGE_PIN N2 [get_ports {LED[1]}]

set_property PACKAGE_PIN M2 [get_ports {LED[2]}]

set_property PACKAGE_PIN L2 [get_ports {LED[3]}]

set_property PACKAGE_PIN J1 [get_ports {LED[4]}]

set_property PACKAGE_PIN H2 [get_ports {LED[5]}]

set_property PACKAGE_PIN L4 [get_ports {LED[6]}]

set_property PACKAGE_PIN L3 [get_ports {LED[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports LED*]

set_property PACKAGE_PIN F2 [get_ports {VGA_R[0]}]

set_property PACKAGE_PIN F1 [get_ports {VGA_R[1]}]

set_property PACKAGE_PIN G2 [get_ports {VGA_R[2]}]

set_property PACKAGE_PIN G1 [get_ports {VGA_R[3]}]

set_property PACKAGE_PIN C2 [get_ports {VGA_G[0]}]

set_property PACKAGE_PIN D2 [get_ports {VGA_G[1]}]

set_property PACKAGE_PIN D1 [get_ports {VGA_G[2]}]

set_property PACKAGE_PIN E1 [get_ports {VGA_G[3]}]

set_property PACKAGE_PIN A3 [get_ports {VGA_B[0]}]

set_property PACKAGE_PIN A2 [get_ports {VGA_B[1]}]

set_property PACKAGE_PIN B2 [get_ports {VGA_B[2]}]

set_property PACKAGE_PIN B1 [get_ports {VGA_B[3]}]

set_property PACKAGE_PIN B7 [get_ports {VGA_VS[0]}]

set_property PACKAGE_PIN A6 [get_ports {VGA_HS[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_B[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_B[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_B[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_B[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_G[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_G[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_G[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_G[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {VGA_HS[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_R[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_R[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_R[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {VGA_R[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {VGA_VS[0]}]

set_property PACKAGE_PIN J3 [get_ports CLK_25MHZ]

set_property IOSTANDARD LVCMOS18 [get_ports CLK_25MHZ]

# SEG_C[0] = SEG_CA

set_property PACKAGE_PIN E4 [get_ports {SEG_C[0]}]

set_property PACKAGE_PIN D3 [get_ports {SEG_C[1]}]

set_property PACKAGE_PIN N5 [get_ports {SEG_C[2]}]

set_property PACKAGE_PIN P5 [get_ports {SEG_C[3]}]

set_property PACKAGE_PIN N4 [get_ports {SEG_C[4]}]

set_property PACKAGE_PIN C3 [get_ports {SEG_C[5]}]

set_property PACKAGE_PIN N3 [get_ports {SEG_C[7]}]

set_property PACKAGE_PIN R5 [get_ports {SEG_C[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports SEG_C*]

set_property PACKAGE_PIN A8 [get_ports {SEG_AN[0]}]

set_property PACKAGE_PIN A9 [get_ports {SEG_AN[1]}]

set_property PACKAGE_PIN B9 [get_ports {SEG_AN[2]}]

set_property PACKAGE_PIN A7 [get_ports {SEG_AN[3]}]

set_property PACKAGE_PIN B6 [get_ports {SEG_AN[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports SEG_AN*]

|

Software Design - SDK/HSI

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

For SDK project creation, follow instructions from:

Application

...

...

...

FPGA Example

scu

MCS Firmware to configure SI5338 and Reset System.

srec_spi_bootloader

TE modified 2018.3 SREC

Bootloader to load app or second bootloader from flash into DDR

Descriptions:

- Modified Files: blconfig.h, bootloader.c

- Changes:

- Add some console outputs and changed bootloader read address.

- Add bugfix for 2018.2 qspi flash

xilisf_v5_11

TE modified 2018.3 xilisf_v5_11

- Changed default Flash type to 5.

----------------------------------------------------------

Zynq Example:

zynq_fsbl

TE modified 2018.3 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

Module Specific:

- Add Files: all TE Files start with te_*

- READ MAC from EEPROM and make Address accessible by UBOOT (need copy defines on uboot platform-top.h)

- CPLD access

- Read CPLD Firmware and SoC Type

- Configure Marvell PHY

zynq_fsbl_flash

TE modified 2018.3 FSBL

General:

- Modified Files: main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

ZynqMP Example:

----------------------------------------------------------

zynqmp_fsbl

TE modified 2018.3 FSBL

General:

- Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c(search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device Name

Module Specific:

- Add Files: all TE Files start with te_*

- Si5338 Configuration

- ETH+OTG Reset over MIO

zynqmp_fsbl_flash

TE modified 2018.3 FSBL

General:

- Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

zynqmp_pmufw

Xilinx default PMU firmware.

----------------------------------------------------------

General Example:

hello_te0820

Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output.

u-boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

Template location: ./sw_lib/sw_apps/

zynqmp_fsbl

TE modified 2018.3 FSBL

General:

- Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c(search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device Name

Module Specific:

- Add Files: all TE Files start with te_*

- ETH+OTG+SSD Reset over MIO

zynqmp_fsbl_flash

TE modified 2018.3 FSBL

General:

- Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

zynqmp_pmufw

Xilinx default PMU firmware.

Software Design - PetaLinux

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

For PetaLinux installation and project creation, follow instructions from:

Config

Start with petalinux-config or petalinux-config --get-hw-description

Changes:

- CONFIG_SUBSYSTEM_ETHERNET_PSU_ETHERNET_3_MAC=""

U-Boot

Start with petalinux-config -c u-boot

Changes:

CONFIG_ENV_IS_NOWHERE=y

CONFIG_ENV_IS_IN_SPI_FLASH is not set

Change platform-top.h:

| Code Block | ||

|---|---|---|

| ||

#include <configs/platform-auto.h>

#define CONFIG_SYS_BOOTM_LEN 0xF000000

#define DFU_ALT_INFO_RAM \

"dfu_ram_info=" \

"setenv dfu_alt_info " \

"image.ub ram $netstart 0x1e00000\0" \

"dfu_ram=run dfu_ram_info && dfu 0 ram 0\0" \

"thor_ram=run dfu_ram_info && thordown 0 ram 0\0"

#define DFU_ALT_INFO_MMC \

"dfu_mmc_info=" \

"set dfu_alt_info " \

"${kernel_image} fat 0 1\\\\;" \

"dfu_mmc=run dfu_mmc_info && dfu 0 mmc 0\0" \

"thor_mmc=run dfu_mmc_info && thordown 0 mmc 0\0"

/*Required for uartless designs */

#ifndef CONFIG_BAUDRATE

#define CONFIG_BAUDRATE 115200

#ifdef CONFIG_DEBUG_UART

#undef CONFIG_DEBUG_UART

#endif

#endif

/*Define CONFIG_ZYNQMP_EEPROM here and its necessaries in u-boot menuconfig if you had EEPROM memory. */

#define CONFIG_ZYNQMP_EEPROM

#ifdef CONFIG_ZYNQMP_EEPROM

#define CONFIG_SYS_I2C_EEPROM_ADDR_LEN 1

#define CONFIG_CMD_EEPROM

#define CONFIG_ZYNQ_EEPROM_BUS 1

#define CONFIG_ZYNQ_GEM_EEPROM_ADDR 0x50

#define CONFIG_ZYNQ_GEM_I2C_MAC_OFFSET 0xFA

#endif

|

Device Tree

...

| language | js |

|---|

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

CONFIG_CPU_FREQ is not set (only needed to fix JTAG Debug issue)

...

...

...

...

...

...

...

...

Applications

startup

Script App to load init.sh from SD Card if available.

...

...

...

...

...

...

...

...

| Page info | ||||

|---|---|---|---|---|

|