Page History

...

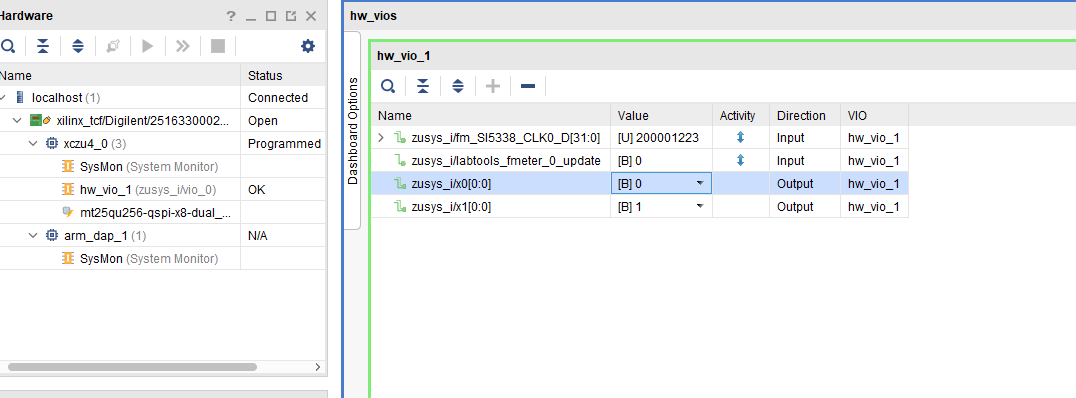

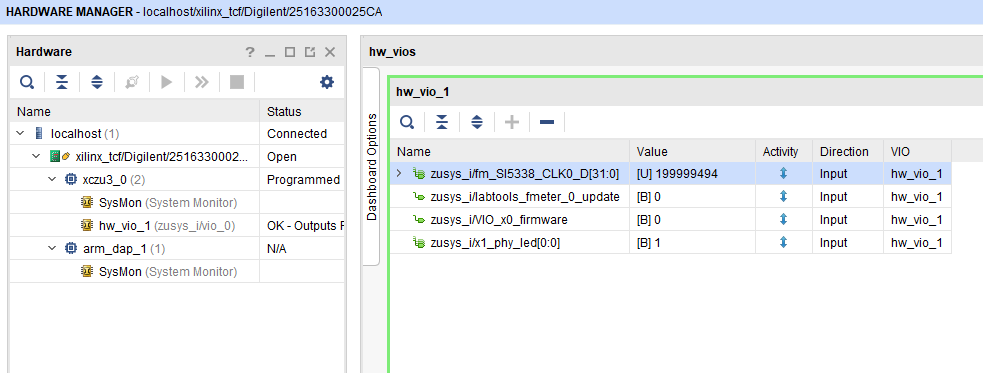

ZynqMP PS Design with Linux Example and simple frequency counter to measure SI5338 Reference CLK with Vivado HW-Manager. Only for use with TEF1002 Carrier.

Wiki Resources page: http://trenz.org/te0820-info

...

| Excerpt |

|---|

|

...

| Scroll Title | |||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||

|

...

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

...

For general structure and of the reference design, see Project Delivery - Xilinx AMD devices.

Design Sources

| Scroll Title | ||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||

|

...

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

- Xilinx AMD Development Tools#XilinxSoftware-BasicUserGuides

- Vivado Projects - TE Reference Design

- Project Delivery.

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

...

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging.

Note: Depending on CPLD Firmware and Boot Mode settings, QSPI boot with Linux image on SD or complete SD Boot is possible.

...

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0820" possible - Copy image.ub on SD-Card

- use files from (<project foler>/_binaries_<Artikel Name>)/boot_linux from generated binary folder,see: Get prebuilt boot binaries

- or use prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Insert SD-Card

...

- Prepare HW like described on section TEF1002 Getting Started

- for PCIe insert TEF1002 in PCIe slot and us PC internalconnect PC PCIe 6 pin power connector

- Connect JTAG/UART USB

- Connect SATA device

- Select SD Card as Boot Mode (S3-1: OFF)

- Power On PCB

Note: 1. ZynqMP Boot ROM loads PMU Firmware and FSBL from SD/QSPI Flash into OCM, 2. FSBL loads ATF(bl31.elf) and U-boot from SD into DDR, 3. U-boot load Linux from SD into DDR

...

PCB REV03 Design:

- User LED, see: TE0820 CPLD#LED

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

PCB REV01, REV02 Design:

- PHY LEDS, see: TE0820-REV01_REV02 CPLD#X0/X1Pin

- CPLD Firmware, see: TE0820-REV01_REV02 CPLD#X0/X1Pin

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

...

For SDK project creation, follow instructions from:

Application

| Page properties | ||||

|---|---|---|---|---|

| ||||

---------------------------------------------------------- FPGA Example todo.. ---------------------------------------------------------- Zynq Example: zynq_fsblTE modified 2018.3 FSBL General:

Module Specific:

zynq_fsbl_flashTE modified 2018.3 FSBL General:

ZynqMP Example: ---------------------------------------------------------- zynqmp_fsblTE modified 2018.3 FSBL General:

Module Specific:

zynqmp_fsbl_flashTE modified 2018.3 FSBL General:

zynqmp_pmufwXilinx default PMU firmware. ---------------------------------------------------------- General Example: hello_te0820Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output. u-bootU-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin. |

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

| Note: |

SI5338

File location <design name>/misc/Si5338/Si5338-*.slabtimeproj

General documentation how you work with these project will be available on Si5338

Appx. A: Change History and Legal Notices

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||

|

Legal Notices

| Include Page | ||||

|---|---|---|---|---|

|

...