...

| Scroll Title |

|---|

| anchor | Table_DRH |

|---|

| title | Design Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Vivado | Project Built | Authors | Description |

|---|

| 2020-0206-1303 | 2019.2 | TEB0911-test_board_noprebuilt-vivado_2019.2-build_512_2020021311451320200603131549.zip

TEB0911-test_board_noprebuilt-vivado_2019.2-build_512_2020021311273020200603131603.zip | John Hartfiel | - 2019.2 update

- new assembly variants

- Vitis support

- FSBL SI programming procedure update

- petalinux device tree and u-boot update

- reduced DDR speed (see Xilinx Datasheet)

| - bugfix usb3

- add nvme driver

| | 2020-03-25 | 2019 | 2018-11-26 | 2018.2 | TEB0911-test_board_noprebuilt-vivado_20182019.2-build_038_2018112613262220200325084706.zip

TEB0911-test_board-vivado_20182019.2-build_038_2018112613260720200325084633.zip | John Hartfiel | - new assembly variant

- add init.sh

| 2018-07-20 | 2018 | | 2020-02-24 | 2019.2 | TEB0911-test_board_noprebuilt-vivado_ | 20182019.2-build_ | 026_ | 2018071915344320200224080741.zip

TEB0911-test_board-vivado_ | 20182019.2-build_ | 026_ | 2018071915342920200224080728.zip | John Hartfiel | |

|

Release Notes and Know Issues

| Page properties |

|---|

|

Notes :- add known Design issues and general notes for the current revision

- do not delete known issue, add fixed version time stamp if issue fixed

|

| - bugfix PL Design (all MGT buffer enabled)

| | 2020-02-13 | 2019.2 | TEB0911-test_board_noprebuilt-vivado_2019.2-build_5_20200213114513.zip

TEB0911-test_board-vivado_2019.2-build_5_20200213112730.zip | John Hartfiel | - 2019.2 update

- new assembly variants

- Vitis support

- FSBL SI programming procedure update

- petalinux device tree and u-boot update

- reduced DDR speed (see Xilinx Datasheet)

| | 2018-11-26 | 2018.2 | TEB0911-test_board_noprebuilt-vivado_2018.2-build_03_20181126132622.zip

TEB0911-test_board-vivado_2018.2-build_03_20181126132607.zip | John Hartfiel | - new assembly variant

- add init.sh

| | 2018-07-20 | 2018.2 | TEB0911-test_board_noprebuilt-vivado_2018.2-build_02_20180719153443.zip

TEB0911-test_board-vivado_2018.2-build_02_20180719153429.zip | John Hartfiel | |

|

Release Notes and Know Issues

| Page properties |

|---|

|

Notes :- add known Design issues and general notes for the current revision

- do not delete known issue, add fixed version time stamp if issue fixed

|

| Scroll Title |

|---|

| anchor | Table_KI |

|---|

| title | Known Issues |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Issues | Description | Workaround | To |

|---|

|

| Scroll Title |

|---|

| anchor | Table_KI |

|---|

| title | Known Issues |

|---|

|

| Scroll Table Layout |

|---|

|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

style | widths | | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

| Issues | Description | Workaround | To be fixed version |

|---|

| No known issues | --- | --- | --- |

...

For general structure and of the reference design, see Project Delivery - Xilinx AMD devices

Design Sources

| Scroll Title |

|---|

| anchor | Table_DS |

|---|

| title | Design sources |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Type | Location | Notes |

|---|

| Vivado | <design name>/block_design

<design name>/constraints

<design name>/ip_lib | Vivado Project will be generated by TE Scripts | | Vitis | <design name>/sw_lib | Additional Software Template for Vitis and apps_list.csv with settings automatically for Vitis app generation | | PetaLinux | <design name>/os/petalinux | PetaLinux template with current configuration |

|

...

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

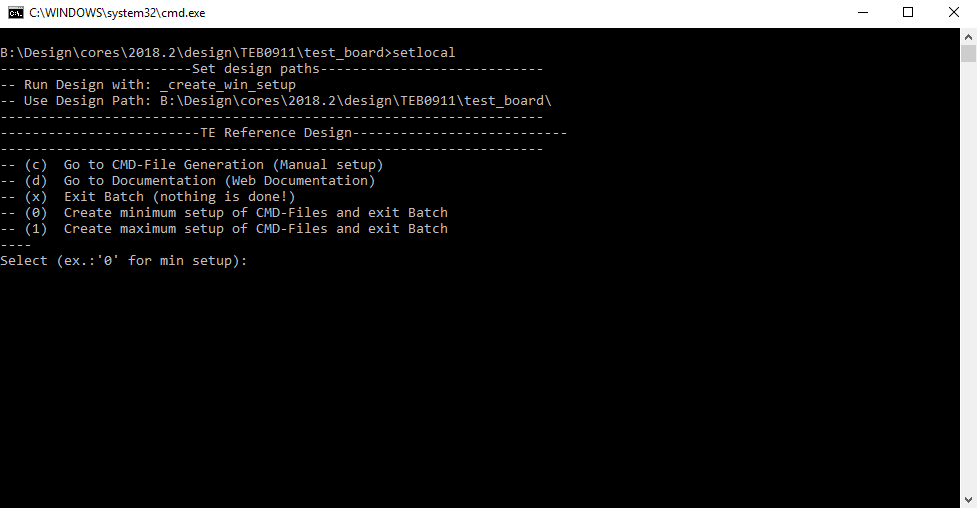

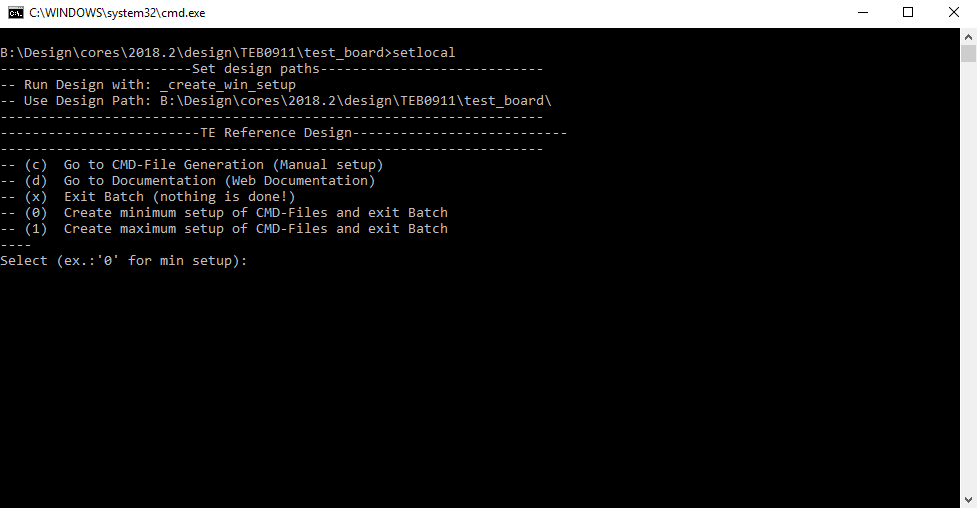

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see alsoTE Board Part Files

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Create Linux (uboot.elf and image.ub) with exported XSA

- XSAis exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\<ddr size>" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with Vitis

- Run on Vivado TCL: TE::sw_run_vitis -all

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_vitis

Note: TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

Launch

| Page properties |

|---|

|

Note: - Programming and Startup procedure

|

...

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

Get prebuilt boot binaries

...

| Scroll Title |

|---|

| anchor | Table_PSI |

|---|

| title | PS Interfaces |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Type | Note |

|---|

| DDR | SODIMM, setting depends on used memory | | QSPI | MIO | | SD0 | MIO | | SD1 | MIO | | I2C0 | MIO | | PJTAG0 | MIO | | UART0 | MIO | | GPIO0 | MIO | | SWDT0..1 |

| | TTC0..3 |

| | GEM3 | MIO | | USB0 | MIO/GTP | | PCIe | MIO/GTP | | DisplayPort | EMIO/GTP |

|

...

Constrains

...

Basic module constrains

Constrains

Basic module constrains

| Code Block |

|---|

| language | ruby |

|---|

| title | _i_bitgen_common.xdc |

|---|

|

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLNONE [current_design] |

...

| Code Block |

|---|

|

/include/ "system-conf.dtsi"

/ {

chosen {

xlnx,eeprom = &eeprom;

};

};

/* USB */

&dwc3_0 {

status = "okay";

dr_mode = "host";

snps,usb3_lpm_capable;

snps,dis_u3_susphy_quirk;

snps,dis_u2_susphy_quirk;

phy-names = "usb2-phy","usb3-phy";

phys = <&lane1 4 0 21 100000000>;

maximum-speed = "super-speed";

};

/* QSPI */

&qspi {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

flash0: flash@0 {

compatible = "jedec,spi-nor";

reg = <0x0>;

#address-cells = <1>;

#size-cells = <1>;

};

};

/* ETH */

&gem3 {

phy-handle = <&phy0>;

phy0: phy0@1 {

device_type = "ethernet-phy";

reg = <1>;

};

};

/* SD1 */

&sdhci1 {

// disable-wp;

no-1-8-v;

};

&i2c0 {

i2cswitch@76 { // I2C Switch U13

compatible = "nxp,pca9548";

#address-cells = <1>;

#size-cells = <0>;

reg = <0x76>;

i2c-mux-idle-disconnect;

i2c@2 { // FMCD (/dev/i2c-3)

#address-cells = <1>;

#size-cells = <0>;

reg = <2>;

};

i2c@3 { // FMCE (/dev/i2c-4)

#address-cells = <1>;

#size-cells = <0>;

reg = <3>;

};

i2c@4 { // FMCB (/dev/i2c-5)

#address-cells = <1>;

#size-cells = <0>;

reg = <4>;

};

i2c@5 { // FMCC (/dev/i2c-6)

#address-cells = <1>;

#size-cells = <0>;

reg = <5>;

};

i2c@6 { // PLL (/dev/i2c-7)

#address-cells = <1>;

#size-cells = <0>;

reg = <6>;

si570_2: clock-generator3@5d {

#clock-cells = <0>;

compatible = "silabs,si570";

reg = <0x5d>;

temperature-stability = <50>;

factory-fout = <156250000>;

clock-frequency = <78800000>;

};

};

};

i2cswitch@77 { // I2C Switch U37

compatible = "nxp,pca9548";

#address-cells = <1>;

#size-cells = <0>;

reg = <0x77>;

i2c-mux-idle-disconnect;

i2c@0 { // SFP2 (/dev/i2c-9)

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

};

i2c@1 { // FMCA (/dev/i2c-10)

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

};

i2c@2 { // FMCF (/dev/i2c-11)

#address-cells = <1>;

#size-cells = <0>;

reg = <2>;

};

i2c@3 { // SFP0 (/dev/i2c-12)

#address-cells = <1>;

#size-cells = <0>;

reg = <3>;

};

i2c@4 { // SFP1 (/dev/i2c-13)

#address-cells = <1>;

#size-cells = <0>;

reg = <4>;

};

i2c@5 { // MEM (/dev/i2c-14)

// Low frequency to work with CPLD

clock-frequency = <100000>;

#address-cells = <1>;

#size-cells = <0>;

reg = <5>;

eeprom: eeprom@54 {

compatible = "atmel,24c08";

reg = <0x54>;

};

};

i2c@6 { // DDR4 (/dev/i2c-15)

#address-cells = <1>;

#size-cells = <0>;

reg = <6>;

};

i2c@7 { // USBH (/dev/i2c-16)

#address-cells = <1>;

#size-cells = <0>;

reg = <7>;

};

};

};

|

...

Kernel

Start with petalinux-config -c kernel

Changes:

- # CONFIG_CPU_IDLE is not set (only needed to fix JTAG Debug issue)

- # CONFIG_CPU_FREQ is not set (only needed to fix JTAG Debug issue)

- CONFIG_EDAC_CORTEX_ARM64=y (only needed to fix JTAG Debug issue)

- CONFIG_NVME_CORE=y

- CONFIG_BLK_DEV_NVME=y

- # CONFIG_NVME_MULTIPATH is not set

- CONFIG_NVME_TARGET=y

- # CONFIG_NVME_TARGET_LOOP is not set

- # CONFIG_NVME_TARGET_FC is not set

- CONFIG_NVM=y

- CONFIG_NVM_PBLK=y

- CONFIG_NVM_PBLK_DEBUG=y

Rootfs

Start with petalinux-config -c kernelrootfs

Changes:

- # CONFIG_CPU_IDLE is not set (only needed to fix JTAG Debug issue)

- # CONFIG_CPU_FREQ is not set (only needed to fix JTAG Debug issue)

- CONFIG_EDAC_CORTEX_ARM64=y (only needed to fix JTAG Debug issue)

Rootfs

Start with petalinux-config -c rootfs

Changes:

- CONFIG_i2c-tools=y

- CONFIG_busybox-httpd=y (for web server app)

- CONFIG_packagegroup-petalinux-utils(util-linux,cpufrequtils,bridge-utils,mtd-utils,usbutils,pciutils,canutils,i2c-tools,smartmontools,e2fsprogs)i2c-tools

Applications

See: \os\petalinux\project-spec\meta-user\recipes-apps\

...

| Scroll Title |

|---|

| anchor | Table_dch |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | 2*,*,3*,4* |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Document Revision | Authors | Description |

|---|

| Page info |

|---|

| modified-date |

|---|

| modified-date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | | 2020-06-03 | v.10 | John Hartfiel | | | 2020-03-25 | v.9 | John Hartfiel | | | 2020-02-24 | v.8 | John Hartfiel | | | 2020-02-13 | v7 | John Hartfiel | - new assembly variants

- Release 2019.2

| | 2019-02-07 | v.6 | John Hartfiel | | | v.5 | John Hartfiel | - new assembly variant

- documentation style update

| | v.4 | John Hartfiel | | | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| -- |

|

...