Page History

...

| Scroll pdf title | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| |||||||||

|

Signal FX2_PS_EN

To command signal FX2_PS_EN, read the reference firmware code.

IOD = 0x03; // Enable PS_EN and disable PROG_B

OED = 0x03; // Configure PS_EN and PROG as outputs

...

| Scroll pdf title | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

|

Signal PS_EN

Signal PS_EN enables (1) or disables (0) power rails 1.2 V, 1.5 V and 2.5 V.

Scroll pdf title title Power rails 1.2 V, 1.5 V and 2.5 V could be enabled/disabled by signal PS_EN. Power-rail 3.3V is not controlled by signal PS_EN and is unconditionally enabled.

Scroll pdf title title Power rails 3.3V could not be enabled/disabled by signal PS_EN.

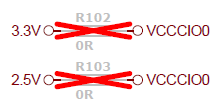

VCCIO assembly options

According to the corresponding assembly option, power rail VCCCIO0 can depend or not on the power rail 2.5V.

VCCIO0 voltage can be configured in 3 ways:

- 2.5V - When resistor R103 is populated and resistor R102 is not populated.

- 3.3V - When R103 is not populated and resistor R102 is populated.

- 1.2 V ÷ 3.3 V (External supply) - When R103 is not populated and R102 is not populated. In this case external supply source have to be connected to pins 1, 2, 3, 4 of J4 B2B connector(1).

(1) See Spartan-6 documentation fo VCCIO power range.

| Scroll pdf title | ||

|---|---|---|

| ||

| Others options of VCCIO0 power supply are not supported and can damage the FPGA! |

|---|

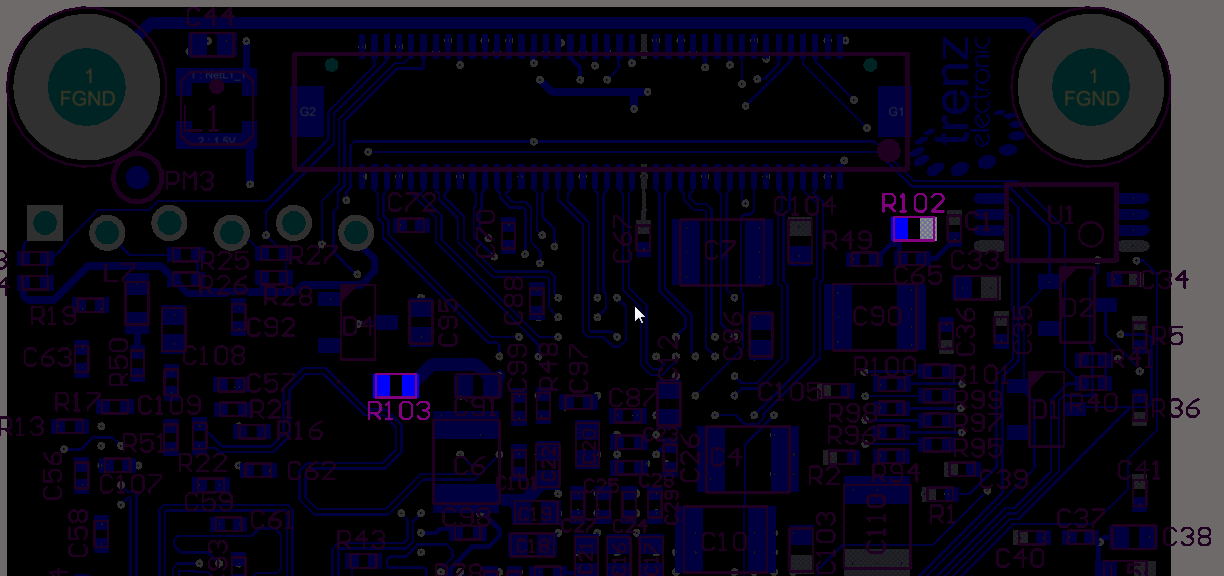

See the figure below to locate R102 and R103 on PCB.

| Scroll pdf title | ||

|---|---|---|

| ||

Dip Switch S1B = FX2 PON

When Dip switch S1B is in the left position ( = FX2 PON : power rails conditionally on depending on signal FX2_PS_EN), signal PS_EN is set to signal FX2_PS_EN (PS_EN = FX2_PS_EN) driven by the EZ-USB FX2LP USB FX2 microcontroller under user control (IOD and OED of fw.c).

...

- FPGA core logic (1.2 V)

- DDR SDRAM (2.5 V)

- FPGA bank 1 (1.5 V)

- VREF1 (0.75 V)

- VCCCIO0 (2.5 V) FPGA bank 0 (if R102+R103- assembly)

Dip Switch S1B = PON

Full power operation (PS_EN = 1): when Dip switch S1B is in the right position (PON = power rails unconditionally on), signal PS_EN is set to power rail 3.3V. Thus power rails 1.2 V, 1.5 V and 2.5 V are unconditionally enabled.

| Scroll pdf title | ||

|---|---|---|

| ||

|

Summary table

The table below summarizes all switching options implied by Dip switch S1B and firmware signal FX2_PS_EN (under the standard assembly option).

...