Page History

...

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

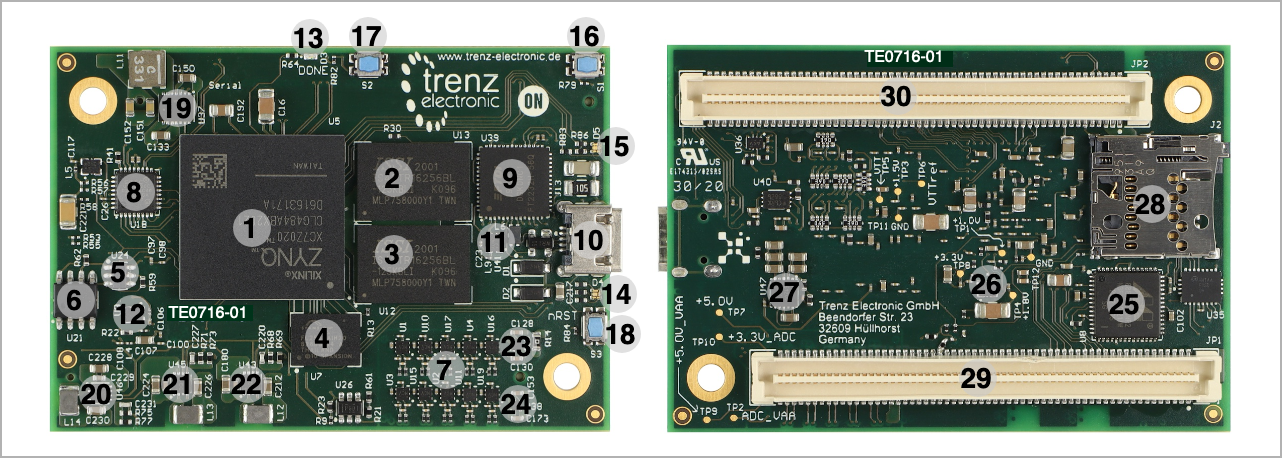

- Xilinx Zynq XC7Z SoC, U5 (Top)

- 4Gbit DDR3/L SDRAM, U13 (Top)

- 4Gbit DDR3/L SDRAM, U12 (Top)

- 32MByte Quad SPI Flash memory, U7 (Top)

- 2Kbit MAC address serial EEPROM with EUI-48TM node identity, U24 (Top)

- 512Kb Serial EEPROM memory, U21 (Top)

- 10x 12-Bit Low Power SAR ADCs, U1..U4, U10, U11, U15..U17, U19 (Top)

- High-speed USB 2.0 ULPI transceiver, U18 (Top)

- Single chip USB Interface 2.0 to UART / JTAG, U39 (Top)

- MicroUSB-B connector, J13 (Top)

- Low-power oscillator @ 12.000000MHz (OSCI-FTDI), U41 (Top)

- Low-power oscillator @ 25.000000MHz (ETH-CLK), U9 (Top)

- LED FPGA DONE (Green) 13 d3 (Top)

- User RGB LED 1 D4 (Top)

- User RGB LED 2 D5 (Top)

- Tactile Switch (User), S1 (Top)

- Tactile Switch (User), S2 (Top)

- Tactile Switch (Reset), S3 (Top)

- 5A Synchronous Buck DC-DC Converter (1V), U37 (Top)

- 2A Synchronous Buck DC-DC Converter (3.3V), U46 (Top)

- 2A Synchronous Buck DC-DC Converter (1.8V), U45 (Top)

- 2A Synchronous Buck DC-DC Converter (1.5V), U43 (Top)

- 250mA Ultra-Low Noise LDO Regulator (3.3V_ADC Digital I/O supply), U23 (Top)

- 250mA Ultra-Low Noise LDO Regulator (ADC_VAA Analog supply/reference, 3.3V), U38 (Top)

- Gigabit Ethernet PHY transceiver, U8 (Bottom)

- Low-power oscillator @ 33.333333MHz (PS-CLK), U6 (Bottom)

- 3A Sink/Source DDR Termination Regulator (VTT/VTTREF, 0.75V), U47 (Bottom)

- Card Connector microSD™, J2 (Bottom)

- 2x60 positions high speed/density plug connector, JP1 (Bottom)

- 2x60 positions high speed/density plug connector, JP2 (Bottom)

...

Overview

Content Tools