Page History

...

| Scroll pdf ignore | |

|---|---|

Table of contents

|

...

|

...

Create SDK Project from Vivado

...

- Requirements (for HDF-Export with Bitfile):

- "Generate Bitstream" must be finished.

- For HDF export click: File→Export→Export Hardware (Select "Include bitstream" and your preferred folder)

- To Launch SDK click: File→Launch SDK (Select your HDF location and preferred SDK workspace)

- SDK Project will be generated and opened (default location /vivado/<project name>.sdk).

- (optionoptional) Include local library folder in SDK, click: Xilinx Tool→Repositories→New Local Repositories

- for TE-SW-templates use the path: <reference design>/sw_lib

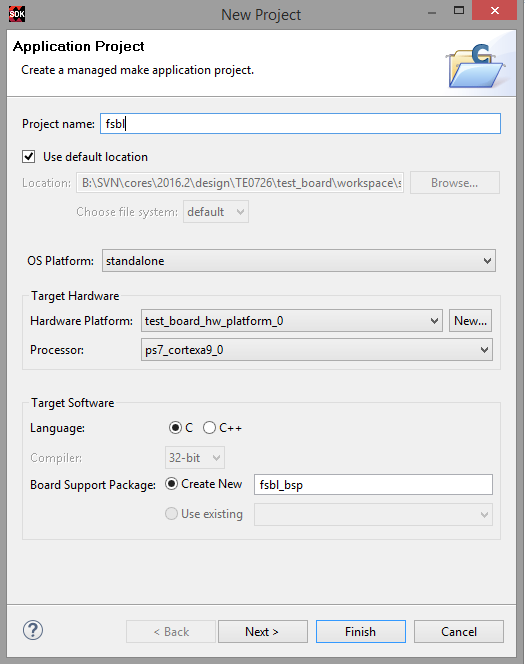

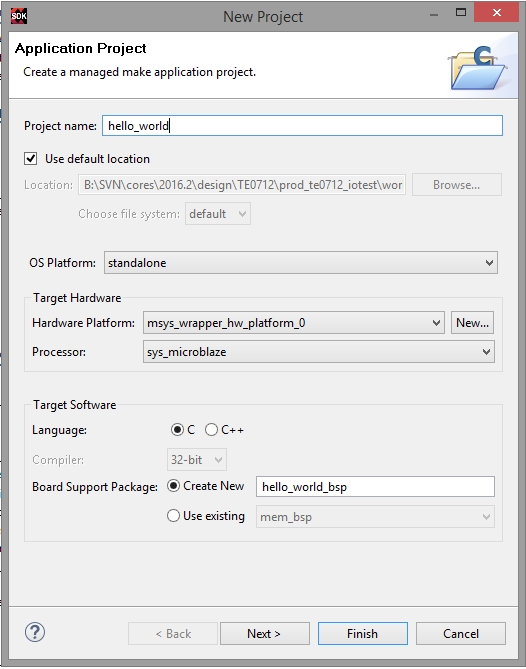

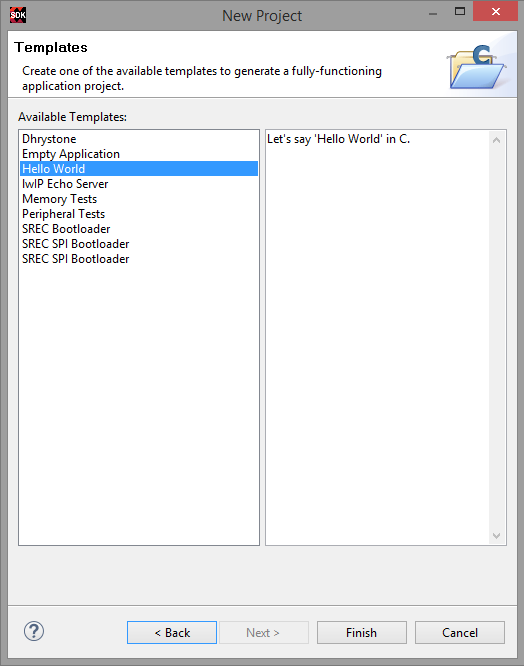

Create Software Application with SDK Template

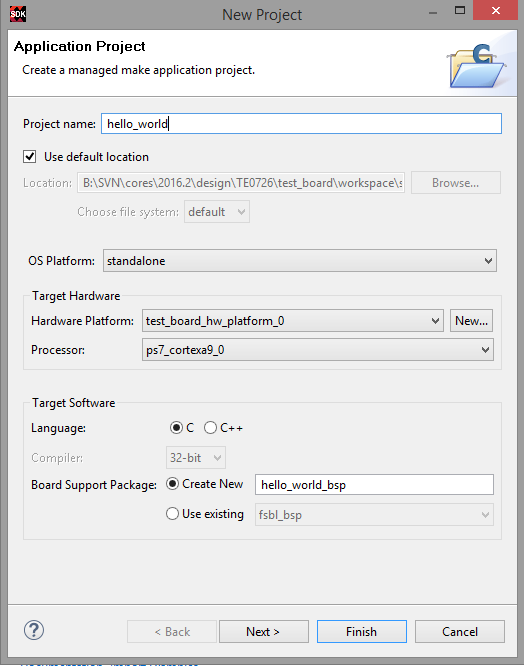

- Click:File→Application File→New → Application Project

- Select Name and OS (Example Name:Hello World, OS:standalone)

- Click: Next

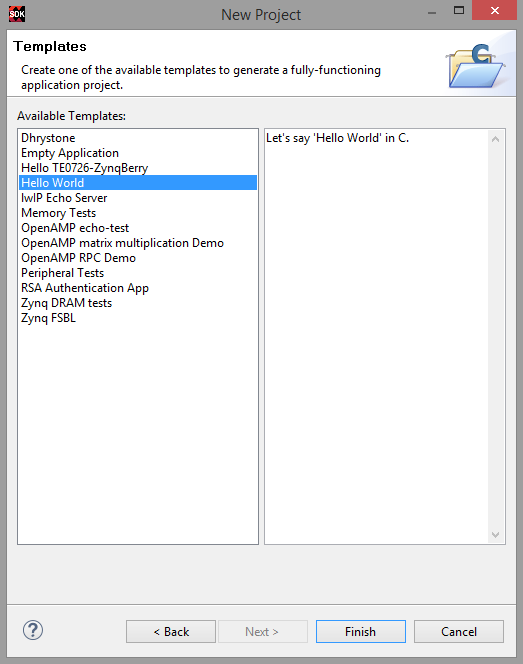

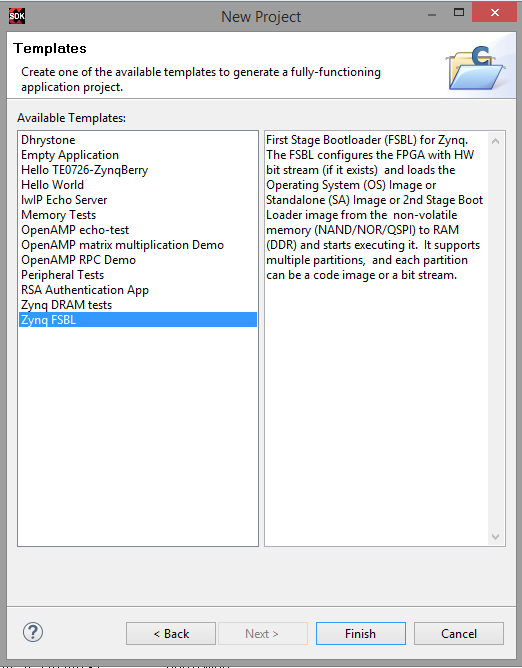

- Select Application (Example Hello World)

- Click Finished

- Project with Xilinx Hello Word will be generated automatically

...

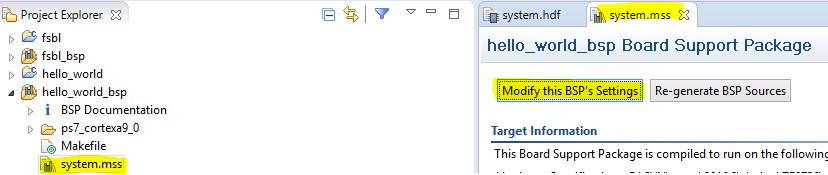

- Double Click on the system.mss of your Application Project BSP folder in the Project Explorer.

- Click Modify this BSP's Settings.

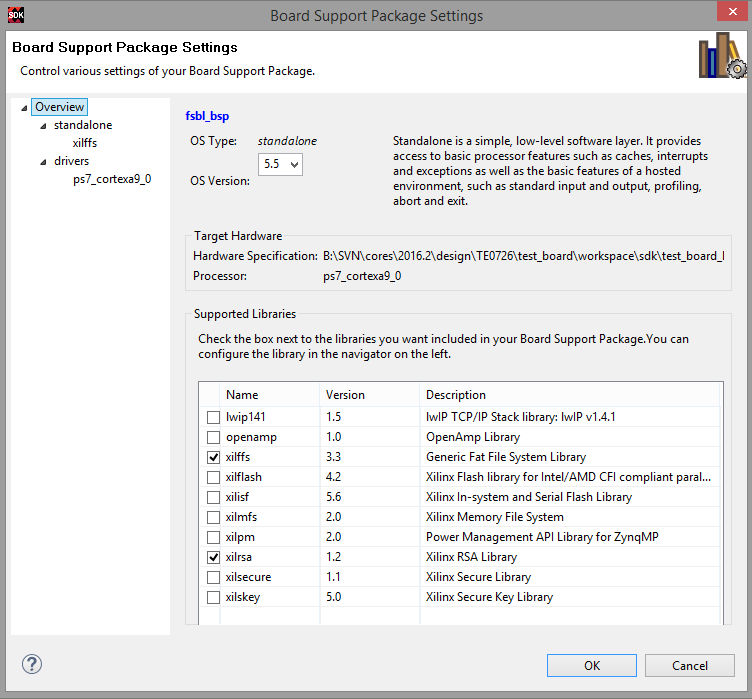

- Modify BSP stdin/sdtout peripheral, drivers or libraries settings

...

Debug Software Application

...

| Info |

|---|

This examples shows only the basic steps without TE-Module specific settings |

Xilinx "Hello World" on ZynqMP

Same procedure as on Zynq device.

Xilinx "Hello World" on Zynq

| Info |

|---|

This Hello World example is not usable for TE0722 without DDR |

- Create SDK Project:

- Create FSBL:

- See Create Software Application with SDK Template

- (optional) If necessary, modify FSBL-BSP stdin/sdtout peripheral, drivers or libraries settings for the FSBL Application

- Create Hello_World:

- See Create Software Application with SDK Template

- (optional) If necessary, modify FSBL-BSP stdin/sdtout peripheral, drivers or libraries settings for the Hello World Application

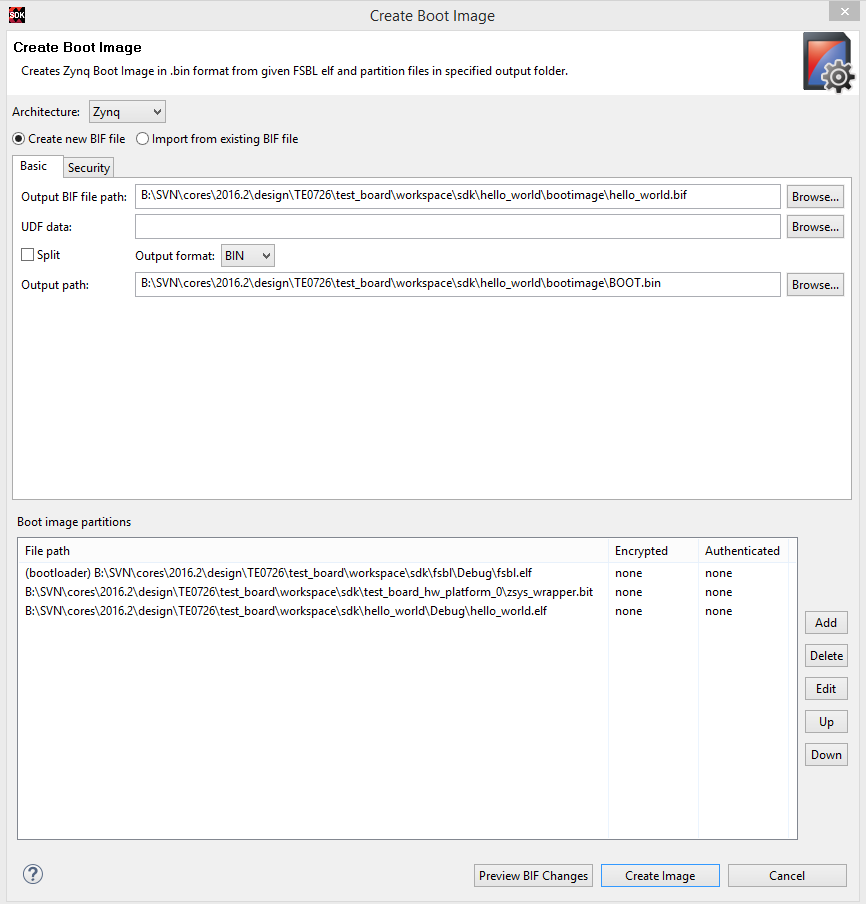

- Create Boot.bin

- Right Click on the hello_world Project in the Project Explorer.

- Click:Create Boot Image

All partition settings will be set automatically,if Build Process of FSBL and Hello World was successful. - Create Image

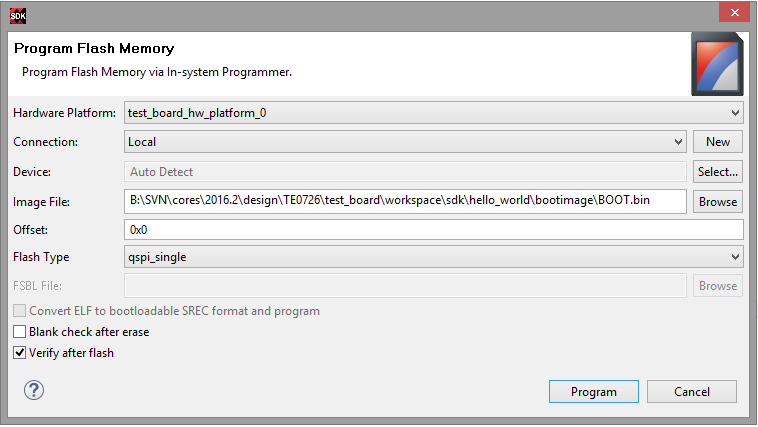

- Program Flash

- Click:Xilinx Tools→Program Flash

- Important since Vivado 2017.4: FSBL is needed on setup for QSPI programming. Reference Designs include special FSBL to program QSPI Flash without changing boot mode to JTAG

- Select generated Boot.bin (optional select "Verify after flash")

Note: Flash Type depends on HW: Select "qspi_single" or "qspi_dual_parallel", see <Reference Design>/board_files/*_board_files.csv - Program Flash

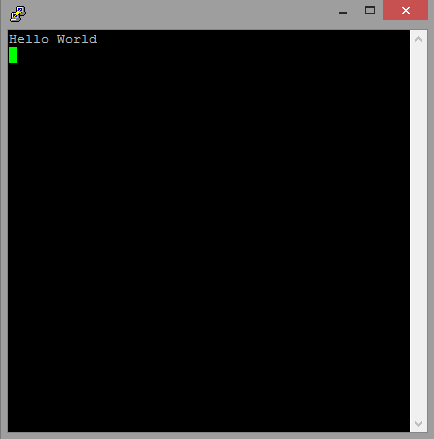

- Connect Serial Console

- COM Port: See OS Device Manager

- Speed: depends on your Vivado Project. On Zynq Devices Default 115200

Reboot Zynq

Note Xilinx Hello World appears only one time on startup, so use HW-Reset Button on Module or Vivado Hardware Manager "Boot from Configuration Memory Device" Command to reboot PS

...

. Alternatively modify helloworld.c to run print "Hello World" in endless loop.

Xilinx "Hello World" on MicroBlaze

- Create SDK Project:

- Create Hello_World:

- See Create Software Application with SDK Template

- (optional) If necessary, modify "Hello World"-BSP stdin/sdtout peripheral, drivers or libraries settings for the Hello World Application

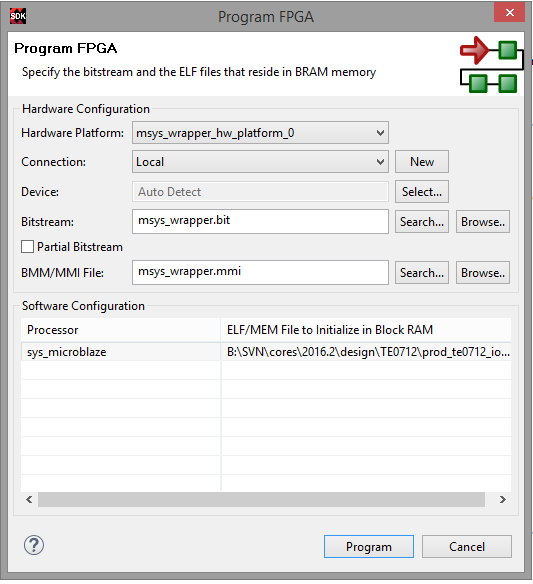

- Program FPGA:

- Click:Xilinx Tools→Program FPGA

Select "hello_world.elf" as ELF File for Processor Block RAM

Click: Program

Note This step configure the Bitfile with the specified ELF-files and program the FPGA

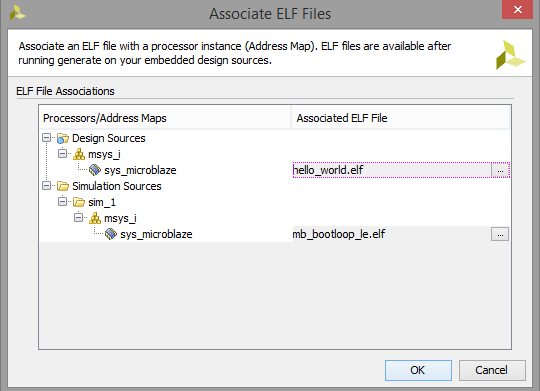

- (Optional) include ELF-file in Vivado Project:

- Right Click on the Block Diagram on Vivado Project Manager source window

- Select "Associated ELF-File"

- Generate Bitfile

- Program FPGA with Vivado HW-Manager

| Note |

|---|

Xilinx Hello World appears only one time on startup, so use HW-Reset Button on Module or Vivado Hardware Manager "Boot from Configuration Memory Device" Command to reboot PS. Alternatively modify helloworld.c to run print "Hello World" in endless loop. |

Convert Application ELF to SREC

- Create Application (for example Hello World)

- Open "Application" properties → C/C++ Build → Settings and go into Build Steps Tap.

- Add to Post-build steps: mb-objcopy -O srec <applicationname>.elf <applicationname>.srec

- Press Apply or regenerate project

References

- UltraFast Design Methodology Guide for the Vivado Design Suite (UG949)

- UltraFast Embedded Design Methodology Guide (UG1046)

- Zynq UltraScale+MPSoC Software Developer Guide (UG1137)

- Zynq-7000 All Programmable SoC Software Developers Guide (UG821)

- Vivado Design Suite User Guide - Embedded Processor Hardware Design (UG898)

- Generating Basic Software Platforms - Reference Guide (UG113)

- PetaLinux KICKStart

...