Page History

| Scroll Ignore |

|---|

Download PDF Version of this Document. |

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of Contents

|

Overview

| Scroll Only (inline) |

|---|

On https://wiki.trenz-electronic.de/display/PD/TE0710 the online Online version of this manual and other related documents can be found. |

...

at https://shop.trenz-electronic.de/de/Download/?path=Trenz_Electronic/TE0710

|

...

Xilinx Artix-7

...

FPGA,

...

Dual 10/100 MBit Ethernet

...

PHYs, 512 MByte DDR3 SDRAM with 8-bit data-width, 32

...

MByte Quad SPI Flash memory for configuration and operation and powerful switch-mode power supplies for all on-board voltages. A large number of configurable I/

...

O's is provided via rugged high-speed stacking strips. All modules in 4 x 5 cm form factor are mechanically compatible.

All this on a tiny footprint, smaller than a credit card, at the most competitive price.

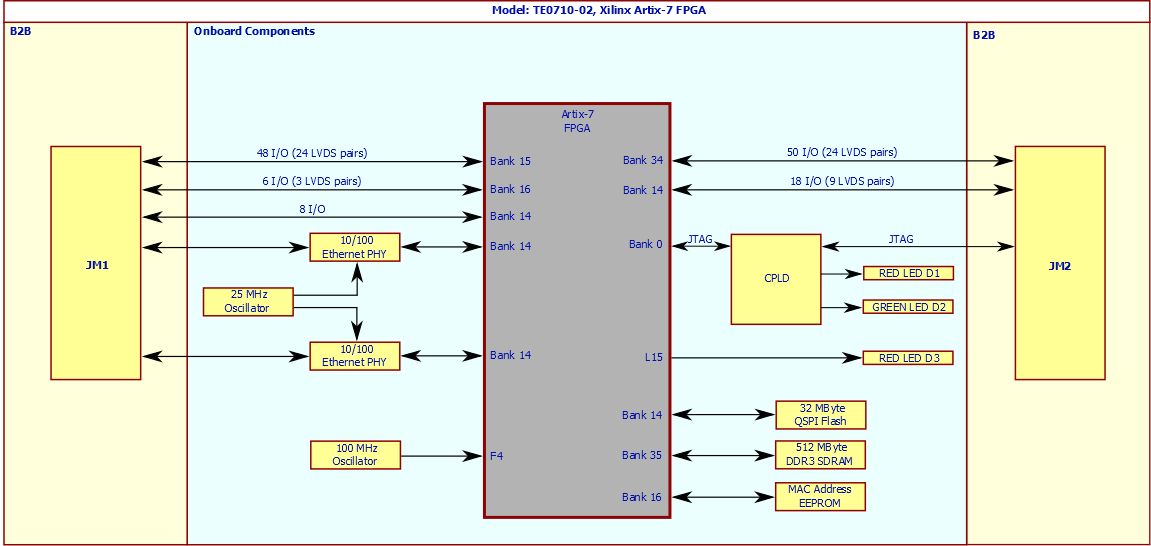

Block Diagram

Key Features

...

Figure 1: TE0710-02 Block Diagram

Main Components

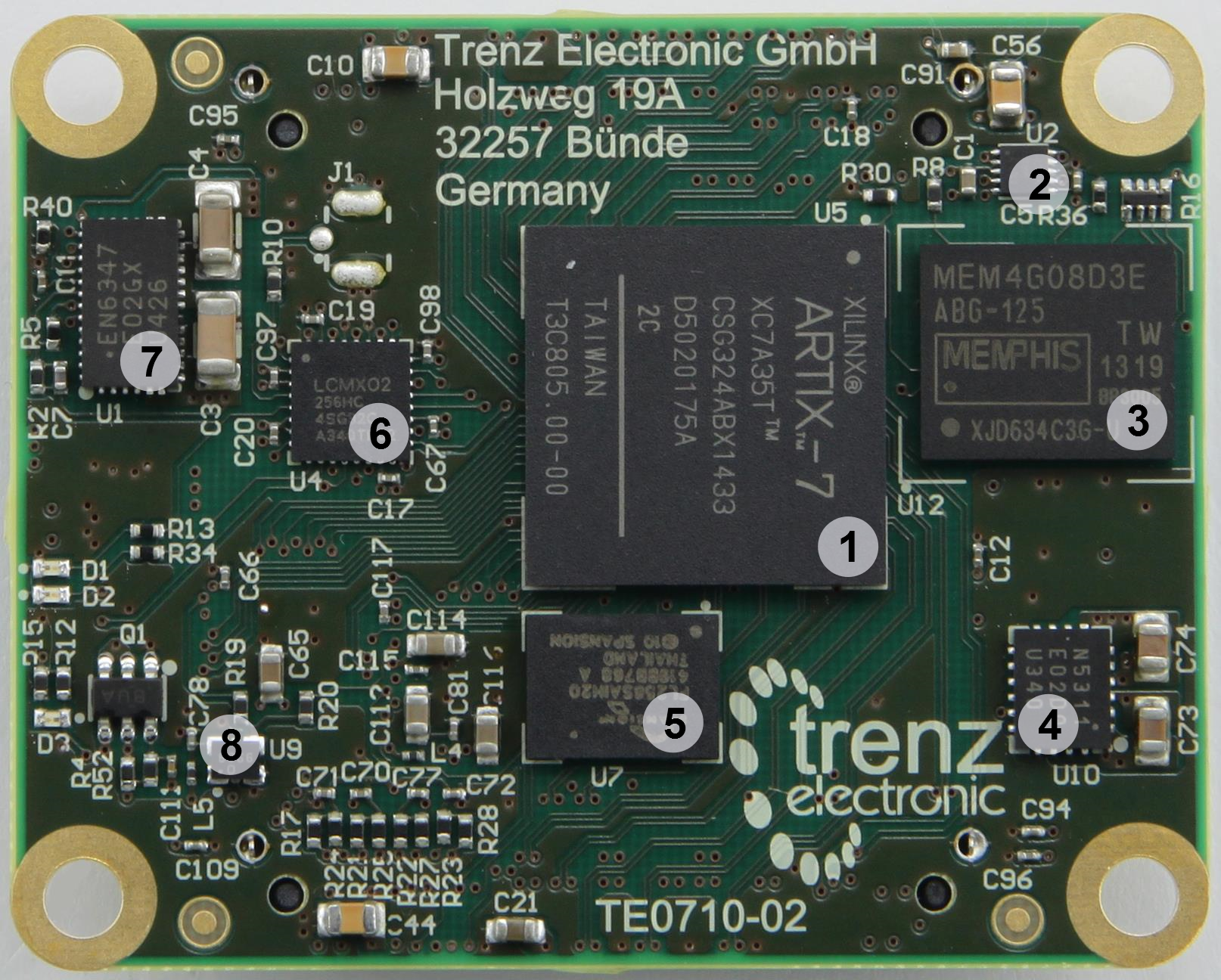

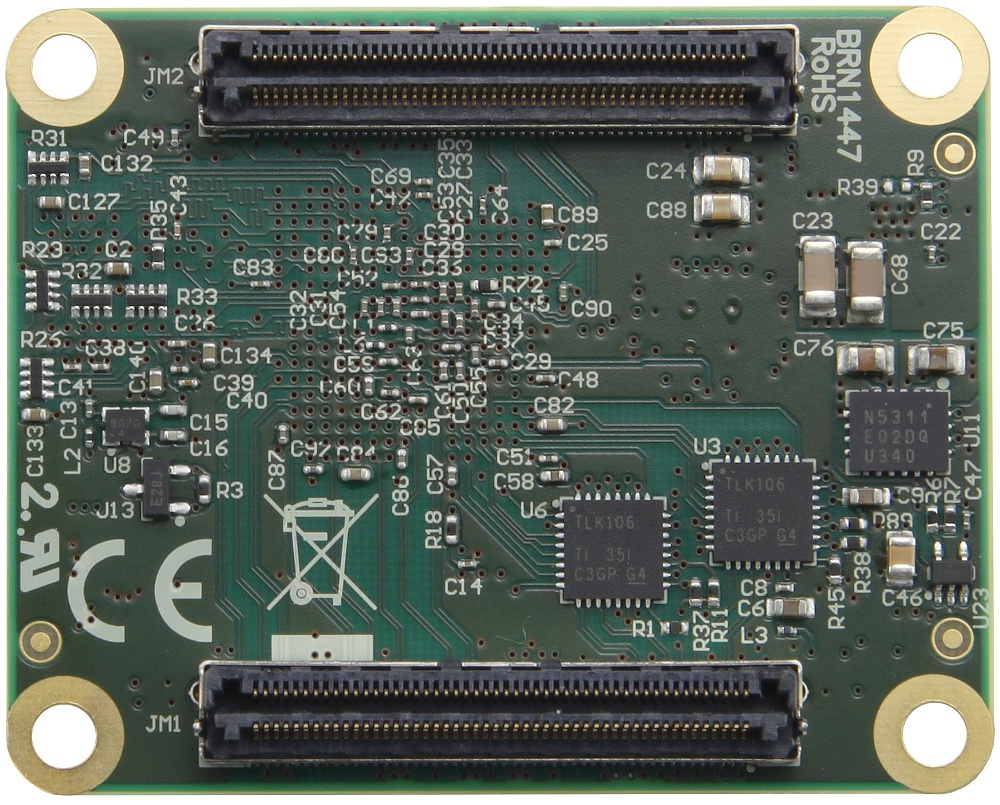

Figure 2: TE0710 (REV 02).

- Artix-7 (15T to 100T)

...

Rugged for shock and high vibration

- FPGA

- TPS51206 DDR3-SDRAM voltage supply

- MEM4G08D3EABG 512 MByte DDR3 SDRAM

...

Dual 100 MBit Ethernet PHY

MAC Address EEPROM

...

32 MByte QSPI Flash memory (with XiP support)

...

100 MHz programmable MEMS oscillator

...

Plug-on module with 2 × 100-pin high-speed hermaphroditic strips

...

112 FPGA I/Os (51 differential pairs) and available on board-to-board connectors

...

On-board high-efficiency DC-DC converters

4.0 A x 1.0 V power rail

1.0 A x 1.8 V power rail

1.0 A x 1.5 V power rail

...

System management and power sequencing

...

eFUSE bit-stream encryption

...

AES bit-stream encryption

...

User LED

...

Evenly-spread supply pins for good signal integrity

- EN5311QI Voltage Regulator 1.5V

- S25FL256S 32 Mbyte Quad SPI Flash memory

- System Controller CPLD (Lattice LCMXO2-256HC): 256 Macrocell CPLD

- EN6347QI voltage Regulator 1.0V

- SiT8008AI 25 MHz Ethernet reference clock

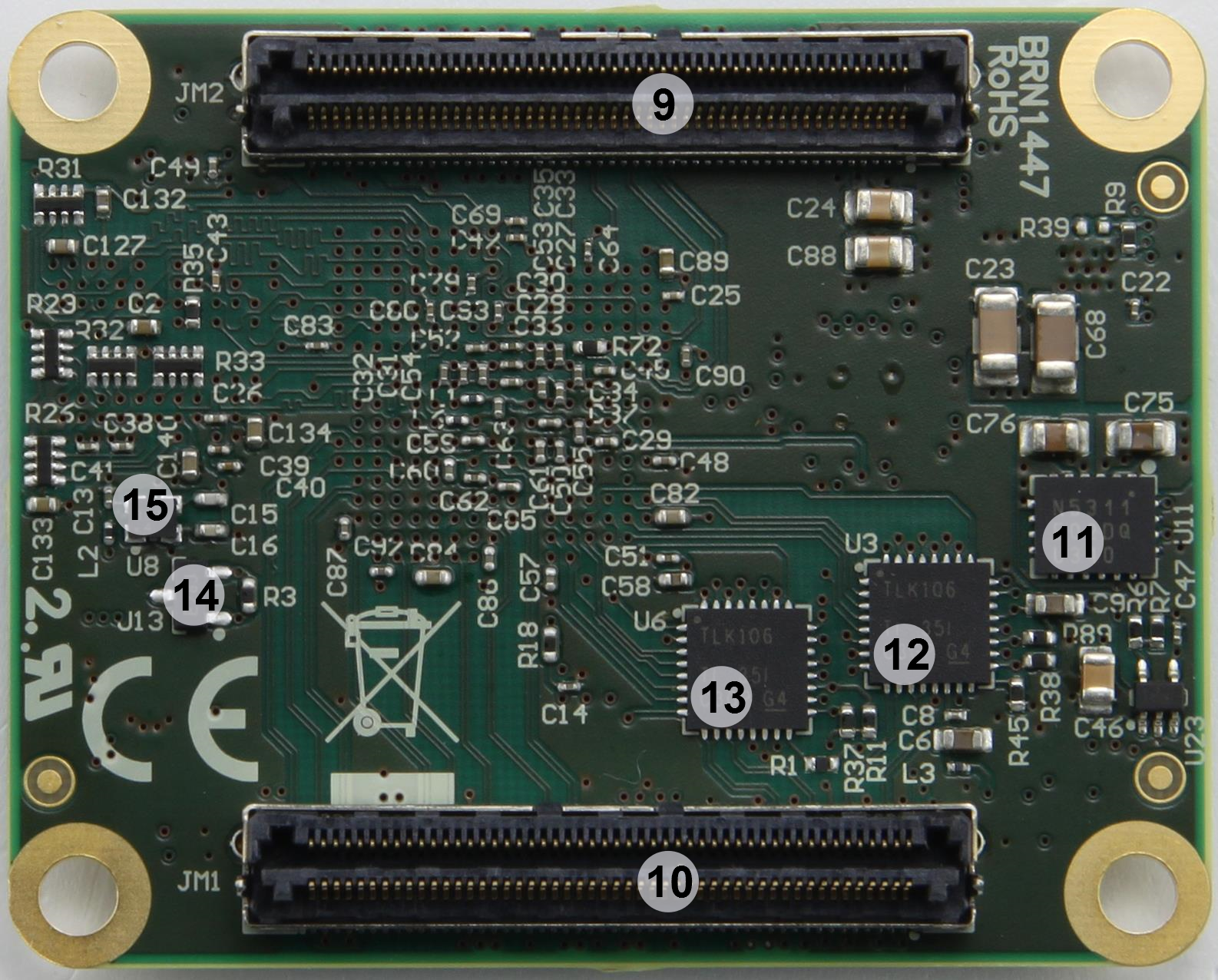

- B2B connector JM2 (0,40 mm Razor Beam™ High Speed Hermaphroditic Terminal/Socket Strip (LSHM-150))

- B2B connector JM1 (0,40 mm Razor Beam™ High Speed Hermaphroditic Terminal/Socket Strip (LSHM-150))

- EN5311QI voltage Regulator 1.8V

- TLK106 10/100 Mbps Ethernet PHY

- TLK106 10/100 Mbps Ethernet PHY

- 11AA02E48T-I/TT 2 Kbit EEPROM with UNI/O serial interface

- SiT8008AI 100 MHz reference clock (connected to FPGA bank 35)

Key Features

Industrial-grade Xilinx Artix-7 (15T to 100T) SoM (System on Module), supported by the free Xilinx Vivado WebPACK tool

Rugged for shock and high vibration

512 MByte DDR3 SDRAM

Dual 10/100 MBit Ethernet PHY

MAC Address EEPROM

32 MByte QSPI Flash memory (with XiP support)

100 MHz MEMS oscillator

Plug-on module with 2 × 100-pin high-speed hermaphroditic strips

112 FPGA I/Os (51 differential pairs) are available on board-to-board connectors

On-board high-efficiency DC-DC converters

4.0 A x 1.0 V power rail

1.0 A x 1.8 V power rail

1.0 A x 1.5 V power rail

System management and power sequencing

eFUSE bit-stream encryption

AES bit-stream encryption

User LED

Evenly-spread supply pins for good signal integrity

Assembly options for cost or performance optimization available upon request.

Initial Delivery State

| Storage device name | Content | Notes |

|---|---|---|

SPI Flash OTP Area | Empty, not programmed | Except serial number programmed by flash vendor. |

SPI Flash Quad Enable bit | Programmed | - |

SPI Flash main array | Demo design | - |

EFUSE USER | Not programmed | - |

EFUSE Security | Not programmed | - |

Table 1: Initial delivery state

Signals, Interfaces and Pins

Board to Board (B2B) I/Os

I/O signals connected to the FPGA's I/O banks and B2B connector:

| Bank | Type | B2B Connector | I/O Signal Count | Voltage | Notes |

|---|---|---|---|---|---|

0 | HR | - | - | 3.3V | Configuration bank |

14 | HR | JM1 | 8 I/O-pins | 3.3V | HR-Banks support voltages from 1.2V to 3.3V standards. See the Artix-7 datasheet (DS181) for the allowable voltage range. |

15 | HR | JM1 | 48 I/O-pins 24 LVDS-pairs possible | user | as above |

16 | HR | JM1 | 6 I/O-pins 3 LVDS-pairs possible | 3.3V | as above |

| 34 | HR | JM2 | 50 I/O-pins 24 LVDS-pairs possible | user | as above |

| 35 | HR | - | - | 1.5V | connected to 512 MByte DDR3 SDRAM |

Table 2: Voltage ranges and pin-outs of available logic banks of the FPGA

Please use Master Pinout Table table as primary reference for the pin mapping information.

JTAG Interface

JTAG access to the Xilinx Artix-7 and to the System Controller CPLD is provided through B2B connector JM2.

| JTAG Signal | B2B Connector |

|---|---|

| TCK | JM2-99 |

| TDI | JM2-95 |

| TDO | JM2-97 |

| TMS | JM2-93 |

| JTAGEN | JM1-89 |

Table 3: Pin-mapping of JTAG Interface on B2B connector

| Note |

|---|

Select by JTAGEN pin on B2B connector JM1-89 either to access FPGA Artix-7 (JTAGEN pin driven low or open) or System Controller via JTAG (JTAGEN pin driven high). The use of Xilinx legacy development tools (ISE, Impact) is not recommended. Impact recognizes only A100T, any smaller Artix-7 FPGA is not recognized as Xilinx FPGA by Impact. |

System Controller I/O Pins

Special purpose pins are connected to smaller System Controller CPLD and have following default configuration:

| Pin Name | Mode | Function | Default Configuration | B2B Connector |

|---|---|---|---|---|

| PGOOD | Output | Power Good | Active high when all on-module power supplies are working properly. | JM1-30 |

| RESIN | Input | Reset | Active low reset signal, drive low to keep the system in reset (FPGA pin PROG_B will be driven by CPLD) | JM2-18 |

| JTAGEN | Input | JTAG Select | Low for normal operation, high (3.3V) to programm the System Controller CPLD | JM1-89 |

Table 4: Pin-description of System Controller CPLD

LEDs

On the SoM TE0710 there is a total of 3 LEDS available. Two LEDs are status LEDs, one can freely used in costumer designs. The user LED is routed to the FPGA by the net with the schematic-name 'USERLED'.

When the FPGA is not configured the status LEDs will flash continuously. Finally once FPGA configuration has completed the status LEDs can be used in the user's FPGA design.

| LED | Color | Connected to pin | Description and Notes |

|---|---|---|---|

| D1 | red | SYSLED2 | System Controller status LED, connected to CPLD |

| D2 | green | SYSLED1 | System Controller status LED, connected to CPLD |

| D3 | red | USERLED | User LED, active LOW, connected to FPGA Pin L15 |

Table 5: Description of the on board LEDs

Clocking

The TE0710 is equipped with two Sitara reference clocks to provide clock signals to the Ethernet PHYs and for the on board 512 MByte DDR3 SRRAM.

| Clock | Frequency | IC | Connected to | Notes |

|---|---|---|---|---|

Ethernet reference | 25 MHz | U9 SiT8008AI-73-XXS-25.000000E | ICs U3, U6 TLK106RHB | clock signal shared by both Ethernet PHYs |

| DDR3 SDRAM reference | 100 MHz | U8 SiT8008AI-73-XXS-100.000000E | FPGA bank 35, pin F4 | forwarded as differential clock signal to DDR3 SDRAM IC U12 MEM4G08D3EABG-125 |

Table 6: Clocks overview

Onboard Peripherals

32 Mbyte Quad SPI Flash Memory

An SPI flash memory S25FL256S (U7) is provided for FPGA configuration file storage. After configuration completes the remaining free memory can be used for application data storage. All four SPI data lines are connected to the FPGA allowing x1, x2 or x4 data bus widths to be used. The maximum data rate will be dependent on the bus width and clock frequency.

| Note |

|---|

SPI Flash QE (Quad Enable) bit must be set, or the FPGA would not configure from Flash. This bit is always set at manufacturing. |

System Controller

The system controller is used to coordinate the configuration of the FPGA. The FPGA is held in reset (by driving the PROG_B signal) until the power supplies have sequenced. Low level at RESIN pin also resets the FPGA. This signal can be driven from the user’s PCB via the B2B connector pin JM2-18. Input EN1 is also gated to FPGA Reset, should be open or pulled up for normal operation. EN1 low does not turn off on board DCDC converters.

It is possible for the user to create their own system controller design using the Lattice Diamond software. Once created the design can be programmed into the device using the JTAG pins. The signal JTAGEN should be set to 3.3V to enable programming mode. For normal operation it should be set to 0V.

There are two LEDs that are connected to the system controller. When the FPGA is not configured the LEDs will flash continuously. Finally once FPGA configuration has completed the LEDs can be used in the user's FPGA design.

DDR3 SDRAM

The TE0710-02 board is equipped with one DDR3 SRRAM IC (U12) with a capacity of 512 MByte volatile memory for storing user code and data.

- Part number: MEM4G08D3EABG-125 (Memphis)

- Supply voltage: 1.5V

- Organization: 64M words x 8 bits x 8 banks

- Memory speed limited by Artix speed grade and MIG

Configuration of the DDR3 memory controller in the FPGA should be done using the Xilinx MIG tool in the Vivado IP catalog.

Ethernet

The TE0710-02 is equipped with two TI TLK106 10/100 MBit Ethernet PHYs (U3 and U6). The I/O Voltage is fixed at 3.3V. The reference clock input for both PHYs is supplied from an on board 25MHz oscillator (U9).

Both Ethernet PHYs are connected to FPGA Bank 14 using MII interface.

Note: Pin ETH2_INT (power down or interrupt, default function is power down) is connected to FPGA bank 16 (pin D10).

Power and Power-On Sequence

Power Supply

Power supply with minimum current capability of 2A for system startup is recommended.

| Power Input Pin | Voltage Range | Max Current |

|---|---|---|

| VIN | 3.3V to 5.5V | Typical 200mA, depending on customer design and connections. |

| 3.3VIN | 3.3V | Typical 50mA, depending on customer design and connections. |

Table 7: maximal current of power supplies

| Tip |

|---|

Vin and Vin 3.3V can be connected to the same source (3.3 V). |

Lowest power consumption is achieved when powering the module from single 3.3V supply. When using split 3.3V/5V supplies the power consumption (and heat dissipation) will rise, this is due to the DC/DC converter efficiency (it decreases when VIN/VOUT ratio rises).

Power-On Sequence

For highest efficiency of on board DC/DC regulators, it is recommended to use same 3.3V power source for both VIN and 3.3VIN power rails. Although VIN and 3.3VIN can be powered up in any order, it is recommended to power them up simultaneously.

It is important that all baseboard I/O's are 3-stated at power-on until System Controller sets PGOOD signal high (B2B connector JM1, pin 30), or 3.3V is present on B2B connector JM2 pins 10,12 or 91, meaning that all on-module voltages have become stable and module is properly powered up.

See Xilinx datasheet DS181 (for Artix7) for additional information. User should also check related baseboard documentation when choosing baseboard design for TE0710 module.

A 3.3V supply is also needed and must be supplied from the user's PCB. An output 3.3V supply is available on some of the board connector pins (see section 'Power Rails'). The input 3.3VIN will be switched to the internal 3.3V voltage level after the FPGA 1.0V supply is stable. Than 3.3V supply will be available on the B2B connector pins.

The regulators can be powered from the 3.3V supply or a 5V supply if preferred. The options for powering the board are as follows:

- Apply 5V to pins VIN and 3.3V to pins 3.3VIN on the board connector

- Apply 3.3V to pins VIN and 3.3VIN on the board connectors.

Power Rails

Voltages on B2B- Connectors | B2B JM1-Pin | B2B JM2-Pin | Direction | Note |

|---|---|---|---|---|

| VIN | 1, 3, 5 | 2, 4, 6, 8 | input | supply voltage |

| 3.3VIN | 13, 15 | - | input | supply voltage |

| VCCIO15 | 9, 11 | - | input | high range bank voltage |

| VCCIO34 | - | 7, 9 | input | high range bank voltage |

| 3.3V | 14 | 10, 12, 91 | output | internal 3.3V voltage level |

| 1.8V | 39 | - | output | internal 1.8V voltage level |

| 1.5V | - | 19 | output | internal 1.5V voltage level |

Table 8: Power rails of SoM on B2B connectors

Bank Voltages

| Bank | Schematic Name | Voltage | Range |

|---|---|---|---|

| 0 Config | 3.3V | 3.3V | - |

| 14 | 3.3V | 3.3V | - |

| 15 | VCCIO15 | user | HR: 1.2V to 3.3V |

| 16 | 3.3V | 3.3V | - |

| 34 | VCCIO34 | user | HR: 1.2V to 3.3V |

| 35 | 1.5V | 1.5V | - |

Table 9: Range of FPGA's bank voltages

See the Artix7 datasheet DS181 for the allowable voltage range.

Board to Board Connectors

| Include Page | ||||

|---|---|---|---|---|

|

Variants Currently In Production

Module Variant | FPGA | FPGA Junction Temperature | Operating Temperature Range |

|---|---|---|---|

| TE0710-02-100-2CF | XC7A100T-2CSG324C | 0°C to 85°C | commercial grade |

| TE0710-02-35-2CF | XC7A35T-2CSG324C | 0°C to 85°C | commercial grade |

| TE0710-02-100-2IF | XC7A100T-2CSG324I | -40°C to 100°C | industrial grade |

| TE0710-02-35-2IF | XC7A35T-2CSG324I | -40°C to 100°C | industrial grade |

| TE0710-02-100-1Q | XA7A100T-1CSG324Q | -40°C to 125°C | industrial grade |

Table 10: Differences between variants of Module TE0710-02

Technical Specifications

Absolute Maximum Ratings

Assembly options for cost or performance optimization available upon request.

Board Components

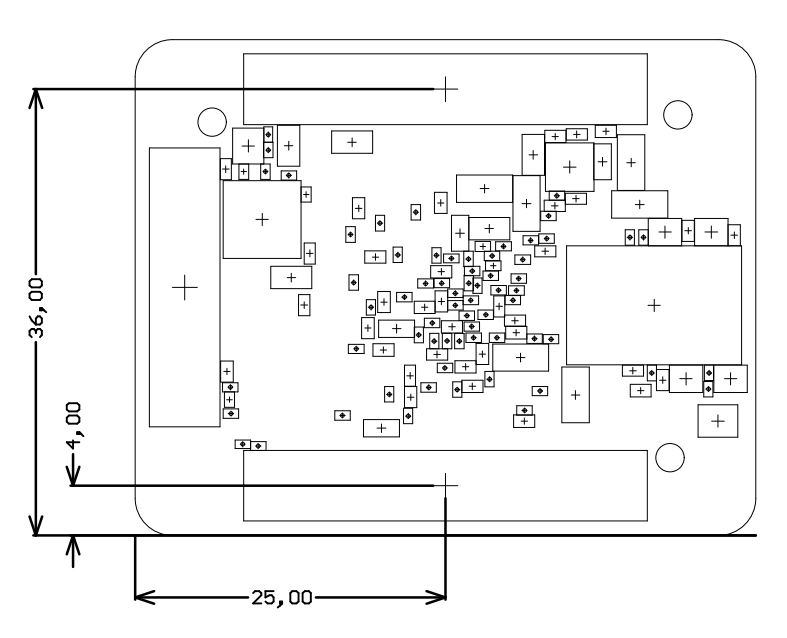

| |

Top view | Bottom view |

Detailed Description

PL Programmable Logic

The TE0710 board is populated with the Artix-7 Series Families FPGA. The devices can be programmed with the free Xilinx Vivado WebPACK software. Further information on the Artix-7 FPGA can be found in the Xilinx document 7 Series FPGAs Overview (DS180).

FPGA | Logic Cells | Flip-Flops | BRAM |

XC7A15T-2CSG324C | 16,640 | 20,800 | 25 |

XC7A35T-2CSG324C | 33,280 | 41,600 | 50 |

XC7A50T-2CSG324C | 52,160 | 65,200 | 75 |

XC7A75T-2CSG324C | 75,520 | 94,400 | 105 |

XC7A100T-2CSG324C | 101,440 | 126,800 | 135 |

Configuration Modes

The following two FPGA configuration interfaces are supported:

Mode | Setting | Notes |

JTAG | JTAG | For debugging purposes |

SPI Flash | SPI Master 4-bit mode | Main configuration mode: 4-Bit mode must be used when generating bitstream |

TE0710 Configuation pin settings

Config Pin | Setting | Notes |

| M0 | 3.3V | Bootmode setting: Master SPI

|

| M1 | 0V | |

| M2 | 0V | |

| CFGBVS | 3.3V | Select 3.3V as Config Bank I/O Voltage |

| PUDC | Strong pull-up to 3.3V | Pre-configuration pull-ups are DISABLED |

Configuration Memory

TE0710 standard assembly option includes 32MByte SPI Flash for configuration and data storage. This memory is large enough to hold at least 4 uncompressed FPGA Bitstreams.

Parameter | Value | Notes |

Memory size (MBytes) | 32 |

|

Vendor | Spansion | |

Device type | S25FL256SAGBHI20 |

|

Vivado CFGMEM | s25fl256sxxxxxx0-spi-x1_x2_x4 | Value to be used with Vivado labtools flash programmer |

Vivado Board Part File Interface name | SPI Flash |

Parameter values for the SPI Flash memory included in the standard assembly option.

XADC

XADC is configured with internal reference voltage option. All XADC inputs that are shared with FPGA I/O are available in the B2B Connector. There is no access to the dedicated XADC input pins.

Clock Sources

The TE0710 board has a 3.3V single ended 100MHz oscillator (U8). It is wired to an FPGA MRCC clock input on bank 35.

Oscillator: Si Time SiT8008AI-73-XXS-100.000000E (100 MHz)

Frequency stability: 50 ppm

IC Designator | Description | Frequency | Used as | FPGA Pin | IO Standard | Vivado Board Part Interface |

U8 | MEMS Oscillator | 100 MHz | System Clock | F4 | LVCMOS15 | System Clock |

In standard assembly option MEMS oscillator with 100MHz Frequency and 50 ppm stability is used. Other frequencies possible for custom order.

Reset Sources

Reset Type | Source | Notes |

| Power On Reset | System Controller | PROG_B released after power on causing FPGA reconfiguration |

| Config Reset | JM2.18 | Active low value forces FPGA reconfiguration |

| Dummy Reset | FPGA pin D9 | Can be used as reset with fixed always inactive value if needed (may have to add pullup or pulldown constraint) |

| Soft Reset | Any FPGA B2B I/O | User defined soft reset input with user defined polarity |

| Debug Reset | Microblaze MDM | JTAG debugger soft reset |

LED's

The TE0710 board has 3 LEDs. One is user led, which is connected to Pin L15 on the Bank 14. The other two are connected to the system controller.

LED | Color | IOSTANDARD | FPGA Pin | Description |

D1 | red | N/A | N/A | System controller status LED |

D2 | green | N/A | N/A | System controller status LED |

D3 | red | LVCMOS33 | L15 | User LED, active LOW |

JTAG

JTAG access is provided to the Xilinx Artix-7 FPGA (U5) and system controller (U4) through connector JM2. Selection of JTAG is controlled by the JTAGSEL pin (JM1.89) in connector JM1.

JTAG Bus Access

| Signal | B2B Module | B2B Base | Description |

|---|---|---|---|

| TCK | JM2: 99 |

| |

| TDI | JM2: 95 | . | |

| TDO | JM2: 97 | ||

| TMS | JM2: 93 | ||

| JTAGSEL | JM1: 89 | keep low or GND for normal operation |

| Note |

|---|

| The use of Xilinx legacy development tools (ISE, Impact) is not recommended. Impact does recognize only A100T, any smaller Artix is not even recognized as Xilinx FPGA by Impact. |

DDR3 Memory

The TE0710 board contains one DDR3 component with a capacity of 4Gb.

...

Configuration of the DDR3 memory controller in the FPGA should be done using the Xilinx MIG tool in the Vivado IP catalog. Refer to the reference design section (DDR3 Reference Design) for information on how to do this.

DDR3 Memory Connections to the FPGA

| FPGA Pin | FPGA Bank | I/O Standard | Comment |

| A4 | 35 | DIFF_SSTL15 | DDR3 Clock |

| A3 | 35 | DIFF_SSTL15 | DDR3 Clock |

| B1 | 35 | LVCMOS15 | DDR3 Reset |

| G6 | 35 | SSTL15 | DDR3 ODT |

| H5 | 35 | SSTL15 | DDR3 CS |

| H2 | 35 | SSTL15 | DDR3 CKE |

| J2 | 35 | SSTL15 | DDR3 RAS |

| H6 | 35 | SSTL15 | DDR3 CAS |

| G4 | 35 | SSTL15 | DDR3 WE |

| D3 | 35 | SSTL15 | DDR3 Address 0 |

| B2 | 35 | SSTL15 | DDR3 Address 1 |

| G1 | 35 | SSTL15 | DDR3 Address 2 |

| D4 | 35 | SSTL15 | DDR3 Address 3 |

| E1 | 35 | SSTL15 | DDR3 Address 4 |

| D2 | 35 | SSTL15 | DDR3 Address 5 |

| F1 | 35 | SSTL15 | DDR3 Address 6 |

| D5 | 35 | SSTL15 | DDR3 Address 7 |

| C1 | 35 | SSTL15 | DDR3 Address 8 |

| B3 | 35 | SSTL15 | DDR3 Address 9 |

| E3 | 35 | SSTL15 | DDR3 Address 10 |

| A1 | 35 | SSTL15 | DDR3 Address 11 |

| E2 | 35 | SSTL15 | DDR3 Address 12 |

| B4 | 35 | SSTL15 | DDR3 Address 13 |

| C2 | 35 | SSTL15 | DDR3 Address 14 |

| H1 | 35 | SSTL15 | DDR3 Address 15 |

| J4 | 35 | SSTL15 | DDR3 Bank0 |

| F3 | 35 | SSTL15 | DDR3 Bank1 |

| G2 | 35 | SSTL15 | DDR3 Bank2 |

| C5 | 35 | SSTL15 | DDR3 Data 0 |

| B7 | 35 | SSTL15 | DDR3 Data 1 |

| B6 | 35 | SSTL15 | DDR3 Data 2 |

| C6 | 35 | SSTL15 | DDR3 Data 3 |

| C7 | 35 | SSTL15 | DDR3 Data 4 |

| D8 | 35 | SSTL15 | DDR3 Data 5 |

| E5 | 35 | SSTL15 | DDR3 Data 6 |

| E7 | 35 | SSTL15 | DDR3 Data 7 |

| A6 | 35 | DIFF_SSTL15 | DDR3 Data Strobe |

| A5 | 35 | DIFF_SSTL15 | DDR3 Data Strobe |

| E6 | 35 | SSTL15 | DDR3 Data Mask |

Ethernet PHY

The TE0710 board has two 10/100M Ethernet PHY's TLK106 connected using MII interface to FPGA bank 14.

Ethernet PHY Connections

| FPGA Pin | FPGA Bank | Net Name | I/O Standard | Comment |

| U14 | 14 | ETH-RST | LVCMOS33 | Ethernet Reset, active-low |

| T14 | 14 | ETH_TXCLK | LVCMOS33 | Ethernet transmit clock input from PHY |

| R16 | 14 | ETH_TX_D0 | LVCMOS33 | Ethernet transmit data 0. Output to Ethernet PHY. |

| U18 | 14 | ETH_TX_D1 | LVCMOS33 | Ethernet transmit data 1. Output to Ethernet PHY. |

R18 | 14 | ETH_TX_D2 | LVCMOS33 | Ethernet transmit data 2. Output to Ethernet PHY. |

| R17 | 14 | ETH_TX_D3 | LVCMOS33 | Ethernet transmit data 3. Output to Ethernet PHY. |

| R15 | 14 | ETH_TX_EN | LVCMOS33 | Ethernet transmit enable. Output to Ethernet PHY. |

| N15 | 14 | ETH_RXCLK | LVCMOS33 | Ethernet receive clock input from PHY. |

| U12 | 14 | ETH_RX_D0 | LVCMOS33 | Ethernet receive data 0. Input from Ethernet PHY. |

| V12 | 14 | ETH_RX_D1 | LVCMOS33 | Ethernet receive data 1. Input from Ethernet PHY. |

| U13 | 14 | ETH_RX_D2 | LVCMOS33 | Ethernet receive data 2. Input from Ethernet PHY. |

| T15 | 14 | ETH_RX_D3 | LVCMOS33 | Ethernet receive data 3. Input from Ethernet PHY. |

| V10 | 14 | ETH_RX_DV | LVCMOS33 | Ethernet receive data valid. Input from Ethernet PHY. |

| V11 | 14 | ETH_RX_ER | LVCMOS33 | Ethernet receive error. Input from Ethernet PHY. |

| T9 | 14 | ETH_COL | LVCMOS33 | Ethernet collision detect input from Ethernet PHY. |

| T18 | 14 | ETH_INT | LVCMOS33 | Ethernet power down or interrupt. (default function is power down) |

| V15 | 14 | LINK_LED | LVCMOS33 | Ethernet LED Pin to indicate status. Mode 1: LINK Indication LED; Mode 2: ACT Indication LED |

| T13 | 14 | MDC | LVCMOS33 | Ethernet to PHY MII Management clock |

| V14 | 14 | MDIO | LVCMOS33 | PHY MDIO data I/O ( 3-state buffer) |

| P17 | 14 | ETH2_TXCLK | LVCMOS33 | Ethernet 2 transmit clock input from PHY. |

| M13 | 14 | ETH2_TX_D0 | LVCMOS33 | Ethernet 2 transmit data 0. Output to Ethernet PHY. |

M16 | 14 | ETH2_TX_D1 | LVCMOS33 | Ethernet 2 transmit data 1. Output to Ethernet PHY. |

| M17 | 14 | ETH2_TX_D2 | LVCMOS33 | Ethernet 2 transmit data 2. Output to Ethernet PHY. |

| L16 | 14 | ETH2_TX_D3 | LVCMOS33 | Ethernet 2 transmit data 3. Output to Ethernet PHY. |

| N16 | 14 | ETH2_TX_EN | LVCMOS33 | Ethernet 2 transmit enable. Output to Ethernet PHY. |

| p15 | 14 | ETH2_RXCLK | LVCMOS33 | Ethernet 2 receive clock input from PHY. |

| V17 | 14 | ETH2_RX_D0 | LVCMOS33 | Ethernet 2 receive data 0. Input from Ethernet PHY. |

| T16 | 14 | ETH2_RX_D1 | LVCMOS33 | Ethernet 2 receive data 1. Input from Ethernet PHY. |

| U17 | 14 | ETH2_RX_D2 | LVCMOS33 | Ethernet 2 receive data 2. Input from Ethernet PHY. |

| N17 | 14 | ETH2_RX_D3 | LVCMOS33 | Ethernet 2 receive data 3. Input from Ethernet PHY. |

| R11 | 14 | ETH2_RX_DV | LVCMOS33 | Ethernet 2 receive data valid. Input from Ethernet PHY. |

| U16 | 14 | ETH2_RX_ER | LVCMOS33 | Ethernet 2 receive error. Input from Ethernet PHY. |

| P14 | 14 | ETH2_COL | LVCMOS33 | Ethernet 2 collision detect input from Ethernet PHY. |

| D10 | 16 | ETH2_INT | LVCMOS33 | Ethernet 2 power down or interrupt |

| T10 | 14 | LINK_LED2 | LVCMOS33 | Ethernet LED Pin to indicate status. Mode 1: LINK Indication LED; Mode 2: ACT Indication LED |

| N14 | 14 | MDC2 | LVCMOS33 | Ethernet 2 to PHY MII 2 Management clock |

| P18 | 14 | MDIO2 | LVCMOS33 | PHY MDIO data I/O ( 3-state buffer) |

MAC Address EEPROM

The TE0710 board has a UNI/O serial EEPROM with EUI-48™ Node Identity. This device is a 2 Kbit Serial Electrically Erasable PROM. It is organized in blocks of x8-bit memory and supports single I/O UNI/O® serial bus. It has a built-in 48-bit Extended Unique Identifier (EUI) that is needed to identify the network hardware’s physical address. These built-in MAC addresses enable designer to buy addresses only when needed, and also eliminate the need for serialization and programming. The address is also EUI-64 compatible, and it is write-protected to ensure tamper-proof designs. It contains an 8-bit instruction register and is accessed via the SCIO pin. The Address Data is embedded into the I/O stream through Manchester encoding. The bus is controlled by a master device which determines the clock period, controls the bus access and initiates all operations, while the serial EEPROM works as slave.

- Part number: 11AA02E48T-I/TT (Microchip)

- Supply voltage: 3.3V

Pre-programmed Globally Unique, 48-bit Node Address

- Compatible with EUI-48™ and EUI-64™

- 256 x 8 Bit Organization

| FPGA Pin | Bank | I/O Standard | Comment | Function |

|---|---|---|---|---|

| D9 | 16 | LVCMOS33 | Serial bit stream (SCIO) | Serial Clock, Data Input/Output |

For more information about this device, please refer to the Microchip 11AA02E48 Datasheet.

Board-to-Board Connectors

...

View and download the connector pinout for this module in the master pinout table here: Master Pinout Table

Initial Delivery state

Storage device name | Content | Notes |

| SPI Flash OTP Area | Empty, not programmed | Except serial number programmed by flash vendor |

| SPI Flash Quad Enable bit | Programmed | Must be programmed for SPI Flash Boot |

| SPI Flash main array | demo design | |

| EFUSE USER | Not programmed | |

| EFUSE Security | Not programmed |

Revision History For This Product

Revision | Changes |

02 | Current Hardware Revision |

Technical Specification

Absolute Maximum Ratings

Parameter | Min | Max | Units | Notes |

Vin supply voltage | -0.3 | 6.0 | V |

|

Vin33 supply voltage | -0.4 | 3.6 | V |

|

I/O voltage on any FPGA I/O | -0.4 | Vcco+0.55 | V | |

Voltage on JTAG pins | -0.5 | 3.75 | V | When Vin33 is powered |

Storage Temperature | -40 | +100 | C |

|

...

| Parameter | Min | Max | Units | Notes |

|---|

VIN supply voltage |

| -0. |

| 3 |

| 7. |

| 0 | V |

| EN6347QI / EN5311QI data sheet | ||||

| 3.3VIN supply voltage | -0.1 | 3.6 | V | - |

| PL IO bank supply voltage for HR I/O Banks (VCCO) | -0.5 | 3.6 | V | - |

| I/O input voltage for HR I/O banks |

| Note |

|---|

| Please check Xilinx Datasheet for complete list of Absolute maximum and recommended operating ratings for the Artix-7 device (DS181). |

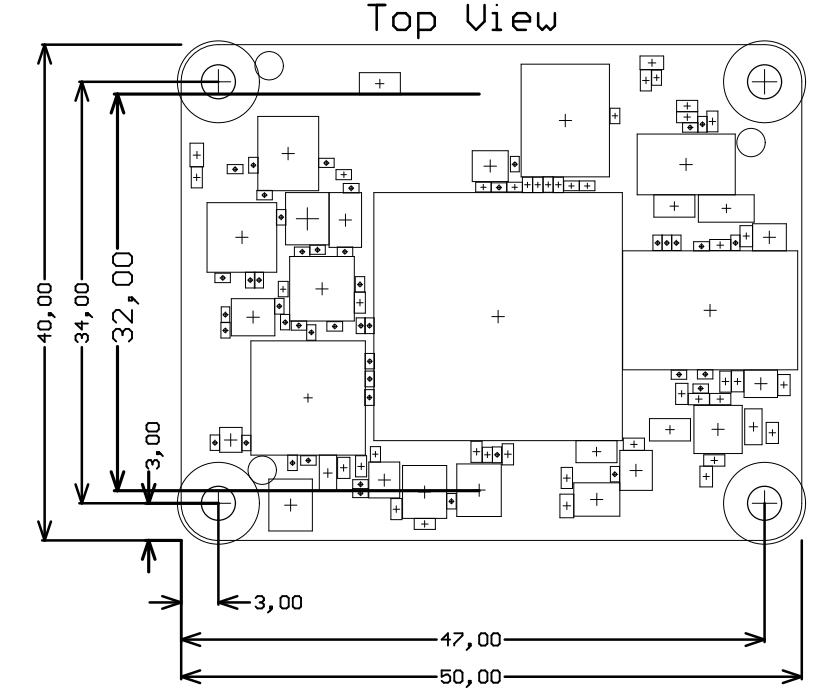

Physical Dimensions

Module size: 50 mm × 40 mm. Please download the assembly diagram for exact numbers.

Mating height with standard connectors: 8mm

PCB thikness: 1.6mm

- Highest part on PCB: approx. 2.5mm. Please download the step model for exact numbers.

Download physical dimensions here: TE0710 Physical Dimensions

Power Supplies

Vin | 3.3 V to 5.5 V | Typical 200mA, depending on customer design and connections. |

Vin 3.3 V | 3.3 V | Typical 50mA, depending on customer design and connections. |

For startup, a power supply with minimum current capability of 2A is recommended.

| Tip |

|---|

Vin and Vin 3.3V can be connected to the same source (3.3 V). |

Temperature Ranges

Commercial grade modules | 0 °C to +70 °C |

Industrial grade modules | -40 °C to +85 °C |

| Note |

|---|

Depending on the customer design, additional cooling might be required. |

Weight

| -0.4 | VCCO_X+0.55 | V | - | |

| Voltage on module JTAG pins | -0.5 | VCCO_0+0.45 | V | VCCO_0 is 3.3V nominal. |

| Storage temperature | -55 | +100 | °C | - |

Table 11: Absolute maximum ratings

Recommended Operation Conditions

| Parameter | Min | Max | Units | Notes | Reference Document |

|---|---|---|---|---|---|

| VIN supply voltage | 2.4 | 5.5 | V | - | EN5311QI data sheet |

| 3.3VIN supply voltage | 3.135 | 3.465 | V | - | 3,3V ± 5% |

| PL I/O bank supply voltage for HR I/O banks (VCCO) | 1.14 | 3.465 | V | - | Xilinx datasheet DS181 |

| I/O input voltage for HR I/O Banks | - 0.20 | VCCO + 0.2 | V | - | Xilinx datasheet DS181 |

| Voltage on Module JTAG pins | 3.135 | 3.465 | V | - | 3,3V ± 5% |

Table 12: Recommended operation conditions

| Note |

|---|

| Please check Xilinx datasheet (DS181) for complete list of absolute maximum and recommended operating ratings. |

Operating Temperature Ranges

Commercial grade: 0°C to +70°C.

Industrial grade: -40°C to +85°C.

The module operating temperature range depends also on customer design and cooling solution. Please contact us for options.

Physical Dimensions

- Module size: 50 mm × 40 mm. Please download the assembly diagram for exact numbers.

- Mating height with standard connectors: 8mm

- PCB thickness: 1.6mm

- Highest part on PCB: approx. 2.5mm. Please download the step model for exact numbers.

All dimensions are shown in mm.

Figure 3: Physical Dimensions of the TE0710-02 board

Weight

| 11 |

| .5 g | without bolts |

| 20.3 g | with bolts |

Downloads For This Product

Recommended Software: Xilinx Vivado WebPACK (free license)

| Note |

|---|

A15T, A35T, A50T, A75T are not supported by Xilinx legacy tools (ISE, Impact). |

The schematic is available for download here: TE0710 Schematic

Resources

...

Revision History

Hardware Revision History

| Date | Revision | Notes | PCN | Documentation link |

|---|---|---|---|---|

| 02 | Current Hardware Revision | |||

| 01 | First production release |

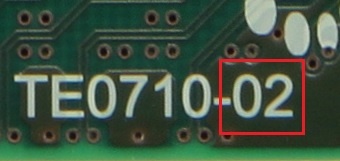

Hardware revision number is printed on the PCB board together with the module model number separated by the dash.

Document Change History

| Date | Revision |

|---|

| Contributors | Description |

|---|---|

| 2016- |

| 12- |

| 19 |

| Ali Naseri |

TRM revision |

| 2015- |

| 01- |

| 23 | 0.1 |

| initial version |

Disclaimer

| Include Page | ||||

|---|---|---|---|---|

|