Page History

| scroll-ignore |

|---|

Download PDF version of this document. |

| scroll-pdf-ignore | |

|---|---|

Table of Contents

|

...

| Scroll Only (inline) |

|---|

On https://wiki.trenz-electronic.de/display/PD/TE0729+TRM the online version of this manual and other documents can be found. |

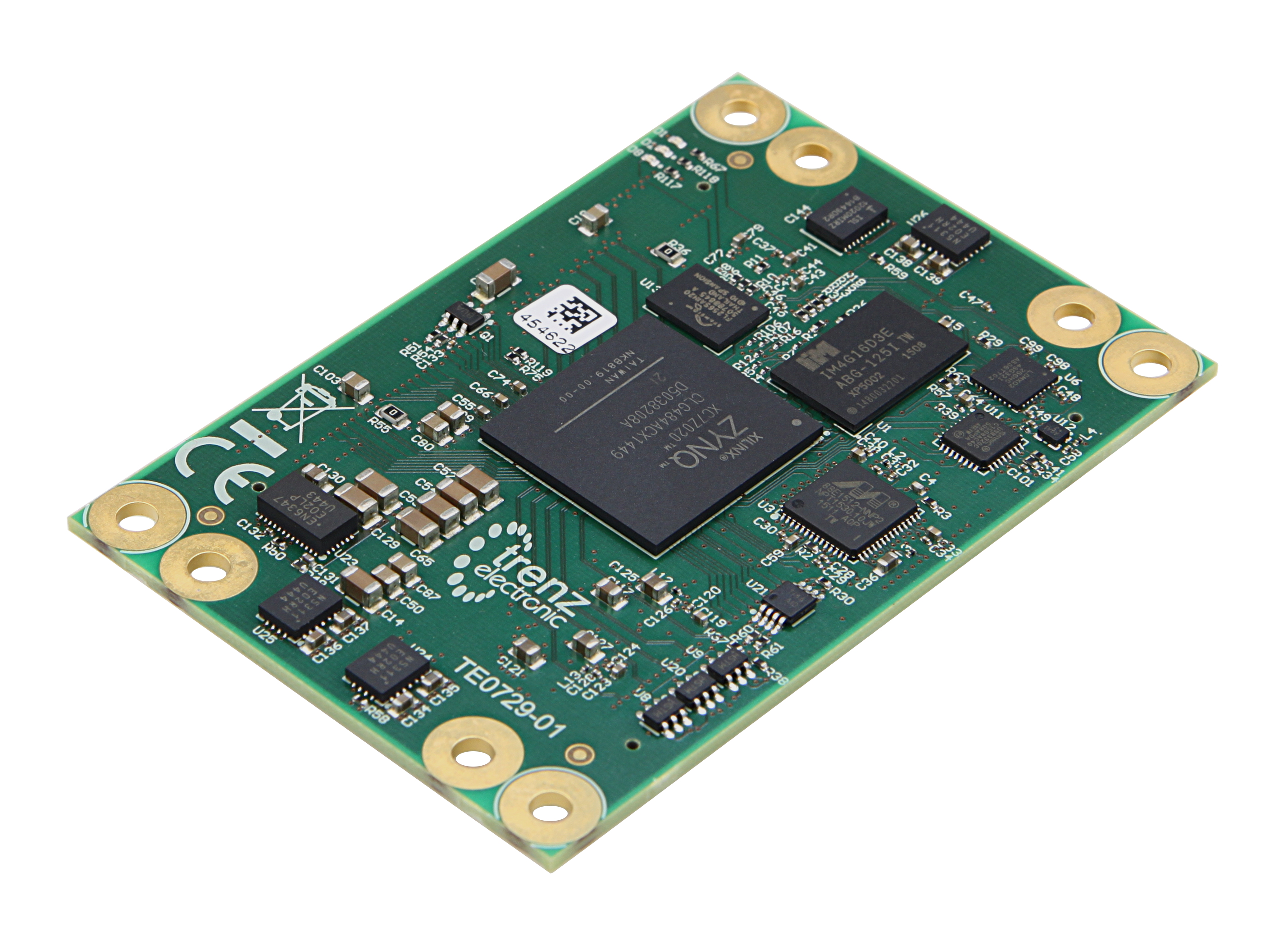

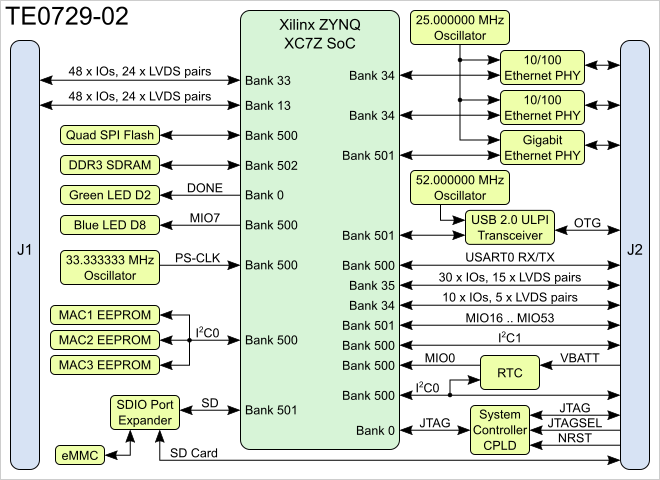

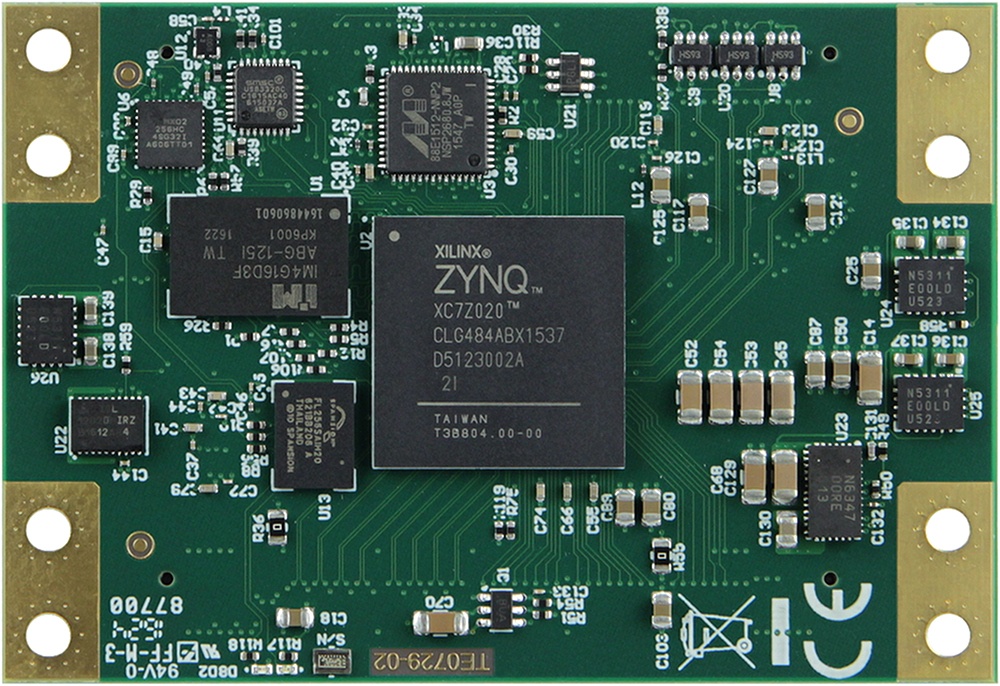

The Trenz Electronic TE0729 is an industrial-grade SoM (System on Module) based on Xilinx Zynq-7000 SoC (XC7Z020).

This SoM has following peripherals on board:

- 1 x Gbps Ethernet PHY transceiver

- 2 x 100 Mbps Ethernet PHY transceivers

- 512 MByte DDR3 Memory

- 32 MByte SPI Flash Memory

- eMMC (4 GByte in standard configuration)

- USB PHY transceiver

- powerful switch-mode power supplies for all on-board voltages

- large number of configurable I/Os

Block Diagramm

Key Features

- Industrial-grade Xilinx Zynq-7000 (XC7Z020) SoM

- Rugged for shock and high vibration

- 2 x ARM Cortex-A9

- 1 x 10/100/1000 Mbps Ethernet transceiver PHY

- 2 x 10/100 Mbps Ethernet transceiver PHY's

- 3 x MAC-Address EEPROM's

- 16-Bit wide 512 MByte DDR3 SDRAM

- 32 MByte QSPI Flash memory

- 4 GByte e-NAND Flash memory (embedded eMMC Memory)

- USB 2.0 high-speed ULPI transceiver

- Plug-on module with two 120-pin connectors

- Evenly-spread supply pins for good signal integrity

- 136 FPGA I/Os (58 LVDS pairs possible)

- 8 PS MIO pins

- On-board high-efficiency DC-DC converters

- 4.0 A x 1.0 V power rail

- 1.5 A x 1.5 V power rail

- 1.5 A x 1.8 V power rail

- 1.5 A x 2.5 V power rail

- System management

- eFUSE bit-stream encryption

- AES bit-stream encryption

- Temperature compensated RTC (real-time clock)

- User LED

Assembly options for cost or performance optimization available upon request.

Signals, Interfaces and Pins

System Controller I/O Pins

Special purpose pins used by TE0729

...

Boot Modes

TE0729 supports primary boot from

- JTAG

- SPI Flash

- SD Card

Boot from on-board eMMC is also supported as secondary boot (FSBL must be loaded from SPI Flash).

The boot modes are controlled by the Pins 'BOOT1' and 'BOOT2' on the board to board (B2B) connector. Pins routed through the CPLD by default firmware with pullup, if not connected on B2B.

...

BOOTMODE2 (M3)

...

JTAG

JTAG access to the Xilinx Zynq-7000 device is provided by connector J2.

...

| Note |

|---|

JTAGSEL pin in J2 should be kept low or grounded for normal operation. |

Clocking

...

Processing System (PS) Peripherals

...

Default MIO mapping

...

53

...

I2C Interface

The on-board I2C components are connected to MIO10 and MIO11 and configured as I2C0 by default.

I2C addresses for on-board components

...

B2B I/O

Number of I/O's connected to the SoC's I/O bank and B2B connector

...

J2-87

J2-88

...

J2-93

J2-95

J2-94

J2-96

...

configured as I2C1 and USART0 by default,

configurable as GPIO by user

...

configured as DISP_RX by default,

configurable as GPIO by user

For detailed information about the pin out, please refer to the Master Pin-out Table.

Peripherals

LED's

There are 3 LED's on TE0729:

...

Key Features

- Industrial-grade Xilinx Zynq-7000 (XC7Z020) SoM

- Dual-core ARM Cortex-A9 MPCore™ with CoreSight™

- 136 x FPGA I/Os (58 LVDS pairs possible)

- 8 x PS MIO pins

- 16-bit wide 512 MByte DDR3 SDRAM

- 32 MByte QSPI Flash memory

- 4 GByte eMMC Flash memory

- 1 x 10/100/1000 Mbps Ethernet transceiver PHY

- 2 x 10/100 Mbps Ethernet transceiver PHY's

- 3 x MAC address EEPROM's

- Hi-speed USB 2.0 ULPI transceiver with full OTG support

- Plug-on module with two 120-pin connectors

- Evenly-spread supply pins for good signal integrity

- On-board high-efficiency DC-DC converters

- 4.0 A x 1.0 V power rail

- 1.5 A x 1.5 V power rail

- 1.5 A x 1.8 V power rail

- 1.5 A x 2.5 V power rail

- System management

- eFUSE bit-stream encryption

- AES bit-stream encryption

- Temperature compensated RTC (real-time clock)

- User LED

- Rugged for shock and high vibration

Assembly options for cost or performance optimization available upon request.

Block Diagram

Main Components

Initial Delivery State

| Storage device name | Content | Notes |

|---|---|---|

24AA025E48 EEPROM's | User content not programmed | Valid MAC Address from manufacturer |

| eMMC Flash-Memory | Empty, not programmed | Except serial number programmed by flash vendor |

SPI Flash OTP Area | Empty, not programmed | Except serial number programmed by flash vendor |

SPI Flash Quad Enable bit | Programmed | |

SPI Flash main array | demo design | |

eFUSE USER | Not programmed | |

eFUSE Security | Not programmed |

Signals, Interfaces and Pins

Board to Board (B2B) I/Os

| Bank | Type | B2B | IO count | IO Voltage | Notes |

|---|---|---|---|---|---|

| 500 | MIO | J2-87 J2-88 | 2 | 3,3 V | MIO0, MIO9 |

| 500 | MIO | J2-93 J2-95 J2-94 J2-96 | 4 | 3,3 V | Configured as I2C1 and USART0 by default, Configurable as GPIO by user |

| 13 | HR | J1 | 48 | User | |

| 33 | HR | J1 | 48 | User | |

| 35 | HR | J2 | 30 | 3,3 V | |

| 34 | GPIO | J2 | 10 | 2,5 V | Configured as DISP_RX by default, Configurable as GPIO by user |

For detailed information about the pin out, please refer to the Master Pin-out table.

JTAG Interface

JTAG access to the Xilinx Zynq-7000 device is provided through connector J2.

| Signal | B2B Pin |

|---|---|

| TCK | J2-119 |

| TDI | J2-115 |

| TDO | J2-117 |

| TMS | J2-113 |

| Note |

|---|

JTAGSEL pin in J2 should be kept low or grounded for normal operation. |

System Controller I/O Pins

Special purpose pins used by TE0729:

| Name | Note |

|---|---|

| NRST | Reset-Signal from Watchdog, available at B2B J2-89 |

| NRST_IN | External Reset, available at B2B J2-91 |

On-board LEDs

There are 3 LED's on TE0729:

| LED | Color | Connected to | Notes |

|---|---|---|---|

| D1 | red | System Controller | Global Status LED |

| D2 | green | DONE | Inverted DONE, ON when FPGA not configured |

| D8 | red | MIO7 | OFF when PS7 not booted and not controlling MIO7 by software, else user controlled |

| Note |

|---|

LED D2 is connected to the FPGA Done pin and will go off as soon as PL is configured. This LED will not operate if the System Controller can not power on the 3.3V output rail that also powers the 3.3V circuitry on the module. |

Clocking

| Clock | Frequency | IC | FPGA | Notes |

|---|---|---|---|---|

| PS CLK | 33.3333 MHz | U14 | PS_CLK | PS Subsystem main clock |

| 10/100/1000 Mbps ETH PHY reference | 25 MHz | U10 | - | |

| USB PHY reference | 52 MHz | U12 | - |

Default MIO mapping

| MIO | Configured as | B2B | Notes |

|---|---|---|---|

| 0 | GPIO | J2-87 | B2B |

| 1 | QSPI0 | - | SPI Flash-CS |

| 2 | QSPI0 | - | SPI Flash-DQ0 |

| 3 | QSPI0 | - | SPI Flash-DQ1 |

| 4 | QSPI0 | - | SPI Flash-DQ2 |

| 5 | QSPI0 | - | SPI Flash-DQ3 |

| 6 | QSPI0 | - | SPI Flash-SCK |

| 7 | GPIO | - | Red LED D8 |

| 8 | - | - | QSPI feedback clock |

| 9 | GPIO | J2-88 | B2B |

| 10 | I2C0 SDA | J2-90 | B2B |

| 11 | I2C0 SCL | J2-92 | B2B |

| 12 | I2C1 SDA | J2-93 | B2B (SDA on-board I2C, also configurable as GPIO by user) |

| 13 | I2C1 SCL | J2-95 | B2B (SCL on-board I2C, also configurable as GPIO by user) |

| 14 | USART0 RX | J2-94 | B2B (RX on-board UART, also configurable as GPIO by user) |

| 15 | USART0 TX | J2-96 | B2B (TX on-board UART, also configurable as GPIO by user) |

| 16..27 | ETH0 | Ethernet RGMII PHY | |

| 28..39 | USB0 | USB ULPI PHY | |

| 40 | SDIO0 | J2-100 | |

| 41 | SDIO0 | J2-102 | |

| 42 | SDIO0 | J2-104 | |

| 43 | SDIO0 | J2-106 | |

| 44 | SDIO0 | J2-108 | |

| 45 | SDIO0 | J2-110 | |

| 46 | GPIO | - | RTC Interrupt |

| 47 | - | - | - |

| 48 | GPIO | SEL_SD | SD Card multiplexer control |

| 49 | GPIO | - | USB Reset |

| 50 | GPIO | - | ETH0 Interrupt |

| 51 | GPIO | - | ETH0 Reset |

| 52 | ETH0 | - | MDC |

53 | ETH0 | - | MDIO |

Boot Modes

TE0729 supports primary boot from

- JTAG

- SPI Flash

- SD Card

Boot from on-board eMMC is also supported as secondary boot (FSBL must be loaded from SPI Flash).

The boot modes are controlled by the Pins 'BOOT1' and 'BOOT2' on the board to board (B2B) connector. Pins routed through the CPLD by default firmware with pull-up, if not connected on B2B.

BOOTMODE2 (M3) | BOOTMODE1 (M2) | M1 | M0 | Boot mode |

|---|---|---|---|---|

| LOW | LOW | LOW | LOW | JTAG |

| LOW | HIGH | LOW | LOW | Invalid |

| HIGH | LOW | LOW | LOW | SPI (eMMC as secondary boot possible) |

| HIGH | HIGH | LOW | LOW | SD Card |

Processing System (PS) Peripherals

| Peripheral | IC | Designator | PS | MIO | Notes |

|---|---|---|---|---|---|

| EEPROM I2C | 24AA025E48T-I/OT | U8 | I2C0 | MIO10, MIO11 | MAC Address |

| EEPROM I2C | 24AA025E48T-I/OT | U9 | I2C0 | MIO10, MIO11 | MAC Address |

| EEPROM I2C | 24AA025E48T-I/OT | U20 | I2C0 | MIO10, MIO11 | MAC Address |

| RTC | ISL12020MIRZ | U22 | I2C0 | MIO10, MIO11 | Temperature compensated real time clock |

| RTC Interrupt | ISL12020MIRZ | U22 | GPIO | MIO46 | Real Time Clock Interrupt |

| SPI Flash | S25FL256SAGBHI20 | U13 | QSPI0 | MIO1..MIO6 | |

| Ethernet0 10/100/1000 Mbps PHY | 88E1512-A0-NNP2I000 | U3 | ETH0 | MIO16...MIO27 | |

| Ethernet0 10/100/1000 Mbps PHY Reset | GPIO | MIO51 | |||

| Ethernet1 10/100 Mbps PHY | KSZ8081MLXCA | U17 | - | (EMIO) | |

| Ethernet1 10/100 Mbps PHY Reset | - | (EMIO) | |||

| Ethernet2 10/100 Mbps PHY | KSZ8081MLXCA | U19 | - | (EMIO) | |

| Ethernet2 10/100 Mbps PHY Reset | - | (EMIO) | |||

| USB | USB3320C-EZK | U11 | USB0 | MIO28...MIO39 | |

| USB Reset | GPIO | MIO49 | |||

| eMMC (embedded eMMC) | MTFC4GMVEA-4M IT | U5 | SDIO0 | MIO40...MIO45 |

I2C Interface

The on-board I2C components are connected to MIO10 and MIO11 and configured as I2C0 by default.

I2C addresses for on-board components

| Device | I2C-Address | Notes |

|---|---|---|

| EEPROM for MAC1 | 0x50 | |

| EEPROM for MAC2 | 0x51 | |

| EEPROM for MAC3 | 0x52 | |

| RTC | 0x6F | |

| Battery backed RAM | 0x57 | Integrated in RTC |

On-board Peripherals

Gigabit Ethernet

The TE0729 is equipped with

| Note |

|---|

LED D2 is connected to the FPGA Done pin and will go off as soon as PL is configured. This LED will not operate if the System Controller can not power on the 3.3V output rail that also powers the 3.3V circuitry on the module. |

Ethernet

The TE0729 is equipped with a Marvell Alaska 88E1512 Gigabit Ethernet PHY (U3) connected to PS Ethernet GEM0 (referenced in this manual Ethernet0). The I/O Voltage is fixed at 1.8V. The reference clock input of the PHY is supplied from an on board 25MHz oscillator (U10).

...

All other pins of the PHYs are connected to Bank34 of Zynq, see schematic for further details.

USB Interface

The USB PHY USB3320 from Microchip is used on the TE0729. The ULPI interface is connected to the Zynq PS USB0. The I/O Voltage is fixed at 1.8V.

...

The schematic for the USB connector and required components is different depending on the USB usage. USB standard A or B connectors can be used for Host or Device modes. A Mini USB connector can be used for USB Device mode. A USB Micro connector can be used for Device mode, OTG Mode or Host Mode.

RTC - Real Time Clock

An Intersil temperature compensated real time clock IC ISL12020MIRZ is used for timekeeping (U22). Battery voltage must be supplied to the module from the main board.

...

Watchdog

TE0729 has support for Hardware hardware watchdog function. With standard variant, the Watchdog watchdog is disabled at power up. Please contact Trenz Electronic for details how to enable Watchdog watchdog function.

Power and Power-On Sequence

For startup, a power supply with minimum current capability of 3A is recommended.

...

Supply Voltage | Voltage Range | NoteNotes |

|---|---|---|

VIN | 3.3 V to 5.5 V |

|

| VIN 3.3V | 3.3 V |

|

Bank Voltages

| Bank | Voltage | maxMax. Value | noteNotes |

|---|---|---|---|

| 501 | 1,8 V | - | ETH0 / USB0 / SDIO0 |

| 500 | 3,3 V | - | SPI / I2C / UART |

| 502 | 1,5 V | - | DDR3-RAM |

| 13 | user | 3,3 V | connected to 3,3V by default by 0-Ohm-Resistor R36 |

| 33 | user | 3,3 V | connected to 3,3V by default by 0-Ohm-Resistor R55 |

| 34 | 2,5 V | - | ETH / DISP |

| 35 | 3,3 V | - | GPIO |

...

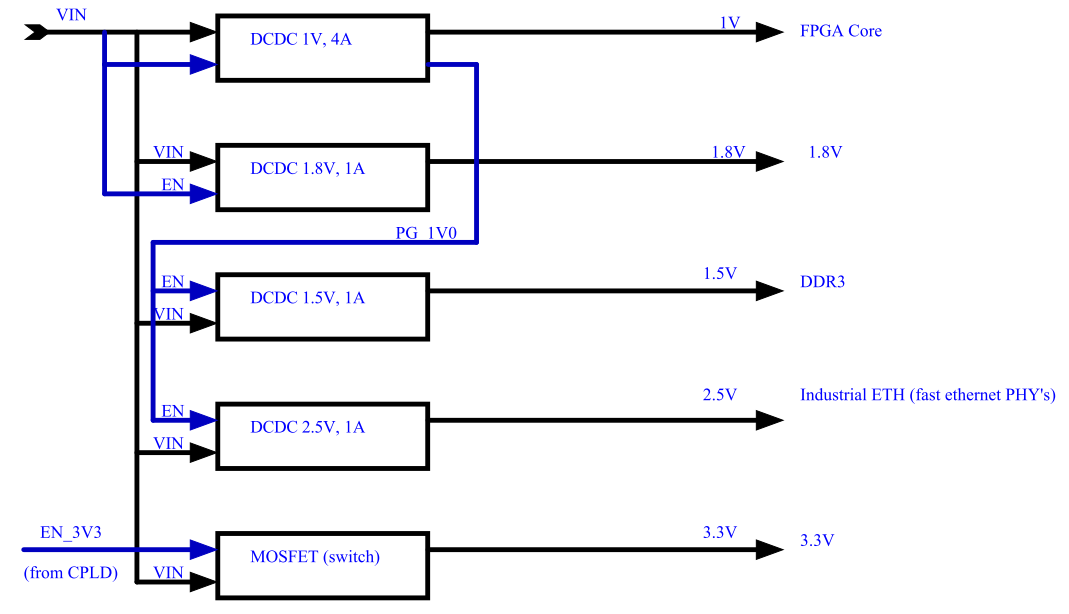

The Trenz TE0729 is equipped with several DC-DC-voltage-regulators to generate the required on-board voltages with the values 1V (FPGA core), 1.8 V (VCC0 MIO, VCCAUX, AVCC, VCCPLL, VDD USB and ETH PHYs), 1.5V (DDR3), 2.5V (Industrial fast ETH-PHY'sPHYs) and 3.3V (VCCIO, pheripheral peripheral components).

In the first step at device start-up the voltages 1V and 1.8V are generated for the FPGA core and programmable logic banks. The voltages 1.5V and 2.5 V are enabled after the voltage 1V has stabilized. The voltage 3.3V is enabled by the CPLD system controller at last.

The voltage 3.3V is available on B2B-connector at pins J1-65, J1-66 and an indicator for stabilized on-board voltages in steady state.

| Warning |

|---|

| To avoid any damages damage to the SoM, check the 3.3V voltage before powering up the SoC's I/O bank voltages VCCIO_13 and VCCIO_33. |

Pay attention to the voltage level of the I/O-signals, which must not be higher thenthan VCCIO + 0.4V.

Initial Delivery state

...

24AA025E48 EEPROM's

...

User content not programmed

...

SPI Flash OTP Area

...

Empty, not programmed

...

Except serial number programmed by flash vendor

...

SPI Flash Quad Enable bit

...

Programmed

...

SPI Flash main array

...

demo design

...

EFUSE USER

...

Not programmed

...

EFUSE Security

...

Not programmed

...

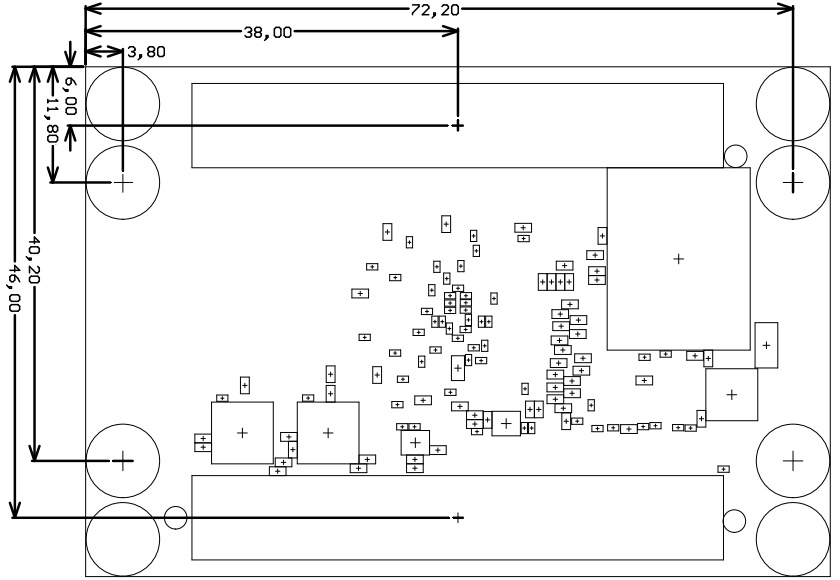

Board to Board Connectors

The TE0729 module has two 120-pin double-row REF-189019-02 connectors on the bottom side which are compatible with Samtec BTE-060-01-L-D-A connectors. Mating connectors on the baseboard are REF-189019-01, which are compatible with Samtec BSE-060-01-L-D-A connectors.

Connector Specifications

Hardware Revision History

...

01

...

Prototypes

...

Technical Specification

Absolute Maximum Ratings

| Parameter | Min | Max | Units | Notes |

|---|---|---|---|---|

Vin supply voltage | -0.1 | 3.75 | V | |

| VBAT supply voltage | -0.3 | 6.0 | V | |

| PL IO Bank supply voltage for HR I/O banks (VCCO) | -0.5 | 3.6 | V | |

| I/O input voltage for HP I/O banks | -0.55 | VCCO_X+0.55 | V | TE0729 does not have HP banks |

Voltage on Module JTAG pins | -0.4 | VCCO_0+0.55 | V | VCCO_0 is 3.3V nominal |

Storage Temperature | -40 | +85 | C | |

| Storage Temperature without the ISL12020MIRZ | -55 | +100 | C |

| Note |

|---|

| Assembly variants for higher storage temperature range on request |

...

| Parameter | Min | Max | Units | Notes | Reference document |

|---|---|---|---|---|---|

| Vin supply voltage | 2.5 | 3.6 | V | ||

| VBAT supply voltage | 1.8 | 5.5 | V | ||

| PL IO Bank supply voltage for HR I/O banks (VCCO) | 1.14 | 3.465 | V | Xilinx document DS191 | |

| I/O input voltage for HR I/O banks | (*) | (*) | V | (*) Check datasheet | Xilinx document DS191 and DS187 |

| Voltage on Module module JTAG pins | 3.135 | 3.465 | V | VCCO_0 is 3.3 V nominal |

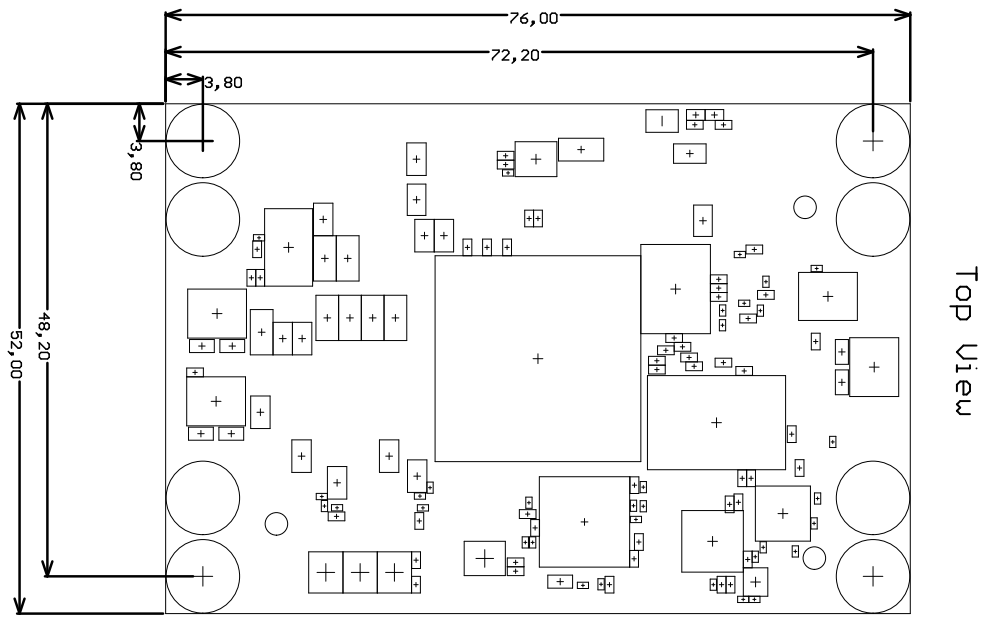

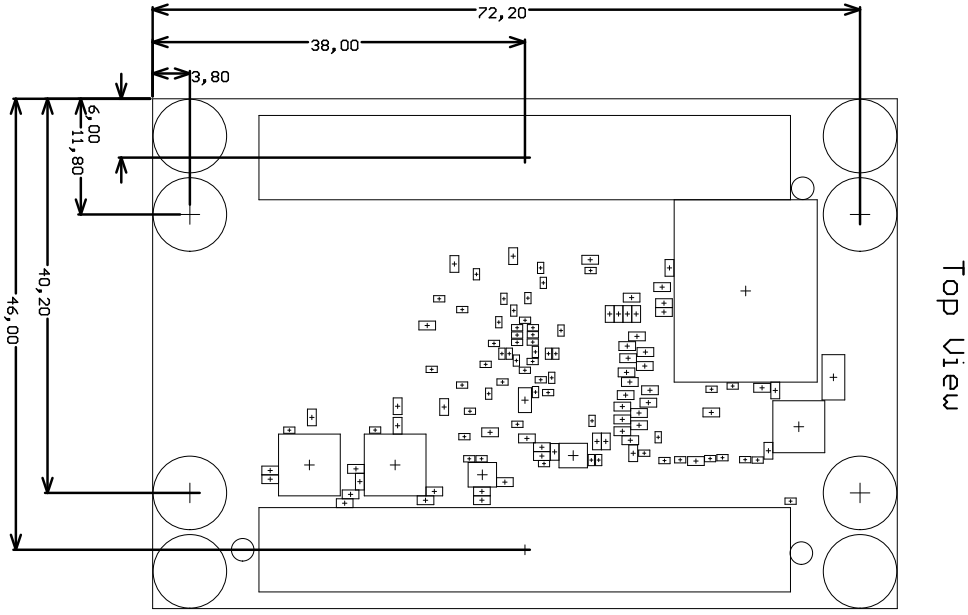

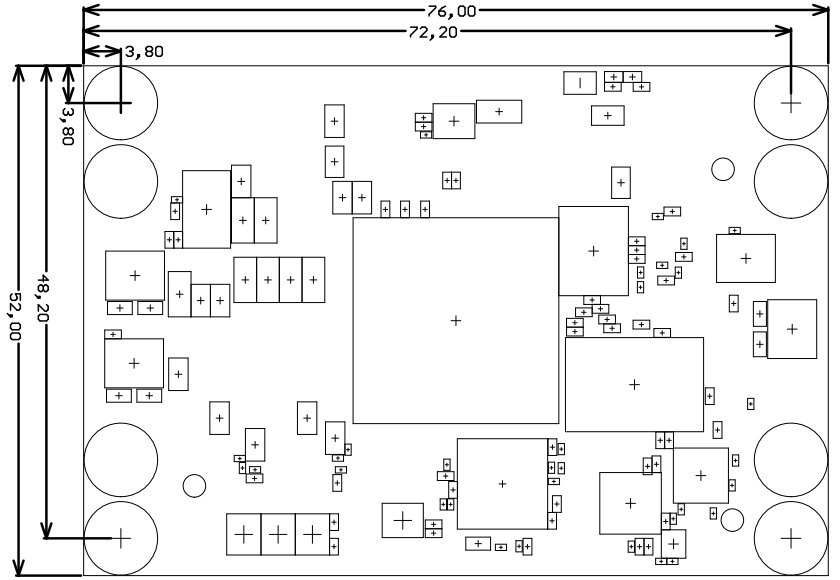

Physical Dimensions

...

Module size: 76 mm × 52 mm.

Mating height with standard connectors: 4,25 mm.

PCB thickness: 2 mm.

All dimensions are shown in mmmillimeters.

...

Weight

...

Part

...

21,6 g

...

Plain module

Operating Temperature Ranges

Commercial grade modules

All parts are at least commercial temperature range of 0°C to +70°C.

Industrial grade modules

All parts are at least industrial temperature range of -40°C to +85°C.

The module operating temperature range depends on customer design and cooling solution. Please contact us for options.

Industrial grade modules

All parts are at least industrial temperature range of -40°C to +85°C. The module operating temperature range depends on customer design and cooling solution. Please contact us for options.

Document Change History

. Please contact us for options.

Weight

Weight | Part |

|---|---|

21,6 g | Plain module |

Revision History

Hardware Revision History

| Date | Revision | Changes |

|---|---|---|

| 2016-05-02 | 02 | First production release |

01 | Prototypes |

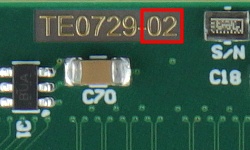

Hardware revision number is written on the PCB board together with the module model number separated by the dash.

Document Change History

| Date | Revision | Contributors | Description | ||||

|---|---|---|---|---|---|---|---|

2017-05-22 | Jan Kumann | Sections rearranged for common style. New physical dimension images. Hardware revision image added. New block diagram. | date | revision | authors | description||

| 2017-03-24 | v11V11 | John Hartfiel | Correction: Boot Mode Settingssettings. | ||||

| 2016-06-14 | V10v10 | Ali Naseri | initial Initial release. |

Disclaimer

| Include Page | ||||

|---|---|---|---|---|

|