...

| Scroll Title |

|---|

| anchor | Table_DRH |

|---|

| title | Design Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Vivado | Project Built | Authors | Description |

|---|

| 2019-04-18 | 2018.3 | TE0712-test_board_noprebuilt-vivado_2018.3-build_05_20190418082456.zip

TE0712-test_board-vivado_2018.3-build_05_20190418082240.zip | John Hartfiel | | | 2019-02-22 | 2018.3 | TE0712-test_board_noprebuilt-vivado_2018.3-build_01_20190222073819.zip

TE0712-test_board-vivado_2018.3-build_01_20190222073754.zip | John Hartfiel | - TE Script update

- linux changes

- SCU rework

- SI5338 CLKBuilder Pro Project

| | 2018-09-05 | 2018.2 | te0712-test_board-vivado_2018.2-build_03_20180906071356.zip

te0712-test_board_noprebuilt-vivado_2018.2-build_03_20180906071434.zip | John Hartfiel | - chance block design: qspi clks, clock wizard(REV01 only)

- change timing constrains

- add hello_te0712 application

- new SREC bootloader version

- change linux device tree

| | 2018-05-25 | 2017.4 | te0712-test_board-vivado_2017.4-build_10_20180525155402.zip

te0712-test_board_noprebuilt-vivado_2017.4-build_10_20180525155555.zip | John Hartfiel | - solved eth issue for REV01

- changed design + second design for REV01

| | 2018-04-12 | 2017.4 | te0712-test_board-vivado_2017.4-build_07_20180412081225.zip

te0712-test_board_noprebuilt-vivado_2017.4-build_07_20180412081253.zip | John Hartfiel | - bugfix constrain file - ETH REFCLK, timing

| | 2018-03-28 | 2017.4 | te0712-test_board-vivado_2017.4-build_07_20180328145151.zip

te0712-test_board_noprebuilt-vivado_2017.4-build_07_20180328145135.zip | John Hartfiel | | | 2018-01-08 | 2017.4 | te0712-test_board-vivado_2017.4-build_02_20180108155712.zip

te0712-test_board_noprebuilt-vivado_2017.4-build_02_20180108155735.zip | John Hartfiel | - no design changes

- small constrain changes

| | 2017-12-15 | 2017.2 | te0712-test_board-vivado_2017.2-build_07_20171215172447.zip

te0712-test_board_noprebuilt-vivado_2017.2-build_07_20171215172514.zip | John Hartfiel | - add SI5338 initialisation with MCS

- add Ethernet IP

| | 2017-11-07 | 2017.2 | te0712-test_board-vivado_2017.2-build_05_20171107172917.zip

te0712-test_board_noprebuilt-vivado_2017.2-build_05_20171107172939.zip | John Hartfiel | - add wiki link in Boart Part Files

- set correct short link for te0712-02-200-2c

| | 2017-10-05 | 2017.2 | te0712-test_board-vivado_2017.2-build_03_20171005082148.zip

te0712-test_board_noprebuilt-vivado_2017.2-build_03_20171005082225.zip | John Hartfiel | |

|

Release Notes and Know Issues

...

| Scroll Title |

|---|

| anchor | Table_KI |

|---|

| title | Known Issues |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Issues | Description | Workaround | To be fixed version |

|---|

| For PCB REV01 only: prebuilt does not boot | There is a Pullup missing on REV01 I2C SCL, so SI5338 configuration over MCS fails | Remove MCS | solved with 20180528 update | | For PCB REV01 only: CLK1B is not available on | additional clk is not connected on PCB | use other internal generated CLK, maybe more effort is needed to get ETH running | solved with 20180528 update | SREC SPI BootLoader default Offset | Default load offset is set to 0x400000 | Change manually on SDK to 0x5E0000 | solved with 20180412 update |

|

Requirements

Software

| Page properties |

|---|

|

Notes : - list of software which was used to generate the design

|

...

| Scroll Title |

|---|

| anchor | Table_HWC |

|---|

| title | Hardware Carrier |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Carrier Model | Notes |

|---|

| TE0701 |

| | TE0703 | used as reference carrier | | TE0705 |

| | TE0706 |

| | TEBA0841 |

|

|

Additional HW Requirements:

| Scroll Title |

|---|

| anchor | Table_AHW |

|---|

| title | Additional Hardware |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Additional Hardware | Notes |

|---|

| USB Cable for JTAG/UART | Check Carrier Board and Programmer for correct typ | | XMOD Programmer | Carrier Board dependent, only if carrier has no own FTDI |

|

Content

For general structure and of the reference design, see Project Delivery - Xilinx devices

Design Sources

| Scroll Title |

|---|

| anchor | Table_DS |

|---|

| title | Design sources |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Type | Location | Notes |

|---|

| Vivado | <design name>/block_design

<design name>/constraints

<design name>/ip_lib | Vivado Project will be generated by TE Scripts | | SDK/HSI | <design name>/sw_lib | Additional Software Template for SDK/HSI and apps_list.csv with settings for HSI | | PetaLinux | <design name>/os/petalinux | PetaLinux template with current configuration |

|

...

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:Vivado/SDK/SDSoCXilinx Development Tools

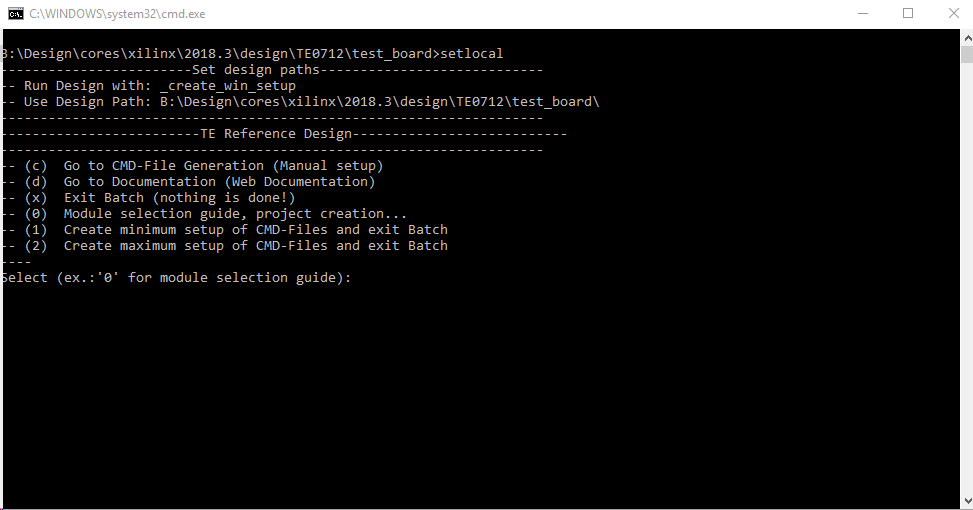

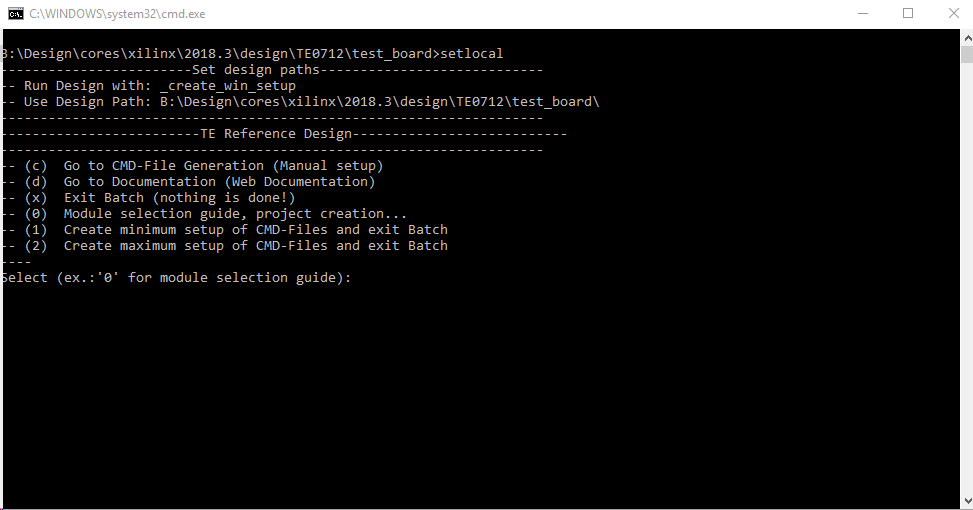

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Create Linux (uboot.elf and image.ub) with exported HDF

- HDF is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

Note: run init_config.sh before you start petalinux config. This will set correct temporary path variable.

Important Note: Select correct Flash partition offset on petalinux-config: Subsystem Auto HW Settings → Flash Settings, FPGA+Boot+bootenv=0x900000 (increase automatically generate Boot partition), increas image size to A:, see 54395771

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\default"

- (not longer needed manually: This will be done with Step 10.a automatically with newer scripts (2017.4.10) ) Generate UBoot SREC:

- Create SDK Project with TE Scripts on Vivado TCL: TE::sw_run_sdk

- Create "uboot-dummy" application

Note: Use Hello World Example - Copy u-boot.elf into "\workspace\sdk\uboot-dummy\Debug"

- Open "uboot-dummy" properties → C/C++ Build → Settings and go into Build Steps Tap.

- Add to Post-build steps: mb-objcopy -O srec u-boot.elf u-boot.srec

- Press Apply or regenerate project

Note: SREC is generated on "\workspace\sdk\uboot-dummy\Debug\u-boot.srec"

- Generate MCS Firmware (optional):

- Create SDK Project with TE Scripts on Vivado TCL: TE::sw_run_sdk

- Create "SCU" application

Note: Select MCS Microblaze and SCU Application - Select Release Built

- Regenerate App

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

- Copy "\prebuilt\software\<short name>\srec_spi_bootloader.elf" into "\firmware\microblaze_0\"

- (optional) Copy "\\workspace\sdk\scu\Release\scu.elf" into "\firmware\microblaze_mcs_0\"

- Regenerate Vivado Project or Update Bitfile only with "srec_spi_bootloader.elf" and "scu.elf"

...

| Scroll Title |

|---|

| anchor | Table_dch |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | 2*,*,3*,4* |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Document Revision | Authors | Description |

|---|

| Page info |

|---|

| modified-date |

|---|

| modified-date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

|

| | Page info |

|---|

| current-version |

|---|

| current-version |

|---|

| prefix | v. |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

|

| | | 2019-02-22 | v.31 | John Hartfiel | - 2018.3 release (include design reworks)

| |

Sept 2018 | v.30 | John Hartfiel | | 2018-05-25 | v.28 | John Hartfiel | | 2018-05-08 | v.27 | John Hartfiel | | 2018-04-12 | v.23 | John Hartfiel | | 2018-03-28 | v.22 | John Hartfiel | - Know Issue for PCB REV01 only

- Fix typo

- New assembly variant

| | 2018-02-13 | v.19 | John Hartfiel | | | 2018-01-08 | v.16 | John Hartfiel | | | 2017-12-15 | v.15 | John Hartfiel | - Update Design and Description

| | 2017-11-07 | v.11 | John Hartfiel | | | 2017-10-06 | v.10 | John Hartfiel | | | 2017-10-05 | v.8 | John Hartfiel | | | 2017-09-11 | v.1 | | | | --- | All | | Page info |

|---|

| modified-users |

|---|

| modified-users |

|---|

|

| --- |

|

Legal Notices

| Include Page |

|---|

| IN:Legal Notices |

|---|

| IN:Legal Notices |

|---|

|

...