Page History

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-06-19 | 2017.4 | TE0820-test_board-vivado_2017.4-build_10_20180619160713.zip TE0820-test_board_noprebuilt-vivado_2017.4-build_10_20180619160728.zip | John Hartfiel |

|

| 2018-05-24 | 2017.4 | TE0820-test_board-vivado_2017.4-build_10_20180524151356.zip | John Hartfiel |

|

| 2018-04-25 | 2017.4 | TE0820-test_board-vivado_2017.4-build_07_20180425134435.zip TE0820-test_board_noprebuilt-vivado_2017.4-build_07_20180425134459.zip | John Hartfiel |

|

| 2018-02-06 | 2017.4 | TE0820-test_board-vivado_2017.4-build_06_20180206203359.zip TE0820-test_board_noprebuilt-vivado_2017.4-build_06_20180206203414.zip | John Hartfiel |

|

| 2018-02-01 | 2017.4 | TE0820-test_board-vivado_2017.4-build_05_20180201084319.zip TE0820-test_board_noprebuilt-vivado_2017.4-build_05_20180201094724.zip | John Hartfiel |

|

| 2018-01-24 | 2017.4 | TE0820-test_board-vivado_2017.4-build_05_20180124085247.zip TE0820-test_board_noprebuilt-vivado_2017.4-build_05_20180124085303.zip | John Hartfiel |

|

| 2017-11-21 | 2017.2 | TE0820-test_board-vivado_2017.2-build_05_20171121160552.zip TE0820-test_board_noprebuilt-vivado_2017.2-build_05_20171121160606.zip | John Hartfiel |

|

| 2017-11-20 | 2017.2 | TE0820-test_board-vivado_2017.2-build_05_20171120162931.zip TE0820-test_board_noprebuilt-vivado_2017.2-build_05_20171120162851.zip | John Hartfiel |

|

| 2017-10-19 | 2017.2 | TE0820-test_board-vivado_2017.2-build_05_20171019104824.zip TE0820-test_board_noprebuilt-vivado_2017.2-build_05_20171019104837.zip | John Hartfiel |

|

...

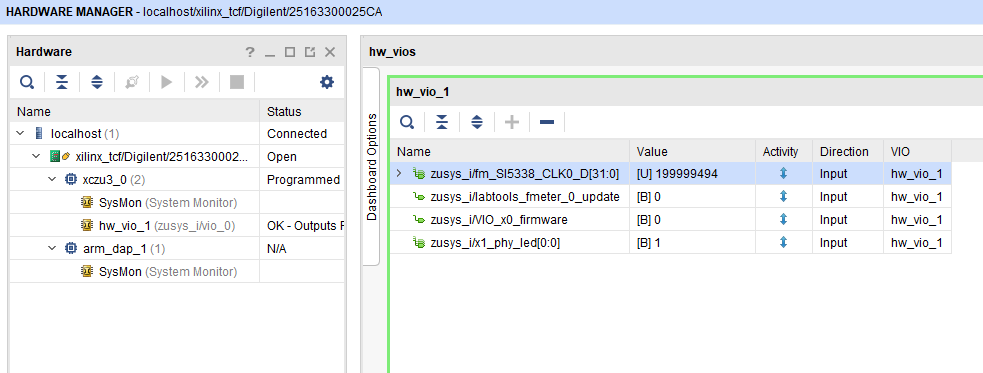

SI5338 CLK is configured to 200MHz by default.

PHY LEDS

CPLD Firmware:

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

...

Overview

Content Tools