Page History

...

Overview

| Scroll Only (inline) |

|---|

OnRefer to https://wiki.trenz-electronic.de/display/PD/TE0729+TRM thefor online version of this manual and additional othertechnical documentsdocumentation canof bethe foundproduct. |

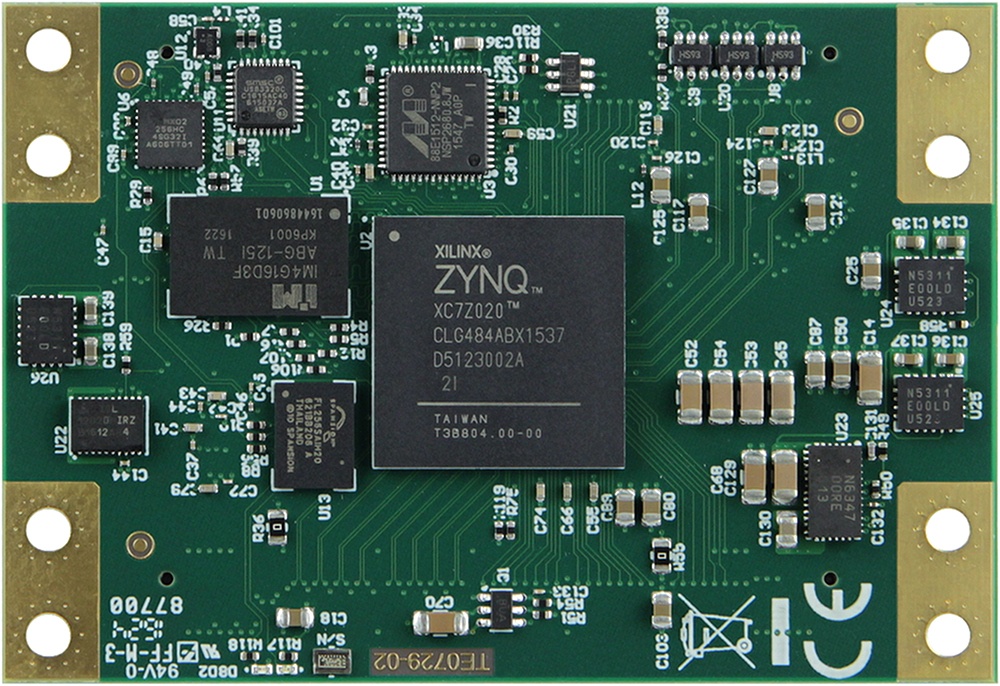

The Trenz Electronic TE0729 is an industrial-grade SoM (System on Module) based on Xilinx Zynq-7000 SoC (XC7Z020).

...

- Industrial-grade Xilinx Zynq-7000 (XC7Z020) SoM

- Dual-core ARM Cortex-A9 MPCore™ with CoreSight™

- 136 x FPGA I/Os (58 LVDS pairs possible)

- 8 x PS MIO pins

- 16-bit wide 512 MByte DDR3 SDRAM

- 32 MByte QSPI Flash memory

- 4 GByte eMMC Flash memory

- 1 x 10/100/1000 Mbps Ethernet transceiver PHY

- 2 x 10/100 Mbps Ethernet transceiver PHY'sPHYs

- 3 x MAC address EEPROM'sEEPROMs

- Hi-speed USB 2.0 ULPI transceiver with full OTG support

- Plug-on module with two 120-pin connectors

- Evenly - spread supply pins for good signal integrity

- On-board high-efficiency DC-DC converters

- 4.0 A x 1.0 V power rail

- 1.5 A x 1.5 V power rail

- 1.5 A x 1.8 V power rail

- 1.5 A x 2.5 V power rail

- System management

- eFUSE bit-stream encryption

- AES bit-stream bitstream encryption

- Temperature compensated RTC (real-time clock)

- User LED

- Rugged for shock and high vibration

...

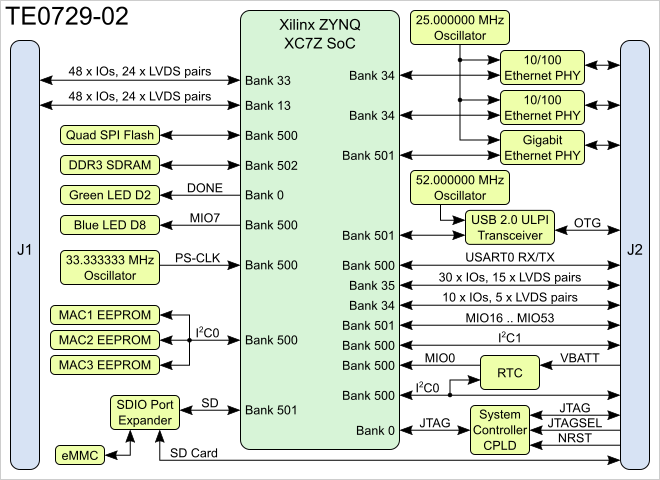

Block Diagram

Main Components

Initial Delivery State

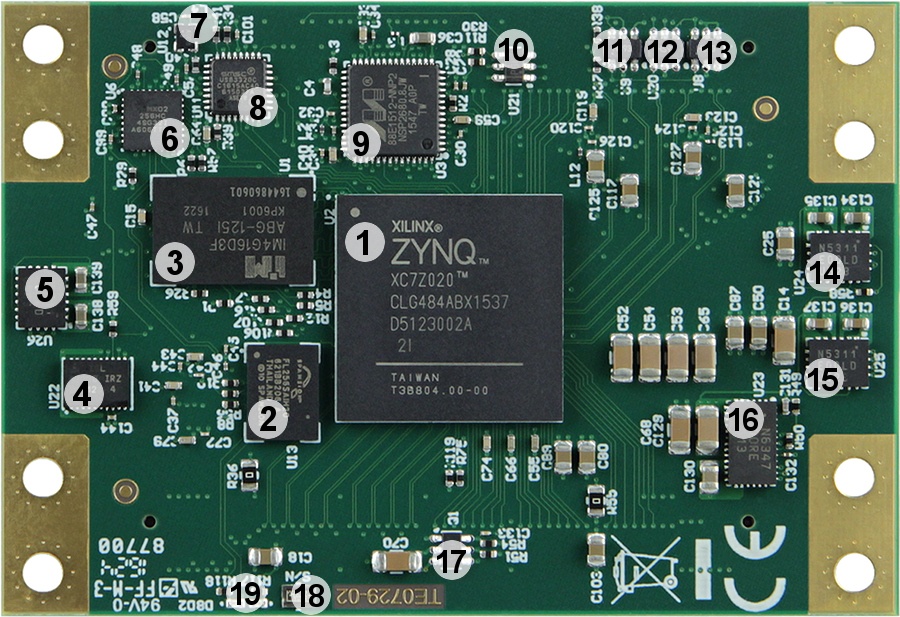

- Xilinx Zynq-7000 all programmable SoC, U2

- 32 MByte quad SPI Flash memory, U13

- 4 Gbit DDR3/L SDRAM, U1

- Low-power RTC with battery backed SRAM, U22

- 1A PowerSoC DC-DC converter (1.5V), U26

- System Controller CPLD, U6

- Low-power programmable oscillator @ 52.000000 MHz (OTG-RCLK), U12

- Hi-speed USB 2.0 ULPI transceiver, U11

- Gigabit Ethernet (GbE) transceiver, U3

- Ultra-low supply-current voltage monitor, U21

- 2K I2C serial EEPROM with EUI-48™ node identity, U9

- 2K I2C serial EEPROM with EUI-48™ node identity, U20

- 2K I2C serial EEPROM with EUI-48™ node identity, U8

- 1A PowerSoC DC-DC converter (2.5V), U24

- 1A PowerSoC DC-DC converter (1.8V), U25

- 4A PowerSoC DC-DC converter (1.0V), U23

- 3A PFET load switch with configurable slew rate (3.3V), Q1

- Serial number (traceability) pad

- Green LED D2 and red LED D8

- 10Base-T/100Base-TX Ethernet PHY, U19

- 10Base-T/100Base-TX Ethernet PHY, U17

- Low-power programmable oscillator @ 25.000000 MHz (ETH_CLKIN), U10

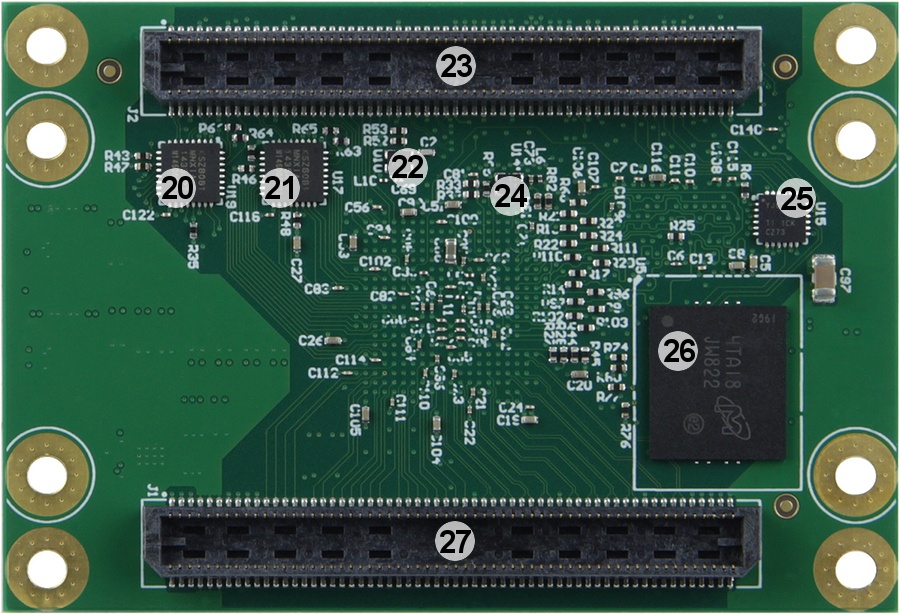

- 120-pin double-row REF-189019-02 B2B connector, J1

- Low-power programmable oscillator @ 33.333333 MHz (PS-CLK), U14

- SDIO port expander with voltage-level translation, U15

- eMMC NAND Flash, U5

- 120-pin double-row REF-189019-02 B2B connector, J2

Initial Delivery State

| Storage device name | Content | Notes |

|---|---|---|

24AA025E48 EEPROMs | ||

| Storage device name | Content | Notes |

24AA025E48 EEPROM's | User content not programmed | Valid MAC Address address from manufacturer |

| eMMC Flash-Memory | Empty, not programmed | Except serial number programmed by flash vendor |

SPI Flash OTP Area | Empty, not programmed | Except serial number programmed by flash vendor |

SPI Flash Quad Enable bit | Programmed | |

SPI Flash main array | demo Demo design | |

eFUSE USER | Not programmed | |

eFUSE Security | Not programmed |

...

JTAG access to the Xilinx Zynq-7000 device is provided through B2B connector J2.

| Signal | B2B Pin |

|---|---|

| TCK | J2-119 |

| TDI | J2-115 |

| TDO | J2-117 |

| TMS | J2-113 |

| Note |

|---|

JTAGSEL pin in 111 of B2B connector J2 should be kept low or grounded for normal operation. |

...

| Clock | Frequency | IC | FPGA | Notes | |

|---|---|---|---|---|---|

| PS-CLK | 33.3333 333333 MHz | U14 | PS_CLK | PS Subsystem subsystem main clock | |

| 10/100/1000 Mbps ETH PHY referenceETH_CLKIN | 25.000000 MHz | U10 | - | Ethernet PHYs reference clock | |

| USB PHY reference | 52.000000 MHz | U12 | - | USB PHY reference clock |

Default MIO mapping

| MIO | Configured as | B2B | Notes |

|---|---|---|---|

| 0 | GPIO | J2-87 | B2B |

| 1 | QSPI0 | - | SPI Flash-CS |

| 2 | QSPI0 | - | SPI Flash-DQ0 |

| 3 | QSPI0 | - | SPI Flash-DQ1 |

| 4 | QSPI0 | - | SPI Flash-DQ2 |

| 5 | QSPI0 | - | SPI Flash-DQ3 |

| 6 | QSPI0 | - | SPI Flash-SCK |

| 7 | GPIO | - | Red LED D8 |

| 8 | - | - | QSPI feedback clock |

| 9 | GPIO | J2-88 | B2B |

| 10 | I2C0 SDA | J2-90 | B2B |

| 11 | I2C0 SCL | J2-92 | B2B |

| 12 | I2C1 SDA | J2-93 | B2B (SDA on-board I2C, also configurable as GPIO by user) |

| 13 | I2C1 SCL | J2-95 | B2B (SCL on-board I2C, also configurable as GPIO by user) |

| 14 | USART0 RX | J2-94 | B2B (RX on-board UART, also configurable as GPIO by user) |

| 15 | USART0 TX | J2-96 | B2B (TX on-board UART, also configurable as GPIO by user) |

| 16..27 | ETH0 | Ethernet RGMII PHY | |

| 28..39 | USB0 | USB ULPI PHY | |

| 40 | SDIO0 | J2-100 | |

| 41 | SDIO0 | J2-102 | |

| 42 | SDIO0 | J2-104 | |

| 43 | SDIO0 | J2-106 | |

| 44 | SDIO0 | J2-108 | |

| 45 | SDIO0 | J2-110 | |

| 46 | GPIO | - | RTC Interrupt |

| 47 | - | - | - |

| 48 | GPIO | SEL_SD | SD Card multiplexer control |

| 49 | GPIO | - | USB Reset |

| 50 | GPIO | - | ETH0 Interrupt |

| 51 | GPIO | - | ETH0 Reset |

| 52 | ETH0 | - | MDC |

53 | ETH0 | - | MDIO |

...

| Peripheral | IC | Designator | PS | MIO | Notes |

|---|---|---|---|---|---|

| EEPROM I2C | 24AA025E48T-I/OT | U8 | I2C0 | MIO10, MIO11 | MAC Address |

| EEPROM I2C | 24AA025E48T-I/OT | U9 | I2C0 | MIO10, MIO11 | MAC Address |

| EEPROM I2C | 24AA025E48T-I/OT | U20 | I2C0 | MIO10, MIO11 | MAC Address |

| RTC | ISL12020MIRZ | U22 | I2C0 | MIO10, MIO11 | Temperature compensated real time clock |

| RTC Interrupt | ISL12020MIRZ | U22 | GPIO | MIO46 | Real Time Clock Interrupt |

| SPI Flash | S25FL256SAGBHI20 | U13 | QSPI0 | MIO1..MIO6 | |

| Ethernet0 10/100/1000 Mbps PHY | 88E1512-A0-NNP2I000 | U3 | ETH0 | MIO16...MIO27 | |

| Ethernet0 10/100/1000 Mbps PHY Reset | GPIO | MIO51 | |||

| Ethernet1 10/100 Mbps PHY | KSZ8081MLXCA | U17 | - | (EMIO) | |

| Ethernet1 10/100 Mbps PHY Reset | - | (EMIO) | |||

| Ethernet2 10/100 Mbps PHY | KSZ8081MLXCA | U19 | - | (EMIO) | |

| Ethernet2 10/100 Mbps PHY Reset | - | (EMIO) | |||

| USB | USB3320C-EZK | U11 | USB0 | MIO28...MIO39 | |

| USB Reset | GPIO | MIO49 | |||

| eMMC eMMC (embedded eMMC) | MTFC4GMVEA-4M IT | U5 | SDIO0 | MIO40...MIO45 |

...

Ethernet1 PHY connection to B2B-connectors:

| PHY PIN | B2B | notesNotes |

|---|---|---|

| ETH1_RX_P | J2-26 | - |

| ETH1_RX_N | J2-28 | - |

| ETH1_TX_P | J2-20 | - |

| ETH1_TX_N | J2-22 | - |

| ETH1_LED0 | J2-34 | Status LED |

| ETH1_LED1 | J2-32 | Transmission LED |

Ethernet2 PHY connection to B2B-connectors:

| PHY PIN | B2B | notesNotes |

|---|---|---|

| ETH2_RX_P | J2-2 | - |

| ETH2_RX_N | J2-4 | - |

| ETH2_TX_P | J2-8 | - |

| ETH2_TX_N | J2-10 | - |

| ETH2_LED0 | J2-16 | Status LED |

| ETH2_LED1 | J2-14 | Transmission LED |

All other pins of the PHYs are connected to Bank34 of Zynq, see schematic for further details.

USB Interface

The USB PHY Microchip USB3320 from Microchip is used on the TE0729. The is connected via ULPI interface is connected to the Zynq PS USB0. The I/O Voltage voltage level is fixed at 1.8V .The and PHY reference clock input of the PHY is supplied from an the on-board 52MHz 52.000000 MHz oscillator (U12).

PHY connection:

| PHY Pin | Zynq Pin | B2B Name | Notes |

|---|---|---|---|

| ULPI | MIO28..39 | - | Zynq USB0 MIO pins are connected to the PHY |

| REFCLK | - | - | 52MHz from on board oscillator (U12) |

| REFSEL[0..2] | - | - | 000 All three connected to the GND, select 52MHz reference Clockselects 52.000000 MHz as reference clock |

| RESETB | MIO49 | - | Active-low reset |

| CLKOUT | MIO36 | - | Connected to 1.8V, selects reference clock operation mode |

| DP,DM | - | OTG_D_P, OTG_D_N | USB Data data lines |

| CPEN | - | VBUS_V_EN | External USB power switch active-high enable signal |

| VBUS | - | USB_VBUS | Connect Connected to the USB-VBUS via a series resistor. Check reference schematic |

| ID | - | OTG_ID | For an A-Device connect connected to the ground, for a B-Device left floating |

...

Battery backed registers are accessed at I2C slave address 0x57. General purpose RAM is accessed at I2C slave address 0x6F. This RTC IC is supported in by the Linux OS, so it can be used as hwclock device.

MAC-Address

...

EEPROMs

TE0729 module has three Microchip 24AA025E48 EEPROMs

...

Three Microchip 24AA025E48 EEPROM's (U8, U9 , and U20) are used on the TE0729. They which contain globally unique 48-bit node addresses, that are compatible with EUI-48(TM) and EUI-64(TM). The devices compatible 48-bit node (MAC) addresses. These EEPROMs are organized as two blocks of 128 x 8-bit memory. One of those the blocks stores the 48-bit node address and is write protected, the other block is available for application use. It is accessible through the I2C EEPROMs are accessible using I2C slave address 0x50 for MAC-Address1 (U8), 0x51 for MAC-Address2 (U9), 0x52 for MAC-Address3 (U20).

...

TE0729 has support for hardware watchdog function. With standard variant, By default the watchdog is disabled at power up. Please contact Trenz Electronic for details how to enable watchdog function.

...

| Parameter | Min | Max | Units | Notes |

|---|---|---|---|---|

Vin VIN supply voltage | -0.1 | 3.75 | V | |

| VBAT supply voltage | -0.3 | 6.0 | V | |

| PL IO Bank I/O bank supply voltage for HR I/O banks (VCCO) | -0.5 | 3.6 | V | |

| I/O input voltage for HP HR I/O banks | -0.55 | VCCO_X+0.55 | V | TE0729 does not have HP banks |

Voltage on Module module JTAG pins | -0.4 | VCCO_0+0.55 | V | VCCO_0 is 3.3V nominal |

Storage Temperaturetemperature | -40 | +85 | C | |

| Storage Temperature temperature without the ISL12020MIRZ | -55 | +100 | C |

...

| Parameter | Min | Max | Units | Notes | Reference document |

|---|---|---|---|---|---|

| Vin VIN supply voltage | 2.5 | 3.6 | V | ||

| VBAT supply voltage | 1.8 | 5.5 | V | ||

| PL IO Bank I/O bank supply voltage for HR I/O banks (VCCO) | 1.14 | 3.465 | V | Xilinx document DS191 | |

| I/O input voltage for HR I/O banks | (*) | (*) | V | (*) Check datasheet | Xilinx document DS191 and DS187 |

| Voltage on module JTAG pins | 3.135 | 3.465 | V | VCCO_0 is 3.3 V nominal |

...

| Date | Revision | Contributors | Description |

|---|---|---|---|

| 2017-06-18 | Jan Kumann | New product images. | |

| 2017-06-07 | V.21 | Jan Kumann | Minor re-formatting. |

2017-05-22 | V.12 | Jan Kumann | Sections rearranged for common style. New physical dimension images. Hardware revision image added. New block diagram. |

| 2017-03-24 | V.11 | John Hartfiel | Correction: Boot Mode settings. |

| 2016-06-14 | V.10 | Ali Naseri | Initial release. |

...