Page History

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2017.4 | John Hartfiel |

| ||

| 2017-12-15 | 2017.2 | te0712-test_board-vivado_2017.2-build_07_20171215172447.zip te0712-test_board_noprebuilt-vivado_2017.2-build_07_20171215172514.zip | John Hartfiel |

|

| 2017-11-07 | 2017.2 | te0712-test_board-vivado_2017.2-build_05_20171107172917.zip te0712-test_board_noprebuilt-vivado_2017.2-build_05_20171107172939.zip | John Hartfiel |

|

| 2017-10-05 | 2017.2 | te0712-test_board-vivado_2017.2-build_03_20171005082148.zip te0712-test_board_noprebuilt-vivado_2017.2-build_03_20171005082225.zip | John Hartfiel |

|

...

| Issues | Description | Workaround | To be fixed version | |||

|---|---|---|---|---|---|---|

| Timing fails for fmeter IP | Timing ignore constrains does not work for some signals. | This can be ignored | No known issues | --- | --- | --- |

Requirements

Software

| HTML |

|---|

<!-- Add needed external Software --> |

...

| Software | Version | Note |

|---|---|---|

| Vivado | 2017.24 | needed |

| SDK | 2017.24 | needed |

| PetaLinux | 2017.24 | needed |

Hardware

| HTML |

|---|

<!-- Hardware Support --> |

...

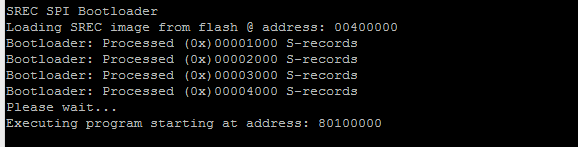

Boot process takes a while, please wait.

Linux

Note: Linux boot process is slower on Microblaze.

- Open Serial Console (e.g. putty)

- Speed: 9600

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:- User Name: root

- Password: root

- You can use Linux shell now.

- ETH0 works with udhcpc

- ETH0 works with udhcpc

...

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

#I2C set_property PACKAGE_PIN W21 [get_ports pllPLL_i2cI2C_scl_io] set_property IOSTANDARD LVCMOS33 [get_ports pllPLL_i2cI2C_scl_io] set_property PACKAGE_PIN T20 [get_ports pllPLL_i2cI2C_sda_io] set_property IOSTANDARD LVCMOS33 [get_ports pllPLL_i2cI2C_sda_io] #Reset set_property PACKAGE_PIN T3 [get_ports reset] set_property IOSTANDARD LVCMOS15 [get_ports reset] #CLKS set_property PACKAGE_PIN R4 [get_ports {CLK1B[0]}] set_property IOSTANDARD SSTL15 [get_ports {CLK1B[0]}] set_property PACKAGE_PIN K4 [get_ports {CLK0_clk_p[0]}] set_property IOSTANDARD DIFF_SSTL15 [get_ports {CLK0_clk_p[0]}] #ETH PHY set_property PACKAGE_PIN N17 [get_ports phy_rst_n] set_property IOSTANDARD LVCMOS33 [get_ports phy_rst_n] |

...

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

create_clock -period 8.000 -name mgt_clk0_clk_p -waveform {0.000 4.000} [get_ports mgt_clk0_clk_p]

create_clock -period 10.000 -name {CLK0_clk_p[0]} -waveform {0.000 5.000} [get_ports {CLK0_clk_p[0]}]

create_clock -period 20.000 -name {CLK1B[0]} -waveform {0.000 10.000} [get_ports {CLK1B[0]}]

create_clock -period 15.152 -name msys_i/axi_quad_spi_0/U0/NO_DUAL_QUAD_MODE.QSPI_NORMAL/QSPI_LEGACY_MD_GEN.QSPI_CORE_INTERFACE_I/LOGIC_FOR_MD_12_GEN.SCK_MISO_STARTUP_USED.QSPI_STARTUP_BLOCK_I/cfgmclk -waveform {0.000 7.576} [get_pins msys_i/axi_quad_spi_0/U0/NO_DUAL_QUAD_MODE.QSPI_NORMAL/QSPI_LEGACY_MD_GEN.QSPI_CORE_INTERFACE_I/LOGIC_FOR_MD_12_GEN.SCK_MISO_STARTUP_USED.QSPI_STARTUP_BLOCK_I/STARTUP_7SERIES_GEN.STARTUP2_7SERIES_inst/CFGMCLK]

set_false_path -from [get_clocks {CLK0_clk_p[0]}] -to [get_clocks clk_pll_i]

set_false_path -from [get_clocks mgt_clk0_clk_p] -to [get_clocks clk_pll_i]

set_false_path -from [get_clocks msys_i/axi_quad_spi_0/U0/NO_DUAL_QUAD_MODE.QSPI_NORMAL/QSPI_LEGACY_MD_GEN.QSPI_CORE_INTERFACE_I/LOGIC_FOR_MD_12_GEN.SCK_MISO_STARTUP_USED.QSPI_STARTUP_BLOCK_I/cfgmclk] -to [get_clocks clk_pll_i]

set_false_path -from [get_clocks -of_objects [get_pins msys_i/mig_7series_0/u_msys_mig_7series_0_0_mig/u_ddr3_infrastructure/gen_ui_extra_clocks.mmcm_i/CLKFBOUT]] -to [get_clocks mgt_clk0_clk_p]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/COUNTER_REFCLK_inst/bl.DSP48E_2/CLK] -to [get_pins {msys_i/vio_0/inst/PROBE_IN_INST/probe_in_reg_reg[*]/D}]

set_false_path -from [get_pins {msys_i/labtools_fmeter_0/U0/F_reg[*]/C}] -to [get_pins {msys_i/vio_0/inst/PROBE_IN_INST/probe_in_reg_reg[*]/D}]

set_false_path -from [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CLK}] -to [get_pins {msys_i/labtools_fmeter_0/U0/F_reg[*]/D}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CECARRYIN}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CEP}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CEA2}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CEB2}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CEALUMODE}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CECTRL}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CEC}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg_replica/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTC}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg_replica/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTB}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg_replica/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTA}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg_replica/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTP}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg_replica/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTINMODE}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg_replica/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTALUMODE}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg_replica/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTCTRL}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg_replica/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTALLCARRYIN}] |

Software Design - SDK/Software Design - SDK/HSI

| HTML |

|---|

<!-- optional chapter separate sections for different apps --> |

...

Template location: \sw_lib\sw_apps\srec_spi_bootloader

xilisf_v5_

...

9

Changed default Flash Typ to 5.

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| 2018-01-08 | v.16 | John Hartfiel |

| sourc

| |||||||||||||||||||||

| 2017-12-15 | v.15 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-11-07 | v.11 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-06 | v.10 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-05 | v.8 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-09-11 | v.1 |

|

| ||||||||||||||||||||||

| All |

|

...

Overview

Content Tools