Page History

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-06-0522 | 2017.4 | TE0841-IBERT_noprebuilt-vivado_2017.4-build_1011_2018060514385220180622140813.zip TE0841-IBERT-vivado_2017.4-build_1011_2018060514383720180622140615.zip | John Hartfiel |

|

Release Notes and Know Issues

| ||||

| 2018-06-05 | 2017.4 | TE0841-IBERT_noprebuilt-vivado_2017.4-build_10_20180605143852.zip TE0841-IBERT-vivado_2017.4-build_10_20180605143837.zip | John Hartfiel |

|

Release Notes and Know Issues

| HTML |

|---|

<!--

- add known Design issues and |

| HTML |

<!--

- add known Design issues and general Notes for the current revision

--> |

...

Complete List is available on <design name>/board_files/*_board_files.csv

Design supports following modules:

Design supports following modules:

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | Others | Notes | |

|---|---|---|---|---|---|---|---|

| TE0841-01-035-1C | 01_35_1c | REV01 | 2x 512MB DDR4 | 32MB | --- | ||

| TE0841-01-035-1I | 01_35_1i | REV01 | 2x 512MB DDR4 | 32MB | --- | ||

| TE0841-01-035-2I | 01_35_2i | REV01 | 2x 512MB DDR4 | 32MB | --- | ||

| TE0841-01-040-1C | 01_40_1c | REV01 | 2x 512MB DDR4 | 32MB | --- | ||

| TE0841-01-040-1I | 01_40_1i | REV01 | 2x 512MB DDR4 | 32MB | --- | ||

| TE0841-01-040-2I | 01_40_2i | REV01 | 2x 512MB DDR4 | 32MB | --- | ||

| TE0841-02-035-1C | 02_35_1c | REV02 | 2x 1GB DDR4 | 64MB | |||

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | Others | Notes | |

| TE0841-01-035-1C | 01_35_1c | REV01 | 2x 512MB DDR4 | 32MB | --- | ||

| TE0841-0102-035-1I | 0102_35_1i | REV01REV02 | 2x 512MB 1GB DDR4 | 32MB64MB | --- | ||

| TE0841-0102-035-2I | 0102_35_2i | REV01REV02 | 2x 512MB 1GB DDR4 | 32MB64MB | --- | ||

| TE0841-0102-040-1C | 0102_40_1c | REV01REV02 | 2x 512MB 1GB DDR4 | 32MB64MB | --- | ||

| TE0841-0102-040-1I | 0102_40_1i | REV01REV02 | 2x 512MB 1GB DDR4 | 32MB64MB | --- | ||

| TE0841-0102-040-2I1IL | 0102_40_2i1i | REV01REV02 | 2x 512MB 1GB DDR4 | 32MB | 64MB | low profile B2B connector--- |

Design supports following carriers:

...

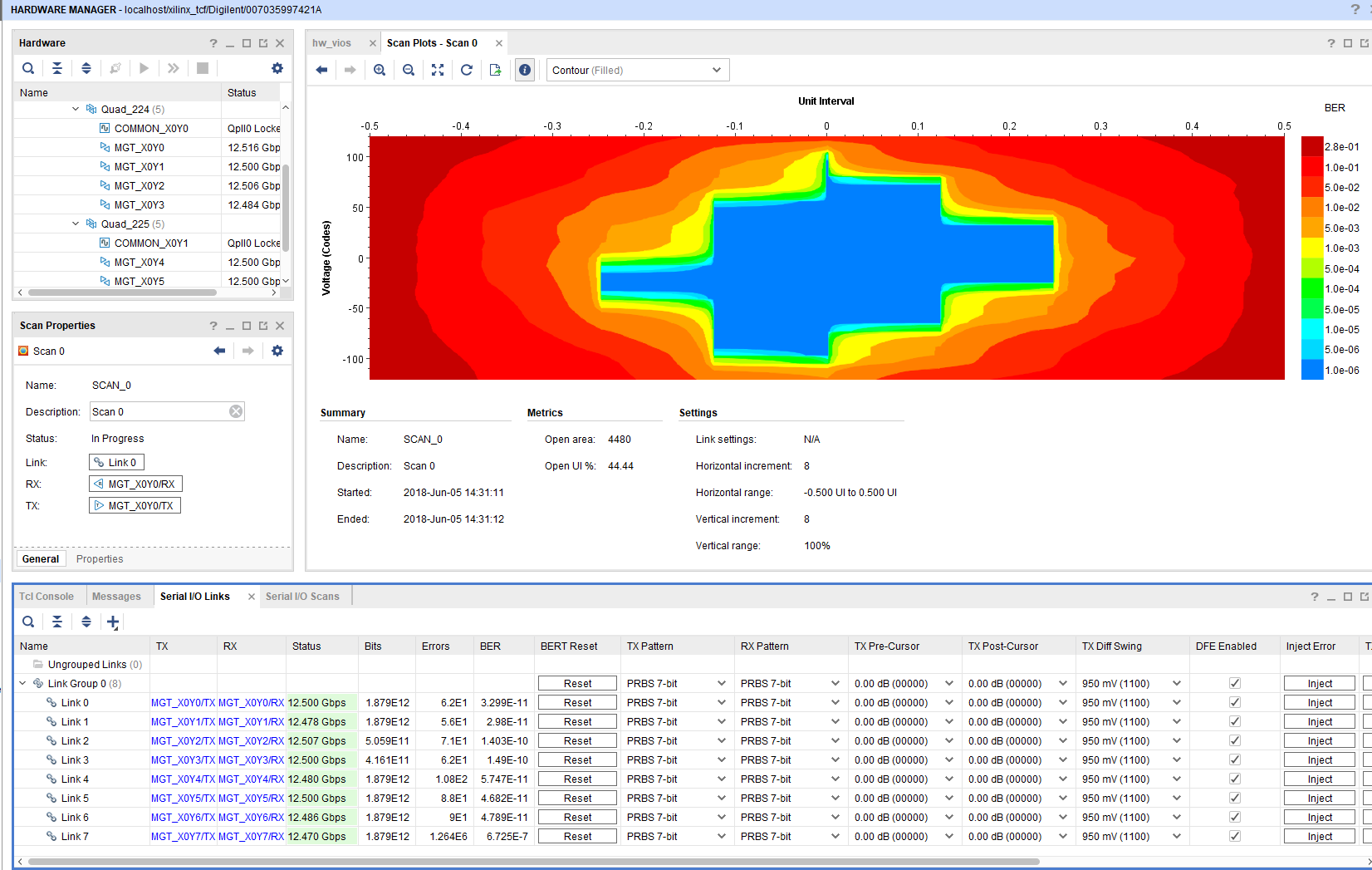

- Open Vivado HW-Manager

- "Refresh device" is needed after Bitfile programming, because MCS reconfigure SI5338 and enables IBERT a little bit later.

- loopback depends on TEB0841 Revision an connection

| IBERT | Component Name | Net Name | TEB0841 |

|---|---|---|---|

| X0Y0 | 224-0 | MGT4 | loop back RX/TX |

| X0Y1 | 224-1 | MGT5 | loop back RX/TX |

| X0Y2 | 224-2 | MGT6 | loopback over SD Pin header possible with lower Linerate otherwise use internal loopback |

| X0Y3 | 224-3 | MGT7 | loop back RX/TX. Note: N.C. on TEB0841-01, use internal loopback |

| X0Y4 | 225-0 | MGT0 | loop back RX/TX |

| X0Y5 | 225-1 | MGT1 | loop back RX/TX |

| X0Y6 | 225-2 | MGT2 | loop back RX/TX |

| X0Y7 | 225-3 | MGT3 | loopback over sfp possible |

...

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

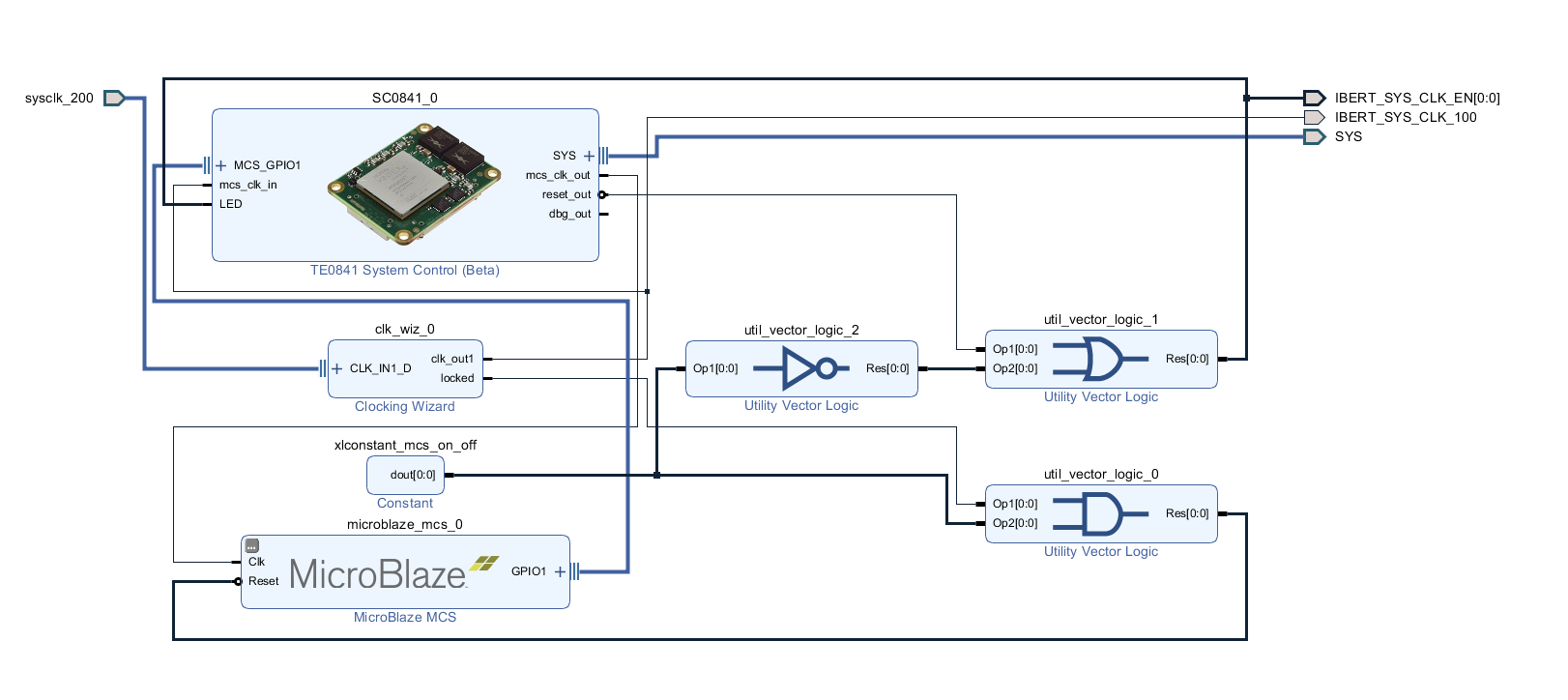

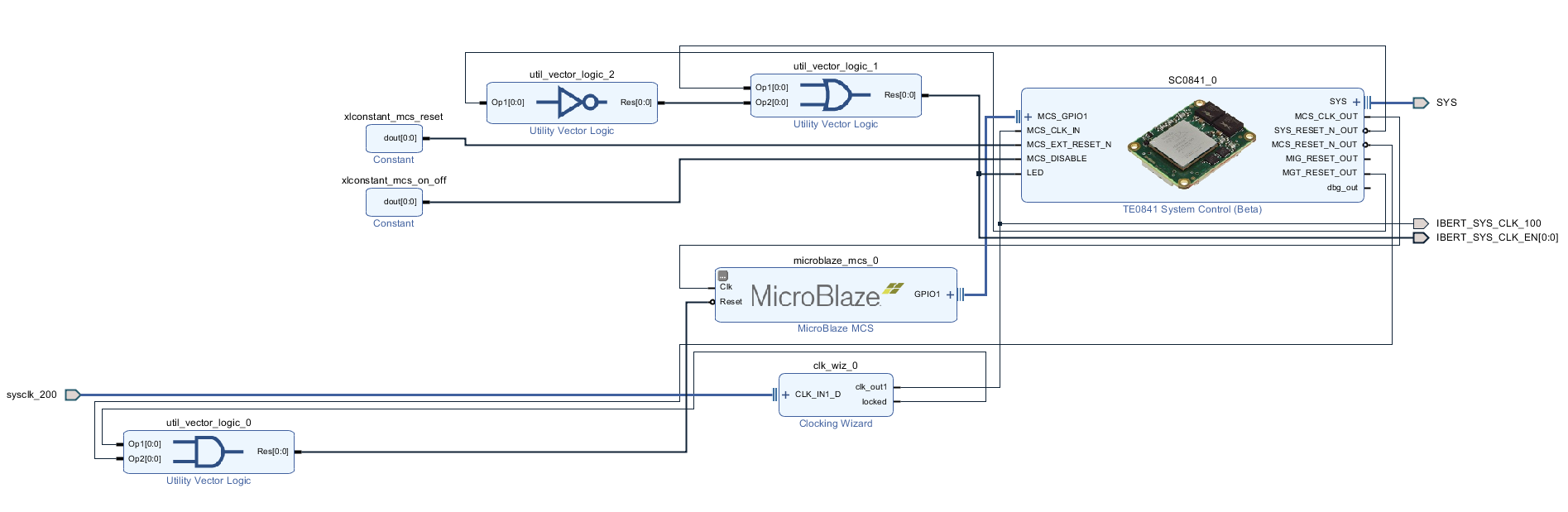

Block Design

HDL

- IBERT_top.v

- ibert xci IPs

...

| Code Block | ||||||

|---|---|---|---|---|---|---|

| ||||||

# file: ibert_ultrascale_gth_0.xdc #################################################################################### ## ____ ____ ## / /\/ / ## /___/ \ / Vendor: Xilinx ## \ \ \/ Version : 2012.3 ## \ \ Application : IBERT Ultrascale ## / / Filename : example_ibert_ultrascale_gth_0.xdc ## /___/ /\ ## \ \ / \ ## \___\/\___\ ## ## ## ## Generated by Xilinx IBERT 7Series ##************************************************************************** ## ## Icon Constraints ## create_clock -name D_CLK -period 10.0 [get_ports gth_sysclkp_i] set_clock_groups -group [get_clocks D_CLK -include_generated_clocks] -asynchronous set_property C_CLK_INPUT_FREQ_HZ 100000000 [get_debug_cores dbg_hub] set_property C_ENABLE_CLK_DIVIDER true [get_debug_cores dbg_hub] ##gth_refclk lock constraints ## set_property PACKAGE_PIN AD6 [get_ports gth_refclk0p_i[0]] set_property PACKAGE_PIN AD5 [get_ports gth_refclk0n_i[0]] set_property PACKAGE_PIN AB6 [get_ports gth_refclk1p_i[0]] set_property PACKAGE_PIN AB5 [get_ports gth_refclk1n_i[0]] ## ## Refclk constraints ## create_clock -name gth_refclk0_0 -period 8.0 [get_ports gth_refclk0p_i[0]] create_clock -name gth_refclk1_0 -period 8.0 [get_ports gth_refclk1p_i[0]] set_clock_groups -group [get_clocks gth_refclk0_0 -include_generated_clocks] -asynchronous set_clock_groups -group [get_clocks gth_refclk1_0 -include_generated_clocks] -asynchronous ## ## System clock pin locs and timing constraints ## set#set_property PACKAGE_PIN R25 [get_ports gth_sysclkp_i] set#set_property IOSTANDARD LVDS [get_ports gth_sysclkp_i] |

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| v.4 | John Hartfiel |

| |||||||||||||||||||||||

| 2018-04-16 | v.1 |

|

| ||||||||||||||||||||||

| All |

|

...

Overview

Content Tools