...

Intel® MAX 10 Commercial [10M08SAU169C8G]

SDRAM Memory up to 64Mb, 166MHzDual High Speed USB to 32 Mbyte (8Mbyte default)

USB 2.0 Multipurpose UART/FIFO IC

64 Mb Quad SPI Flash

4Kb EEPROM Memory

8x User LED

(FT2232H)

- 4 Kbit EEPROM Memory for FTDI configuration data

- Micro USB Receptacle (communication and power)

SPI Flash - NOT INSTALLED (only special option)

- 8x User LED Micro USB2 Receptacle 90

- 18 Bit 2MSPS Analog to Digital Converter

2x SMA Female Connector

I/O interface: 23x GPIO - Arduino MKR compatible

Power Supply: 5V

Dimension: 86.5mm x 25mm

Others:

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

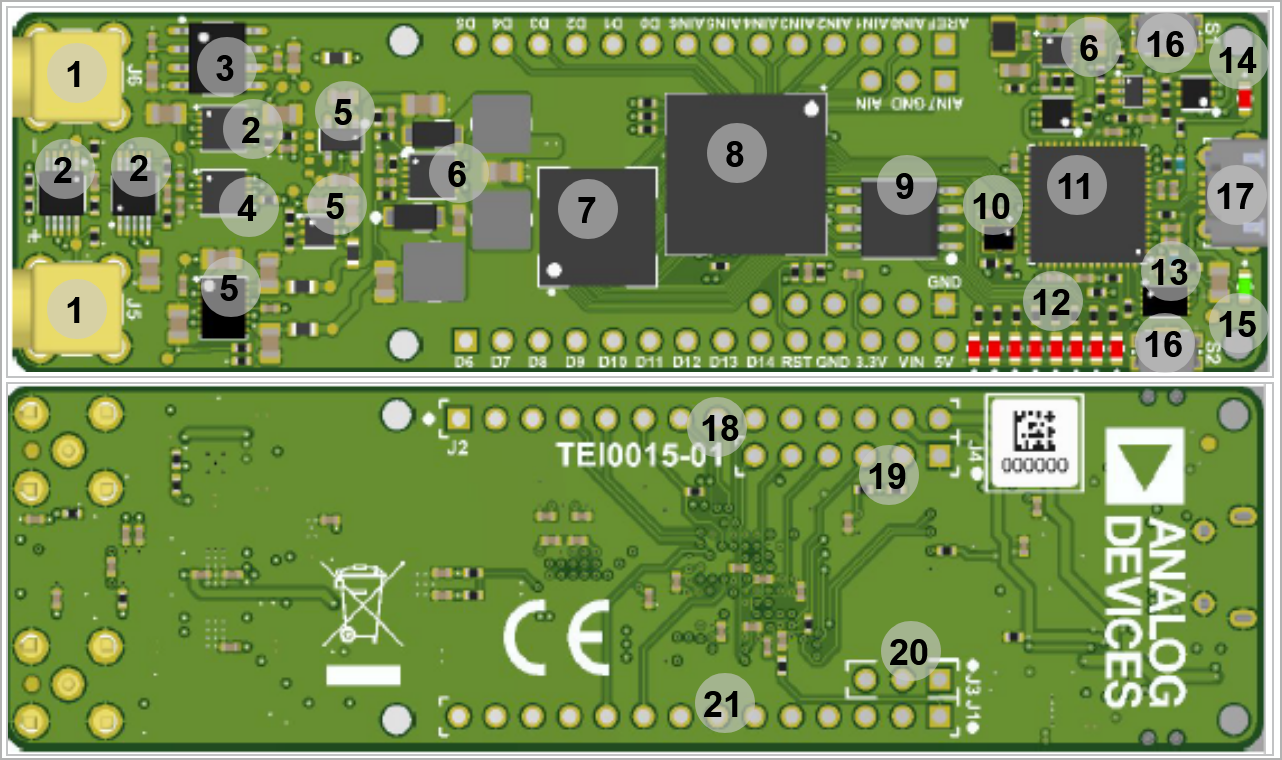

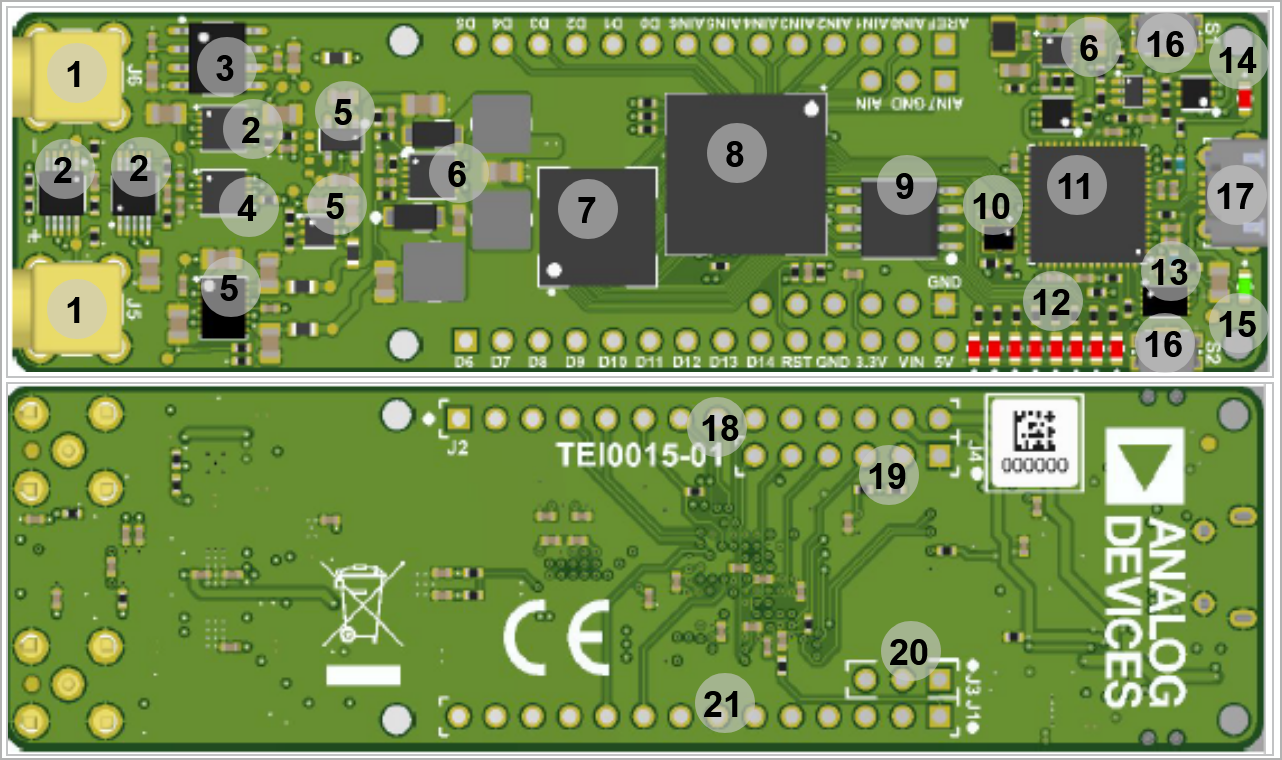

| title | TEI0015 main components |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramName | TEI0015_OV_MC |

|---|

| simpleViewer | false |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 1314 |

|---|

|

|

| Scroll Only |

|---|

|

|

SMA Connector, J5...6

Amplifier, U12 - U14 - U6

Series Voltage Reference, U8

Analog to Digital Converter, U15

Voltage Regulator, U10 - U13 - U16

Switching Voltage Regulator/LDO, U11 - U4

SDRAM Memory, U2

- Intel® MAX 10 FPGA, U1

SPI Flash Memory, U5

12.00 MHz MEMS oscillator, U7

FTDI USB2 to JTAG/UART adapter, U3

User LEDs, D2...9

FTDI configuration EEPROM, U9

Configuration/Status LED (Red) , D10

Power-on LED (Green), D1

Push button, S1...2

Micro USB Connector, J9

1x14 pin header, J2 (Not assembled)

1x6 pin header, J4 (Not assembled)

1x4 Header, J3 (Not assembled)

1x14 pin header, J1 (Not assembled)

...

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Storage device name | Content | Notes |

|---|

Quad SPI Flash | N/A | Not Programmedpopulated | | EEPROM | Programmed | FTDI configuration | SDRAM | Not Programmed |

|

Configuration Signals

Configuration Signals

| Page propertiesdetails |

|---|

|

- Overview of Boot Mode, Reset, Enables.

|

The FPGA configuration for Intel MAX 10 FPGAs can be stored through JTAG interface either in external configuration device (QSPI flash memory U5) or (using a *.POF file) on the FPGA itself since the Intel MAX 10 FPGA offers non-volatile configuration memory on chip. The FPGA configuration is loaded from the non-volatile memory when the board is powered up. To configure the FPGA directly, the JTAG interface can be used to configure the FPGA volatile (using a *.SOF file), means the configuration is lost after power off.

Reset process must be done FPGA Reconfigration can be triggered by pressing push button S1.

...

| Scroll Title |

|---|

| anchor | Table_OBP_IOs |

|---|

| title | FPGA I/O Banks |

|---|

|

| FPGA Bank | I/O Signal Count | Connected to | Notes |

|---|

| Bank 1A | 7 | 1x14 Pin header, J1 | AIN0...6 | | 1 | Jumper, J3 | AIN7 | | Bank 1B | 5 | 1x6 Pin header, J4 | JTAG_EN, TDI, TDO, TMS, TCK | Bank 2

| 4 | 1x14 Pin header, J1 | D2...5 | | 5 | A2D, U15 | ADC_EN, ADC_SDI, ADC_SDO, ADC_SCK, ADC_CNV | | 1 | 12MHz Oscillator, U7 | CLK12M | | 2 | Amplifier, U12 | nIAMP_A0, nIAMP_A1 | | Bank 3 | 22 | SDRAM, U2 | RAM_ADDR_CMD | | Bank 5 | 9 | 1x14 Pin header, J2 | DIO6...14 | | 2 | 1x14 Pin header, J1 | DIO0...1 | | 1 | D12_R | DIO12 | | Bank 6 | 16 | SDRAM, U2 | DQ0...15 | | 2 | SDRAM, U2 | DQM0...1 | | 1 | D11_R | DIO11 | Bank 8

| 8 | User Red LEDs, D2...9 | LED0...7 | | 6 | SPI Flash, U5 | F_CS, F_CKL, F_DI, F_DO, nSTATUS, DEVCLRn | | 1 | Red LED, D10 | CONF_DONE | | 6 | FTDI JTAG/UART Adapter, U3 | BDBUS0...5 | | 1 | Push Button, S2 | USER_BTN |

|

Micro-

...

USB Connector

The Micro-USB2 USB connector J9 provides an interface to access the FIFO/UART and JTAG functions via FTDI FT2232 chip. The use of this feature requires that FTDI USB driver is drivers are installed on your host PC.

...

JTAG access to the TEI0015 SoM through pin header connector J4. This is normally not needed as there is on-board USB JTAG functionality.

| Scroll Title |

|---|

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

JTAG Signal | Pin Header Connector | Note |

|---|

| TMS | J4-6 |

| | TDI | J4-5 |

| | TDO | J4-4 |

| | TCK | J4-3 |

| | JTAG_EN | J4-2 | Pulled-up to 3.3V |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP |

|---|

| title | On board peripherals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

SDRAM

TEI0015 is equipped with a Winbond 64 MBit (8 MByte) SDRAM chip in standard configuration, variants with 256 Mbit (32 MByte) memory density are also available. The SDRAM chip is connected to the FPGA bank 3 and 6 via 16-bit memory interface with 166MHz clock frequency and CL3 CAS latency.

...

| Scroll Title |

|---|

| anchor | Table_OBP_SDRAM |

|---|

| title | SDRAM interface IOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| SDRAM I/O Signals | Signal Schematic Name | Connected to | Notes |

|---|

| Address inputs | A0 ... A13 | bank 3 | - | | Bank address inputs | BA0 / BA1 | bank 3 | - | | Data input/output | DQ0 ... DQ15 | bank 6 | - | | Data mask | DQM0 ... DQM1 | bank 6 | - | | Clock | CLK | bank 3 | - | | Control Signals | CS | bank 3 | Chip select | CKE | bank 3 | Clock enable | RAS | bank 3 | Row Address Strobe | CAS | bank 3 | Column Address Strobe | | WE | bank 3 | Write Enable |

|

FTDI FT2232H

The FTDI chip U3 converts signals from USB2 to a variety of standard serial and parallel interfaces. Refer to the FTDI data sheet to get information about the capacity features of the FT2232H chip. FTDI FT2232H chip channel A is used in MPPSE mode for JTAG, 6 I/O's of . Channel B are routed to FPGA bank 8 of the FPGA SoC and are usable for example as GPIOs, UART or other standard interfacesis configured to be used in async FIFO mode, this is default mode when using preprogrammed FTDI configuration. In this mode the communication from host PC looks like normal UART but from the FTDI side it is 8 bit FIFO style interface.

The configuration of FTDI FT2232H chip is pre-programmed on in the EEPROM U9.

| Scroll Title |

|---|

| anchor | Table_OBP_FTDI |

|---|

| title | FTDI chip interfaces and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FTDI Chip U3 Pin | Signal Schematic Name | Connected to | Notes |

|---|

| ADBUS0 | TCK | FPGA bank 1B, pin G2 | JTAG interface | | ADBUS1 | TDI | FPGA bank 1B, pin F5 | | ADBUS2 | TDO | FPGA bank 1B, pin F6 | | ADBUS3 | TMS | FPGA bank 1B, pin G1 | | BDBUS0 | BDBUS0 | FPGA bank 8, pin A4 | User configurable | | BDBUS1 | BDBUS1 | FPGA bank 8, pin B4 | User configurable | | BDBUS2 | BDBUS2 | FPGA bank 8, pin B5 | User configurable | | BDBUS3 | BDBUS3 | FPGA bank 8, pin A6 | User configurable | | BDBUS4 | BDBUS4 | FPGA bank 8, pin B6 | User configurable | | BDBUS5 | BDBUS5 | FPGA bank 8, pin A7 | User configurable |

|

SPI Flash

| BDBUS6 | BDBUS6 | FPGA bank 6, pin C11 |

| | BDBUS7 | BDBUS7 | FPGA bank 3, pin J7 |

| | BCBUS0 | BCBUS0 | FPGA bank 5, pin J9 |

| | BCBUS1 | BCBUS1 | FPGA bank 3, pin K5 |

| | BCBUS2 | BCBUS2 | FPGA bank 3, pin L4 |

| | BCBUS3 | BCBUS3 | FPGA bank 3, pin L5 |

| | BCBUS4 | BCBUS4 | FPGA bank 3, pin N12 |

|

|

SPI Flash

Optional SPI flash device maybe assembled in custom variants, normally it is not populatedOn-board serial configuration memory (U5) is provided by Winbond with 64 MBit (8 MByte) storage capacity. This non volatile memory is used to store initial FPGA configuration via JTAG interface. The memory is connected to FPGA bank 8 via SPI interface.

| Scroll Title |

|---|

| anchor | Table_OBP_QSPI |

|---|

| title | Quad SPI Flash memory interface |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Signal Schematic Name | Connected to | Notes |

|---|

| F_CS | FPGA bank 8, pin B3 | Chip select | | F_CLK | FPGA bank 8, pin A3 | Clock | | F_DI | FPGA bank 8, pin A2 | Data in / out | | nSTATUS | FPGA bank 8, pin C4 | Data in / out, configuration dual-purpose pin of FPGA | | DEVCLRN | FPGA bank 8, pin B9 | Data in / out, configuration dual-purpose pin of FPGA | | F_DO | FPGA bank 8, pin B2 | Data in / out |

|

...

The configuration of FTDI FT2232H chip is pre-programmed on in the EEPROM U9.

| Scroll Title |

|---|

| anchor | Table_OBP_EEP |

|---|

| title | I2C EEPROM interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic | Connected to | Notes |

|---|

EECS | FTDI U3, Pin EECS |

| | EECLK | FTDI U3, Pin EECLK |

| | EEDATA | FTDI U3, Pin EEDATA |

|

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_CLK |

|---|

| title | Osillators |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Clock Source | Schematic Name | Frequency | Note |

|---|

| Microchip MEMS Oscillator, U7 | CLK12M | 12.00 MHz | Connected to FTDI FT2232 U3, pin 3. Connected to FPGA SoC bank 2, pin H6. |

|

...

| Page properties |

|---|

|

In 'Power and Power-on Sequence' section there are three important digrams which must be drawn: - Power on-sequence

- Power distribution

- Voltage monitoring circuit

|

Power Supply

To power-up the module, power supply with minimum current capability of 1A is recommendedThe module is power supplied from USB (optionally via unpopulated pin header).

Power Consumption

| Scroll Title |

|---|

| anchor | Table_PWR_PC |

|---|

| title | Power Consumption |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA | Typical Current |

|---|

| Intel MAX 10 10M08 FPGA SoCFPGA | TBD* |

|

* TBD - To Be Determined

...

| Scroll Title |

|---|

| anchor | Table_RH_DCH |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Contributor | Description |

|---|

| Page info |

|---|

| infoType | Modified date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | | v.98 | ED | | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| |

|

...