...

| Page properties |

|---|

|

Important General Note:

|

...

| Scroll Title |

|---|

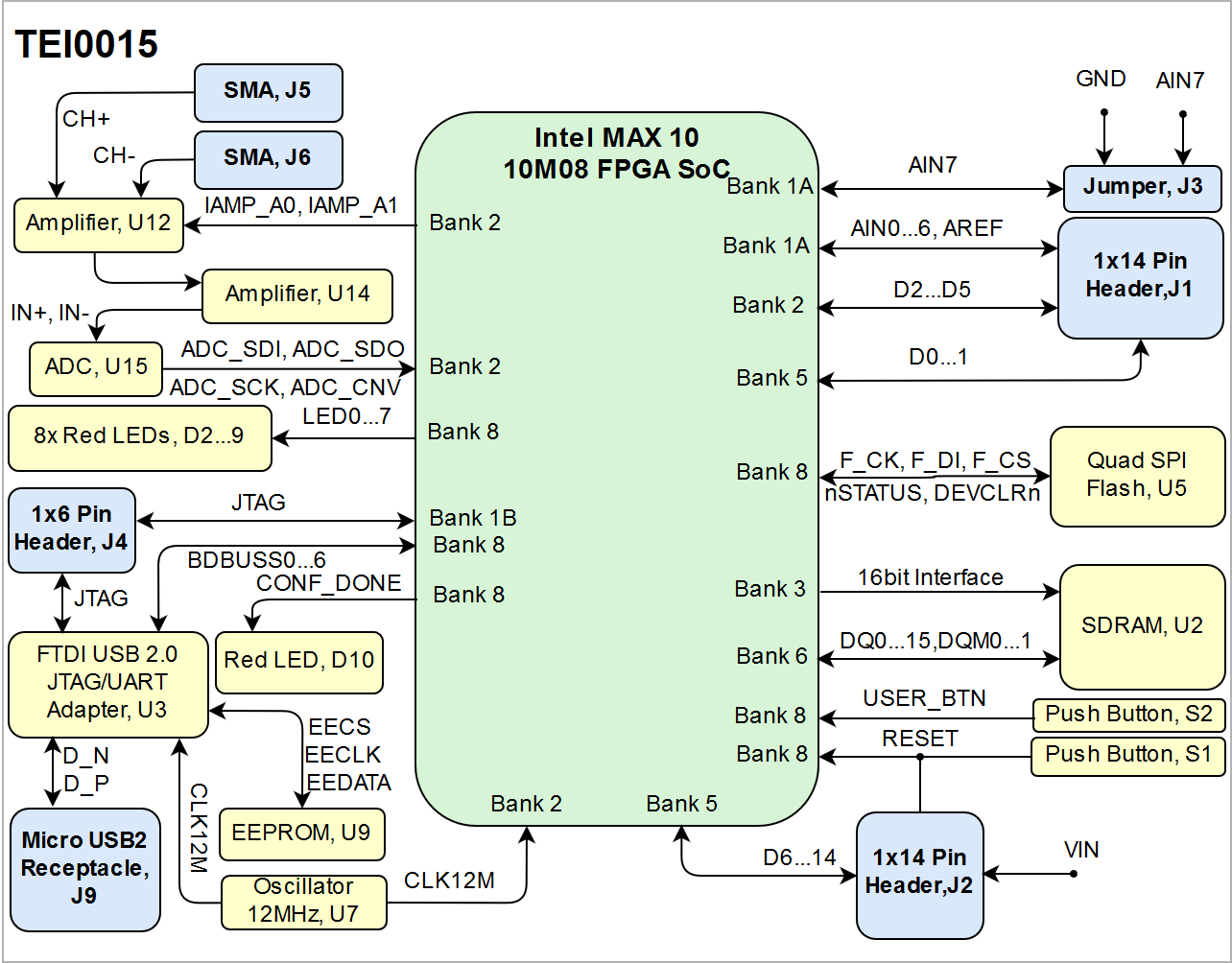

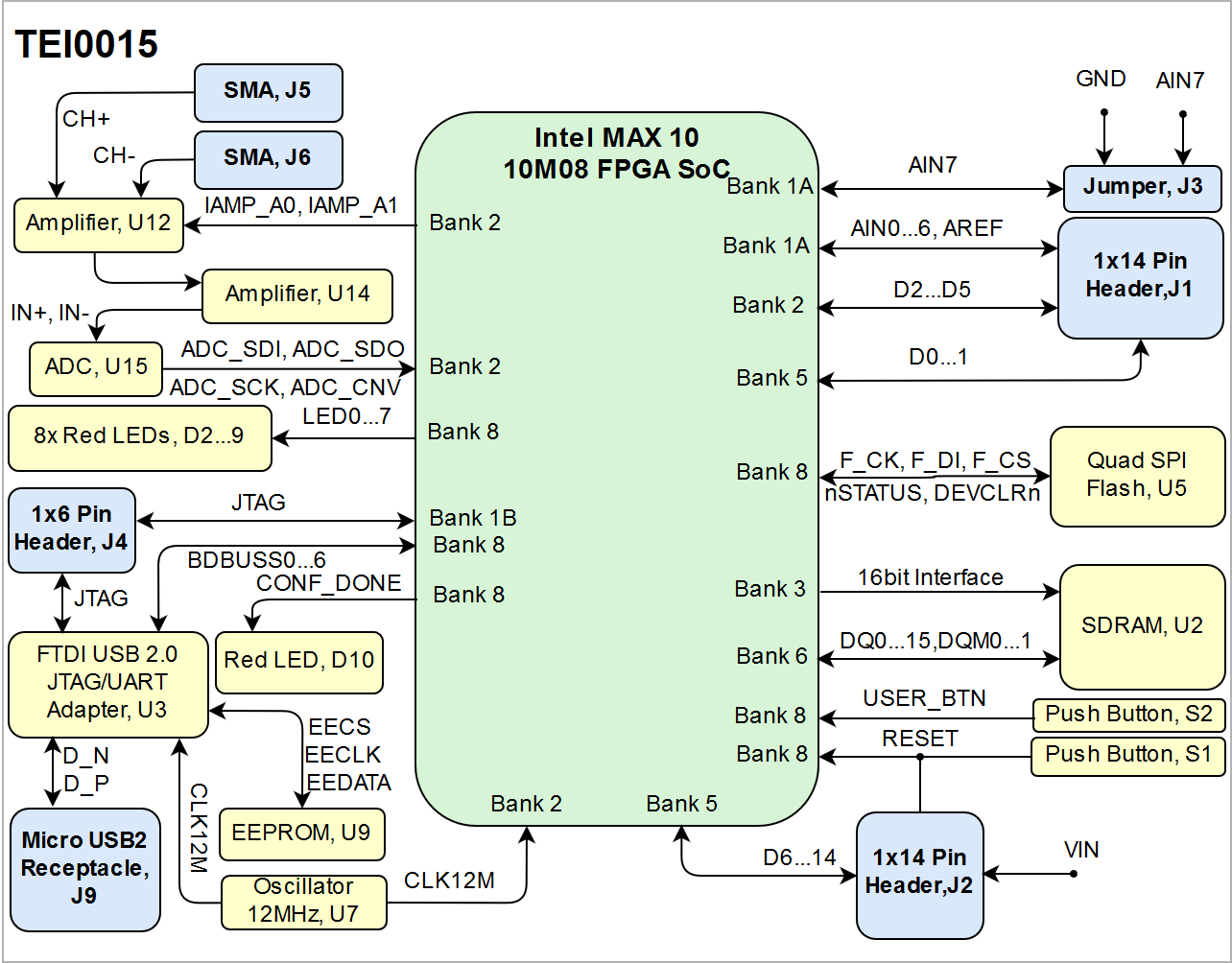

| anchor | Figure_OV_BD |

|---|

| title | TEI0015 block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| fitWindow | false | diagramDisplayName |

|---|

| lbox | true |

|---|

revision | 27 | | diagramName | TEI0015_OV_BD |

|---|

| simpleViewer | false | width |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| lbox | true |

|---|

| diagramWidth | 642 |

|---|

| revision | 27 |

|---|

|

|

| Scroll Only |

|---|

|

|

Main Components

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

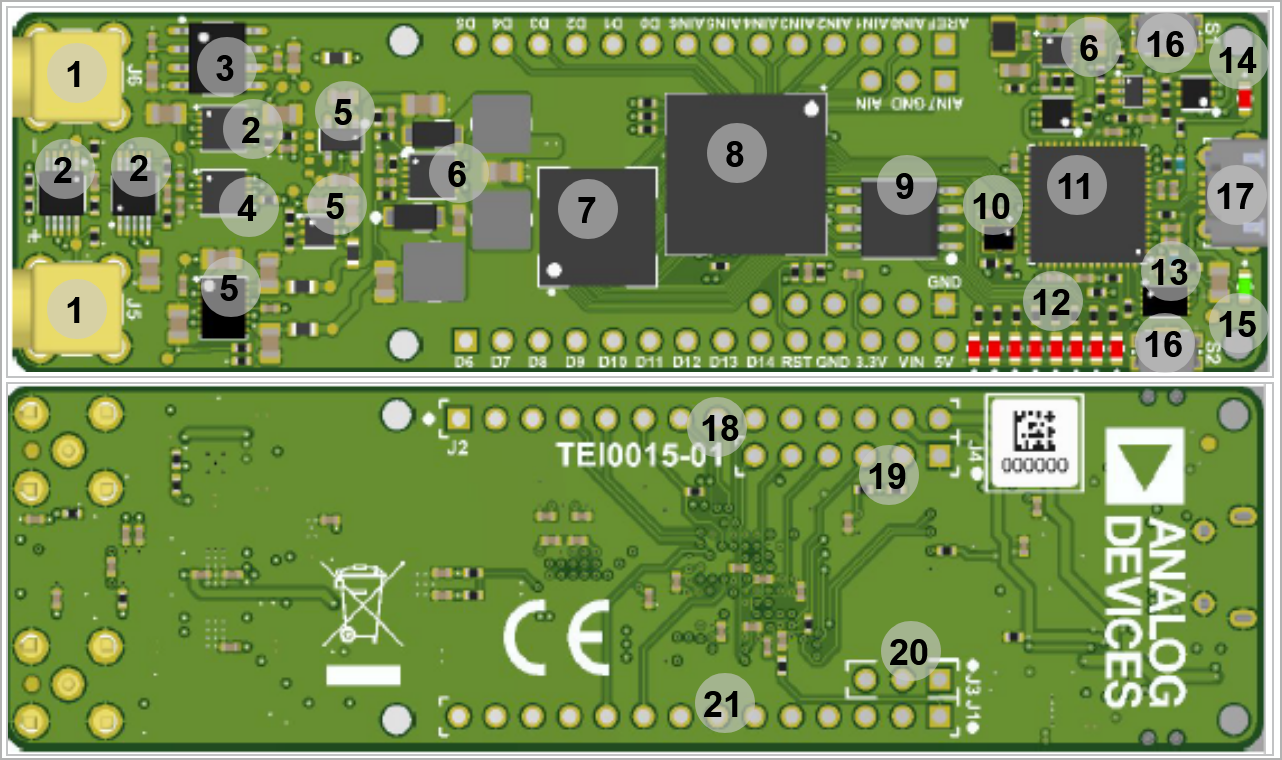

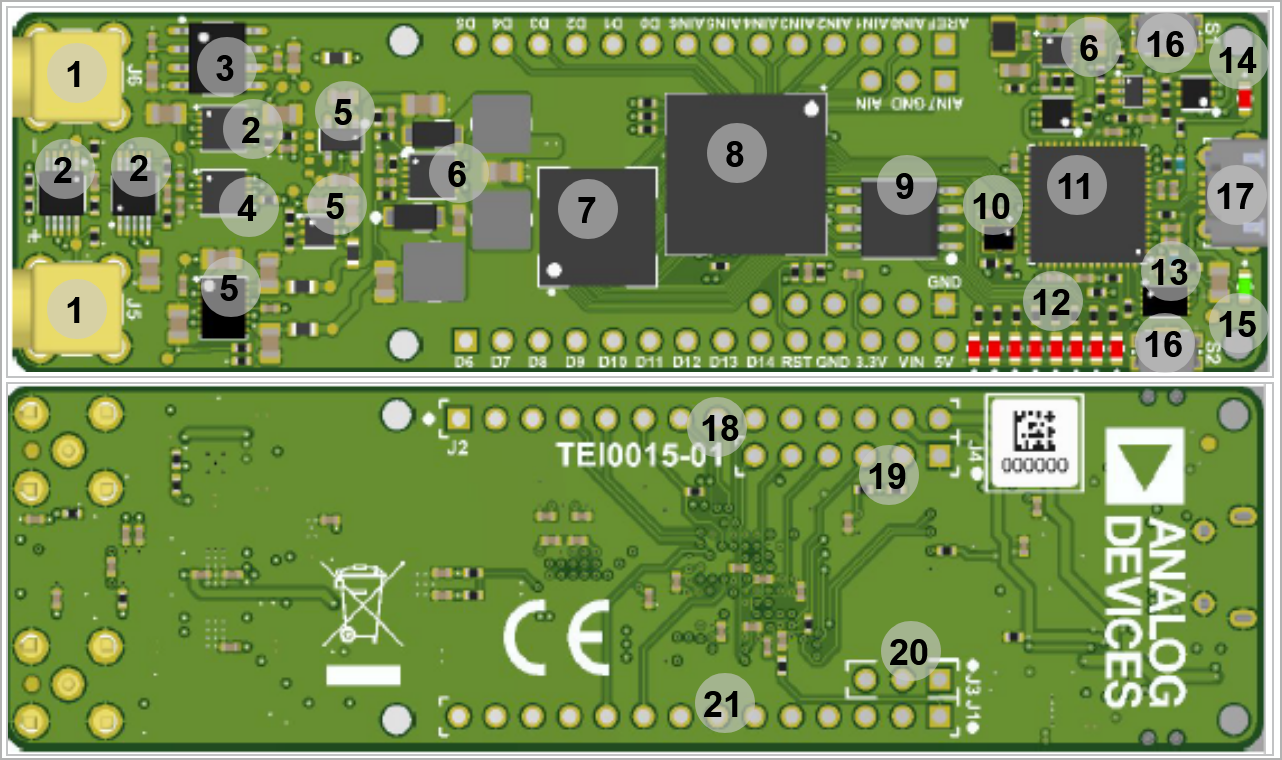

| title | TEI0015 main components |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| fitWindow | false | diagramDisplayName |

|---|

| lbox | true |

|---|

revision | 13 | | diagramName | TEI0015_OV_MC |

|---|

| simpleViewer | false | width |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 13 |

|---|

|

|

| Scroll Only |

|---|

|

|

SMA Connector, J5...6

Amplifier, U12 - U14 - U6

Series Voltage Reference, U8

Analog to Digital Converter, U15

Voltage Regulator, U10 - U13 - U16

Switching Voltage Regulator, U11 - U4

SDRAM Memory, U2

- Intel® MAX 10, U1

SPI Flash Memory, U5

12.00 MHz MEMS oscillator, U7

FTDI USB2 to JTAG/UART adapter, U3

User LEDs, D2...9

FTDI configuration EEPROM, U9

Configuration/Status LED (Red) , D10

Power-on LED (Green), D1

Push button, S1...2

Micro USB Connector, J9

1x14 pin header, J2 (Not assembled)

1x6 pin header, J4 (Not assembled)

1x4 Header, J3 (Not assembled)

1x14 pin header, J1 (Not assembled)

...

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Storage device name | Content | Notes |

|---|

Quad SPI Flash | Not Programmed |

| | EEPROM | Programmed | FTDI configuration | | SDRAM | Not Programmed |

|

|

...

| Scroll Title |

|---|

| anchor | Table_OV_RST |

|---|

| title | Reset process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style | widths |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Signal | Push Button | Pin Header | Note |

|---|

RESET | S1 | J2 | Connected to nCONFIG |

|

...

| Scroll Title |

|---|

| anchor | Table_SIP_GIOs |

|---|

| title | General I/Os to Pin Headers and connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style | widths |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA Bank | Connector Designator | I/O Signal Count | Voltage Level | Notes |

|---|

| Bank 1A | J1 | 7 | 3.3V | AIN0...6 | | Bank 1B | J4 | 5 | 3.3V | JTAG interface | | Bank 2 | J1 | 4 | 3.3V | DIO2...5 | | Bank 5 | J2 | 9 | 3.3V | DIO6...14 | | J1 | 2 | 3.3V | DIO0...1 | | Bank 8 | J2 | 1 | 3.3V | RESET |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_USB |

|---|

| title | Micro USB-2 connector pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pins | Connected to | Note |

|---|

| VBUS | USB_VBUS |

| | D+ | FTDI FT2232H U3, DP pin |

| | D- | FTDI FT2232H U3, DM pin |

|

|

...

| Scroll Title |

|---|

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

JTAG Signal | Pin Header Connector | Note |

|---|

| TMS | J4-6 |

| | TDI | J4-5 |

| | TDO | J4-4 |

| | TCK | J4-3 |

| | JTAG_EN | J4-2 | Pulled-up to 3.3V |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP |

|---|

| title | On board peripherals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_SDRAM |

|---|

| title | SDRAM interface IOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| SDRAM I/O Signals | Signal Schematic Name | Connected to | Notes |

|---|

| Address inputs | A0 ... A13 | bank 3 | - | | Bank address inputs | BA0 / BA1 | bank 3 | - | | Data input/output | DQ0 ... DQ15 | bank 6 | - | | Data mask | DQM0 ... DQM1 | bank 6 | - | | Clock | CLK | bank 3 | - | | Control Signals | CS | bank 3 | Chip select | CKE | bank 3 | Clock enable | RAS | bank 3 | Row Address Strobe | CAS | bank 3 | Column Address Strobe | | WE | bank 3 | Write Enable |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_FTDI |

|---|

| title | FTDI chip interfaces and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FTDI Chip U3 Pin | Signal Schematic Name | Connected to | Notes |

|---|

| ADBUS0 | TCK | FPGA bank 1B, pin G2 | JTAG interface | | ADBUS1 | TDI | FPGA bank 1B, pin F5 | | ADBUS2 | TDO | FPGA bank 1B, pin F6 | | ADBUS3 | TMS | FPGA bank 1B, pin G1 | | BDBUS0 | BDBUS0 | FPGA bank 8, pin A4 | User configurable | | BDBUS1 | BDBUS1 | FPGA bank 8, pin B4 | User configurable | | BDBUS2 | BDBUS2 | FPGA bank 8, pin B5 | User configurable | | BDBUS3 | BDBUS3 | FPGA bank 8, pin A6 | User configurable | | BDBUS4 | BDBUS4 | FPGA bank 8, pin B6 | User configurable | | BDBUS5 | BDBUS5 | FPGA bank 8, pin A7 | User configurable |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_QSPI |

|---|

| title | Quad SPI Flash memory interface |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| stylesortByColumnwidths | 1 |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Signal Schematic Name | Connected to | Notes |

|---|

| F_CS | FPGA bank 8, pin B3 | Chip select | | F_CLK | FPGA bank 8, pin A3 | Clock | | F_DI | FPGA bank 8, pin A2 | Data in / out | | nSTATUS | FPGA bank 8, pin C4 | Data in / out, configuration dual-purpose pin of FPGA | | DEVCLRN | FPGA bank 8, pin B9 | Data in / out, configuration dual-purpose pin of FPGA | | F_DO | FPGA bank 8, pin B2 | Data in / out |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_EEP |

|---|

| title | I2C EEPROM interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style | widths |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic | Connected to | Notes |

|---|

EECS | FTDI U3, Pin EECS |

| | EECLK | FTDI U3, Pin EECLK |

| | EEDATA | FTDI U3, Pin EEDATA |

|

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_A2D |

|---|

| title | A2D converter interface and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pins | Connected to | Notes |

|---|

IN+ | Diff Amplifier U14, VOUT- |

| | IN- | Diff Amplifier U14, VOUT+ |

| | SDI | FPGA, bank 2, pin M2, ADC_SDI |

| | SDO | FPGA, bank 2, pin M1, ADC_SDO |

| | SCK | FPGA, bank 2, pin N3, ADC_SCK |

| | CNV | FPGA, bank 2, pin N2, ADC_CNV |

|

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_LED |

|---|

| title | On-board LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Color | Connected to | Active Level | Note |

|---|

| D2...9 | Red | LED1...8 | Active High | User LEDs | | D10 | Red | CONF_DONE | Active Low | Configuration DONE LED | | D1 | Green | 3.3V | Active High | After power on it will be on. |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_LED |

|---|

| title | On-board Push Buttons |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Connected to | Functionality | Note |

|---|

| S1 | RESET | General reset |

| | S2 | USER_BTN | User push button | Connected to FPGA Bank 8. |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_CLK |

|---|

| title | Osillators |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Clock Source | Schematic Name | Frequency | Note |

|---|

| Microchip MEMS Oscillator, U7 | CLK12M | 12.00 MHz | Connected to FTDI FT2232 U3, pin 3. Connected to FPGA SoC bank 2, pin H6. |

|

...

| Scroll Title |

|---|

| anchor | Table_PWR_PC |

|---|

| title | Power Consumption |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA | Typical Current |

|---|

| Intel MAX 10 10M08 FPGA SoC | TBD* |

|

...

| Scroll Title |

|---|

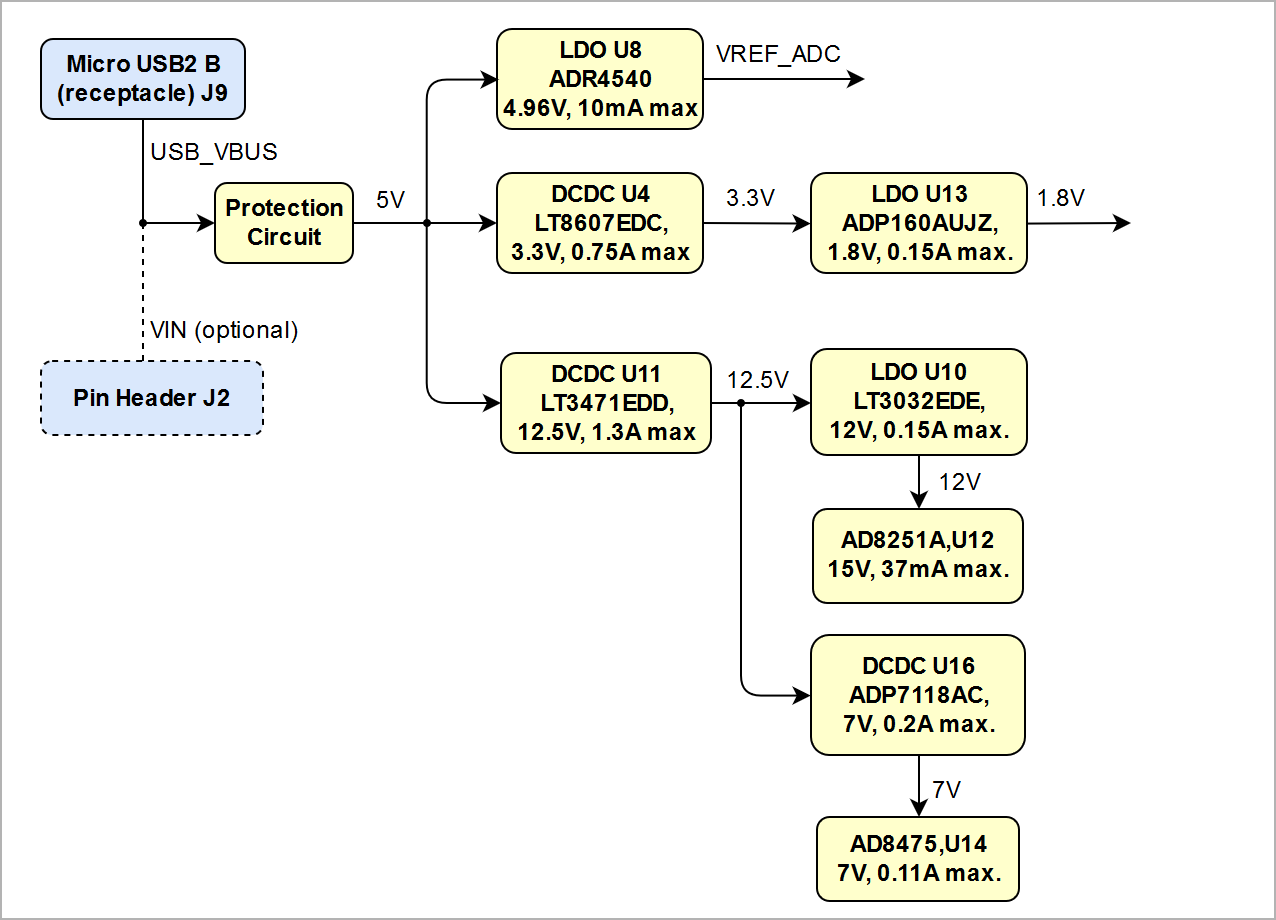

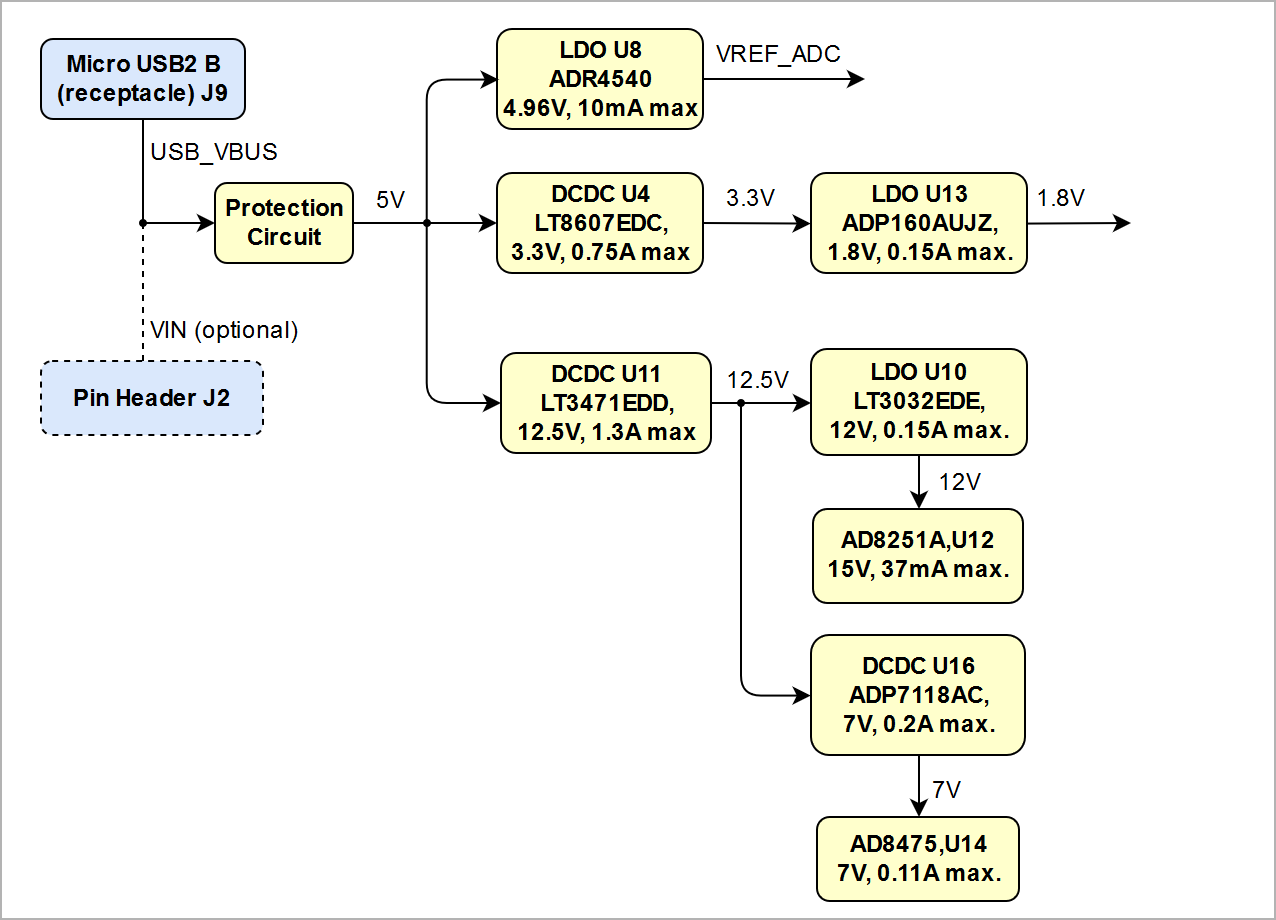

| anchor | Figure_PWR_PD |

|---|

| title | Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | TEI0015_PWR_P |

|---|

| lbox | true |

|---|

| revision | 12 |

|---|

| diagramName | TEI0015_PWR_PD |

|---|

| simpleViewer | false |

|---|

| width | links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | TEI0015_PWR_P |

|---|

| lbox | true |

|---|

| diagramWidth | 638 |

|---|

| revision | 12 |

|---|

|

|

| Scroll Only |

|---|

|

|

Power-On Sequence

...

| Scroll Title |

|---|

| anchor | Table_PWR_PR |

|---|

| title | Module power rails. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style | widths |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Rail Name | Connector J2 Pin | Connector J9 Pin | Direction | Notes |

|---|

| VIN | J2-13 | - | Input | 5 V - Pin Header | | 3.3V | J2-12 | - | Output |

| | 5V | J2-14 | - | Output |

| USB_VBUS | - | J9-1 | Input | 5 V - USB Connector |

|

...

| Scroll Title |

|---|

| anchor | Table_PWR_BV |

|---|

| title | Intel MAX 10 SoC bank voltages. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic Name | | Notes |

|---|

| Bank 1A | VCCIO1A | 3.3V |

| | Bank 1B | VCCIO1B | 3.3V |

| | Bank 2 | VCCIO2 | 3.3V |

| | Bank 3 | VCCIO3 | 3.3V |

| | Bank 5 | VCCIO5 | 3.3V |

| | Bank 6 | VCCIO6 | 3.3V |

| | Bank 8 | VCCIO8 | 3.3V |

|

|

...

| Scroll Title |

|---|

| anchor | Table_TS_AMR |

|---|

| title | Absolute maximum ratings |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Symbols | Description | Min | Max | Unit | Reference Document |

|---|

VIN | Supply voltage | 4.75 | 5.25 | V |

| | CH1-, CH1+ | Analog input voltage on amplifier U12 pin 1, 10 | -30 | 30 | V | AD8251 datasheet | T_STG | Storage Temperature | -25 | +85 | °C |

|

|

...

| Scroll Title |

|---|

| anchor | Table_TS_ROC |

|---|

| title | Recommended operating conditions. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style | widths |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Symbols | Min | Max | Unit | Reference Document |

|---|

VIN supply voltage (5.0V nominal) | 4.75 | 5.25 | V |

| | Analog input voltage on amplifier U12 pin 1 (CH1-), 10 (CH1+) | -10 | 10 | V | AD8251 datasheet | T_OP | 0 | +70 | °C | W9864G6JT-6 datasheet |

|

...

| Scroll Title |

|---|

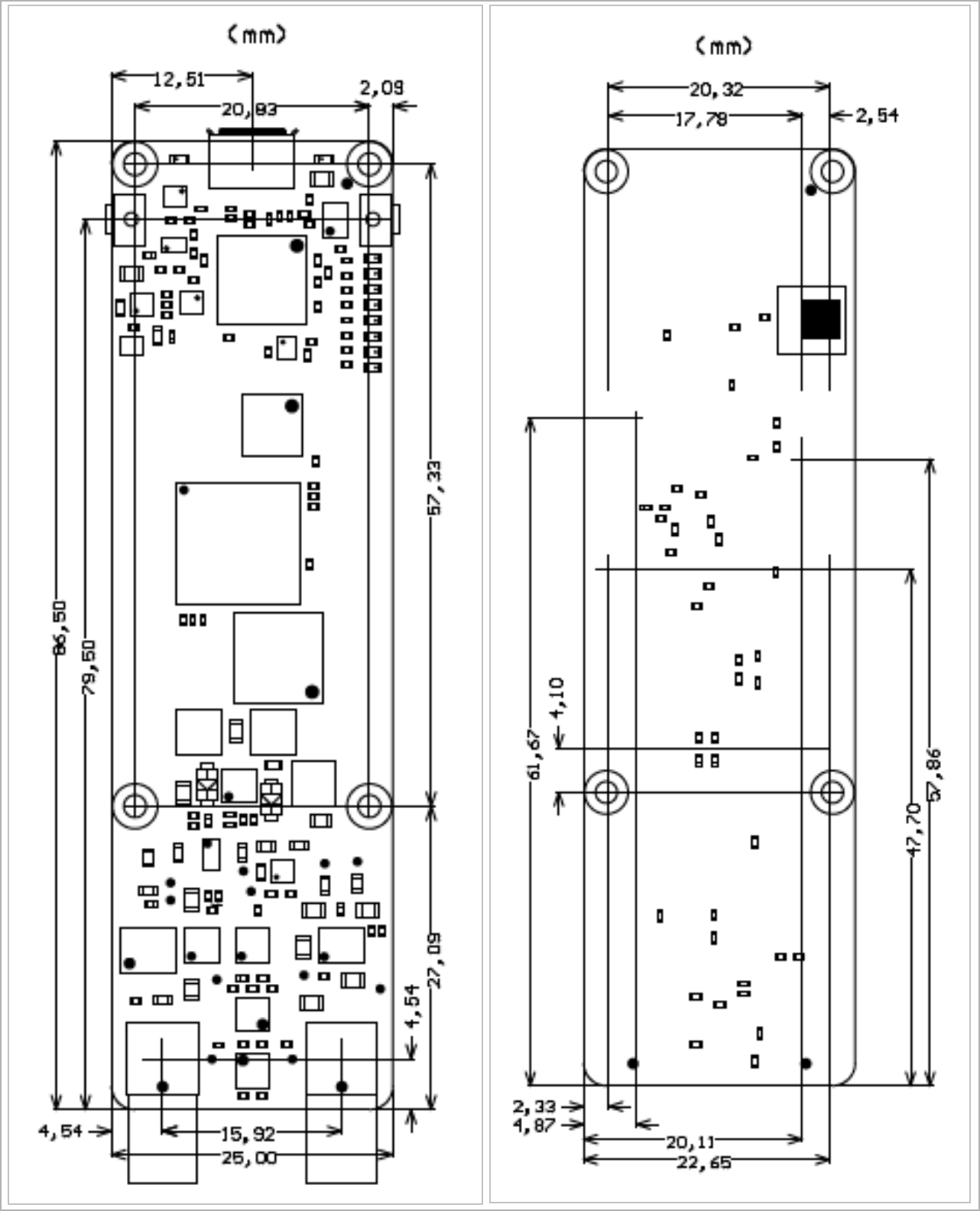

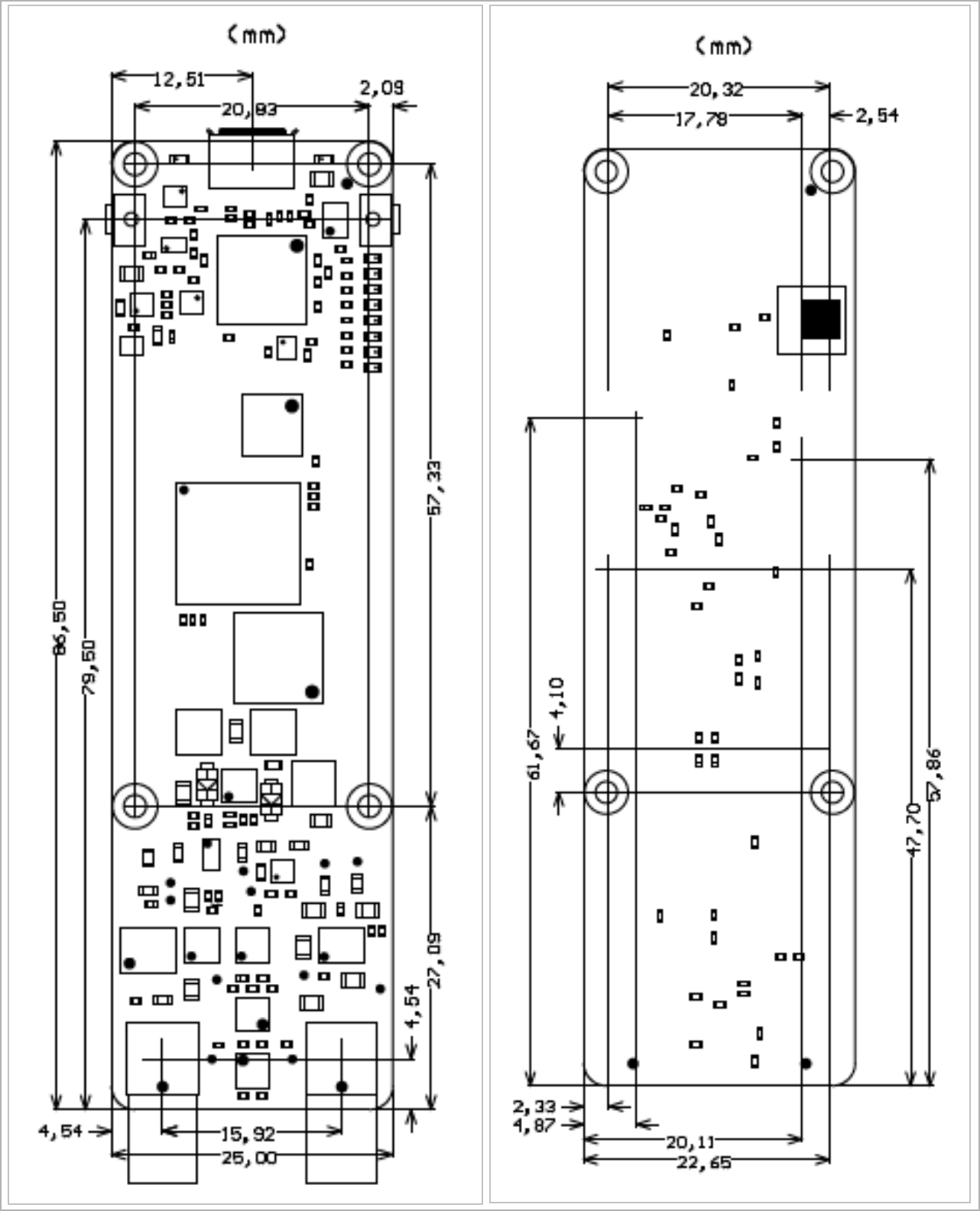

| anchor | Figure_TS_PD |

|---|

| title | Physical Dimension |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| fitWindow | false | diagramDisplayName |

|---|

| lbox | true |

|---|

| revision | 1 |

|---|

| diagramName | TEI0015_TS_PD |

|---|

| simpleViewer | false |

|---|

| width | links | auto |

|---|

| tbstyle | hidden |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 1 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

|

...

| Scroll Title |

|---|

| anchor | Table_VCP_SO |

|---|

| title | Trenz Electronic Shop Overview |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style | widths |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

Revision History

Hardware Revision History

| Scroll Title |

|---|

| anchor | Table_RH_HRH |

|---|

| title | Hardware Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style |

|---|

| widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Changes | Documentation Link |

|---|

| 20202019-0102-3111 | 01 | - | REV01 |

|

Hardware revision number can be found on the PCB board together with the module model number separated by the dash.

| Scroll Title |

|---|

| anchor | Figure_RV_HRN |

|---|

| title | Board hardware revision number. |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| fitWindow | false | diagramDisplayName |

|---|

| lbox | true |

|---|

revision | 2 | | diagramName | TEI0015_RH_RHN |

|---|

| simpleViewer | false |

|---|

| width | links | auto |

|---|

| tbstyle | hidden |

|---|

| lbox | true |

|---|

| diagramWidth | 158 |

|---|

| revision | 2 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

|

...

| Scroll Title |

|---|

| anchor | Table_RH_DCH |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style | widths |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Contributor | Description |

|---|

| Page info |

|---|

| infoType | Modified date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| |

|

...