...

The Trenz Electronic TEI0015 is an commercial-grade module based on Intel® , low cost and small size module integrated with Intel® MAX 10. Intel Intel MAX 10 devices are the ideal solution for system management, I/O expansion, communication control planes, industrial, automotive, and consumer applications.

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

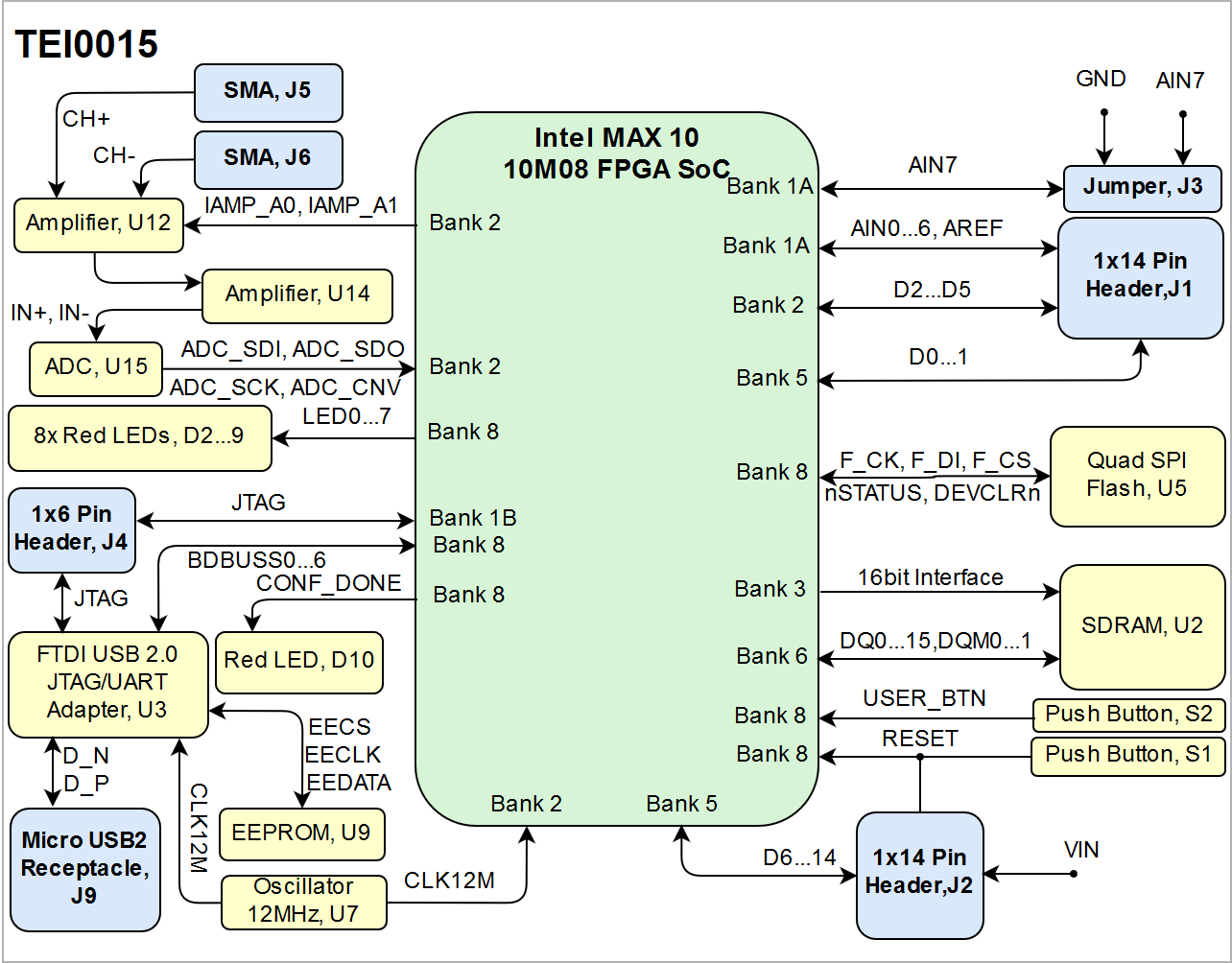

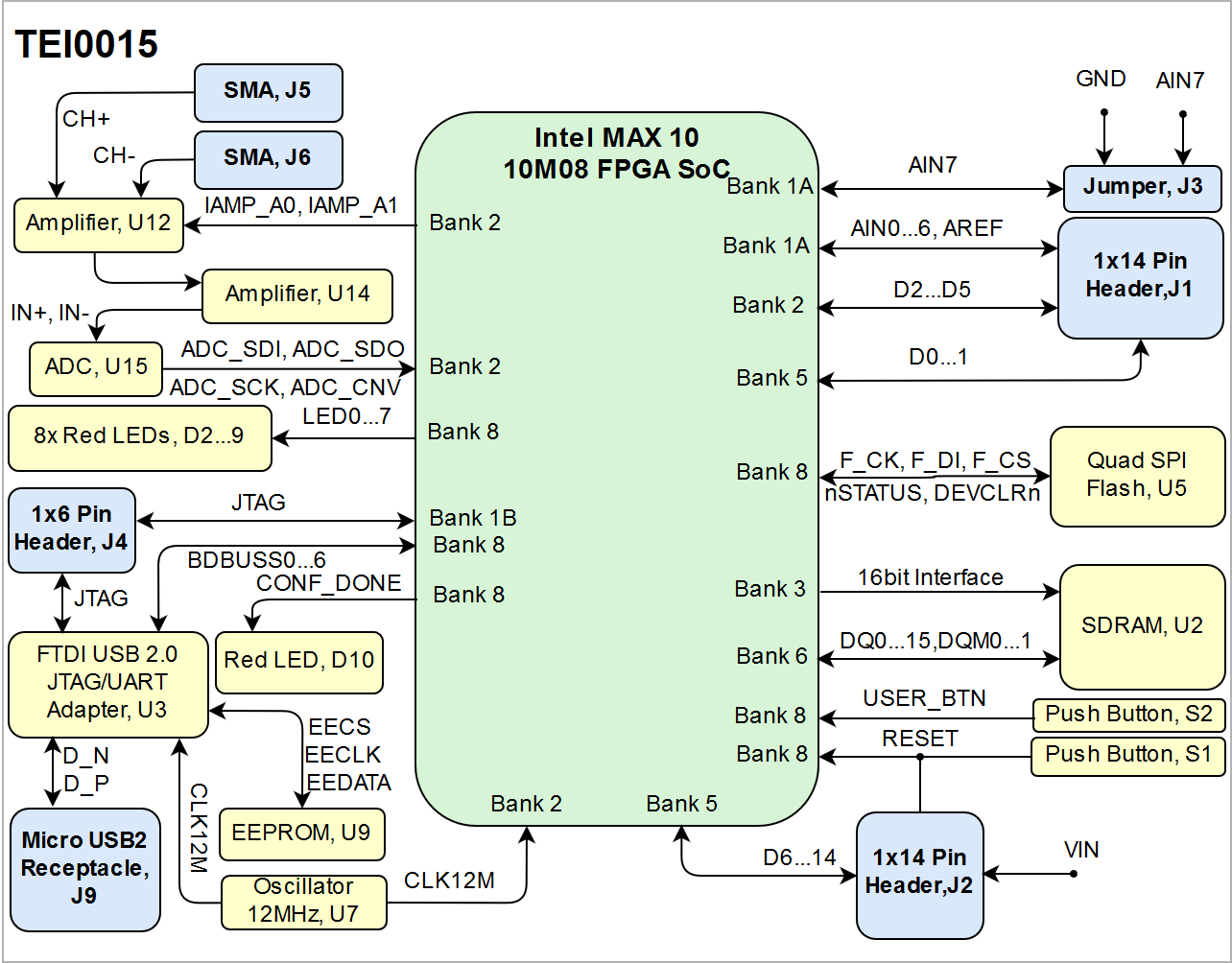

| title | TExxxx block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 68 |

|---|

| diagramName | TEI0015_OV_BD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

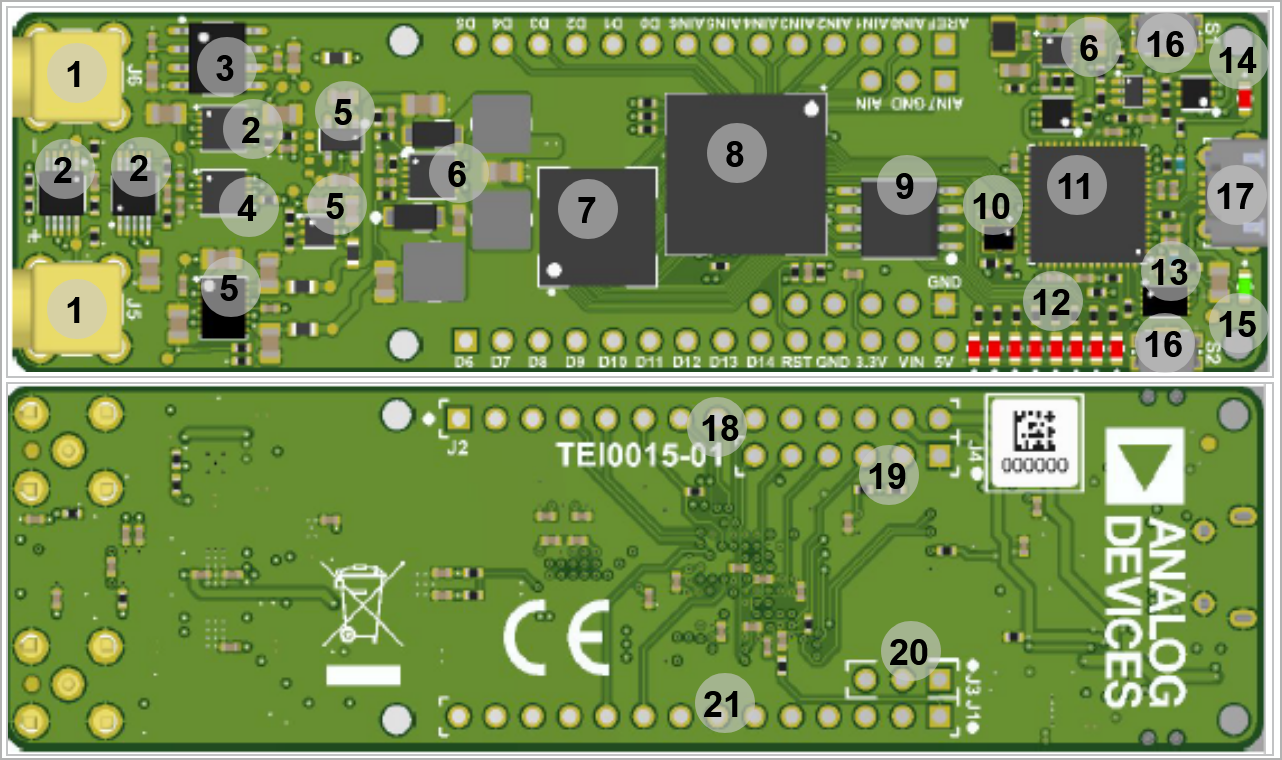

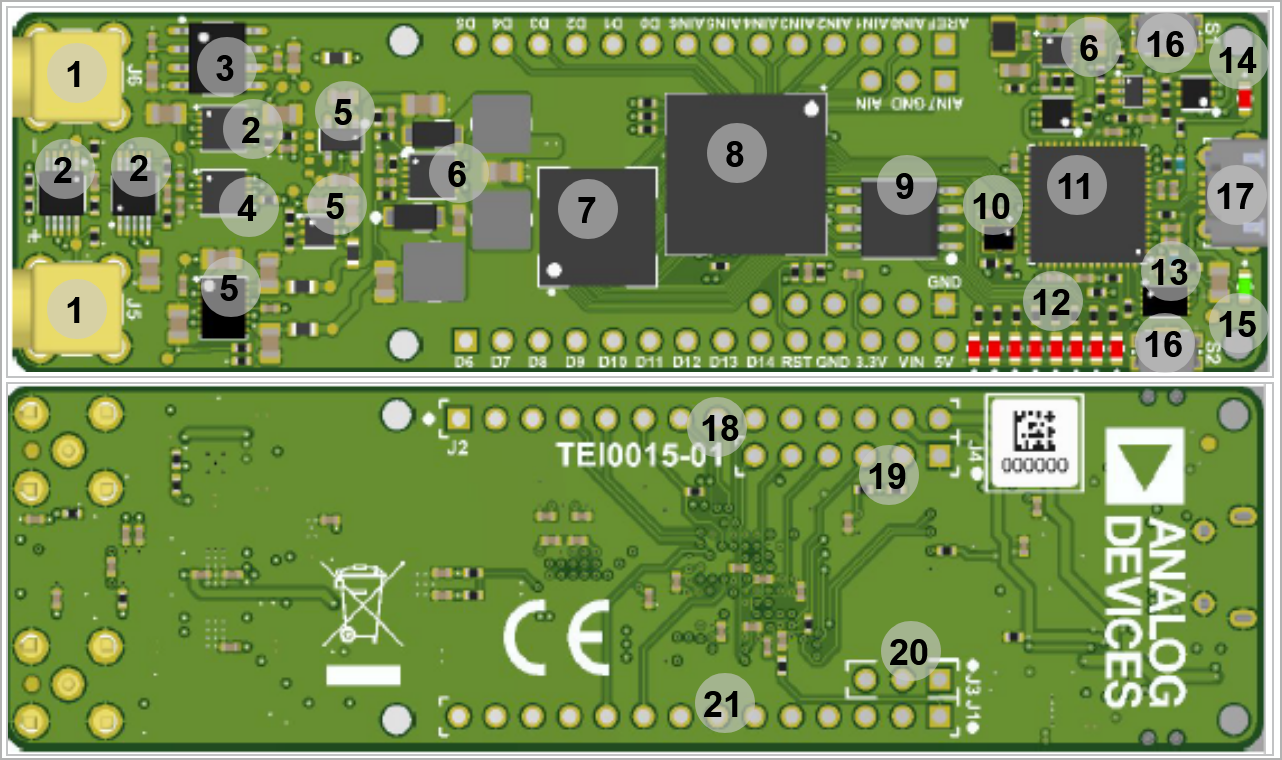

| title | TEI0015 main components |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 56 |

|---|

| diagramName | TEI0015_OV_MC |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

- SMA Connector, J5...6

- Instrumentation Amplifier, U12- U14

- Series Voltage Reference, U8

- Analog to Digital Convertor, U15- U6

- Voltage Regulator, U10- U13- U16

- Buck Switching Regulator, U11- U4

- Intel® MAX 10, U1

- SDRAM Memory, U2

- SPI Flash Memory, U5

- USP to UART convertor, U3

- User LEDs, D2...9

- 4Kb EEPROM, U9

- Switch, S1...2

- USB port, J9

- Pin Holder (Not assembled), J1...4

Initial Delivery State

| Page properties |

|---|

|

Notes : Only components like EEPROM, QSPI flash and DDR3 can be initialized by default at manufacture. If there is no components which might have initial data ( possible on carrier) you must keep the table empty |

...

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Storage device name | Content | Notes |

|---|

Quad SPI Flash | Not Programmed |

| | I2C Configuration EEPROM | Not Programmed |

| | SDRAM | Not Programmed |

|

|

Configuration Signals

| Page properties |

|---|

|

- Overview of Boot Mode, Reset, Enables.

|

| Scroll Title |

|---|

| anchor | Table_OV_BP |

|---|

| title | Boot process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

style | widths | | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

MODE Signal State | Boot Mode |

|---|

The FPGA configuration for Intel MAX 10 FPGAs can be stored through JTAG interface either in external configuration device (QSPI flash memory U5) or on the FPGA itself since the Intel MAX 10 FPGA offers non-volatile memory on chip. The FPGA configuration is loaded from the non-volatile memory when the board is powered up.

To configure the FPGA directly, the JTAG interface can be used to configure the FPGA volatile, means the configuration is lost after power off.

Reset process must be done by pressing push button S1.

| Scroll Title |

|---|

| anchor | Table_OV_RST |

|---|

| title | Reset process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| B2B | I/O| Push Button | Pin Header | Note |

|---|

RESET | S1 | J2 | connected to nCONFIG |

|

Signals, Interfaces and Pins

| Page properties |

|---|

|

Notes : - For carrier or stand-alone boards use subsection for every connector type (add designator on description, not on the subsection title), for example:

- For modules which needs carrier use only classes and refer to B2B connector if more than one is used, for example

|

...

I/Os

...

on Pin Headers and Connectors

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General PL I/O to B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA Bank | B2B Connector Designator | I/O Signal Count | Voltage Level | Notes |

|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

...