Page History

...

| Excerpt |

|---|

|

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||

|

...

For general structure and of the reference design, see Project Delivery - Xilinx devices

Design Sources

| Scroll Title | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||

|

...

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

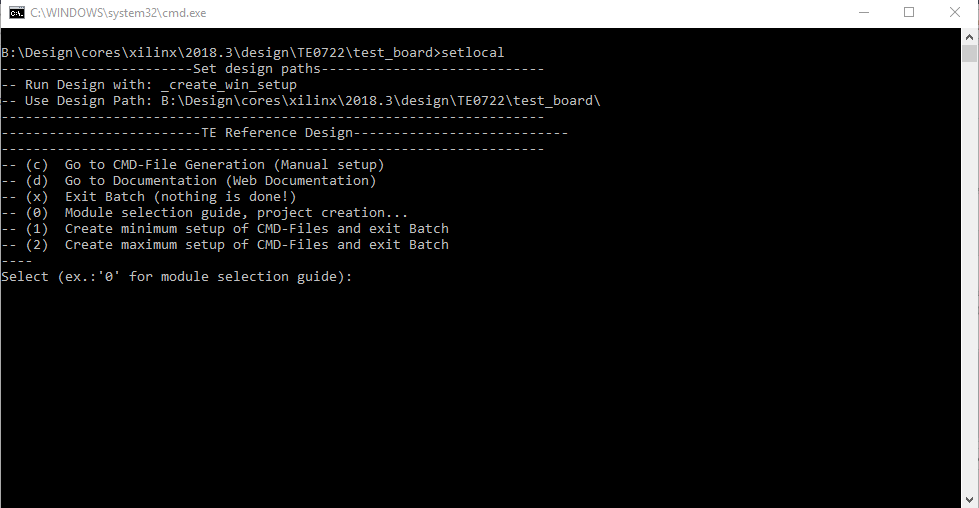

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: Vivado TCL: TE::sw_run_sdk

Note: Projects contains 3 FSBL template: zynq_fsbl (FSBL modified for DDR Less application → use for Boot.bin), zynq_fsbl_app (FSBL modified for DDR Less application and with demo app included → create Boot with this FSBL and Bitstream only), zynq_fsbl_flash(FSBL modified for Flash programming →FSBL which must be selected separately to program Flash)See SDK Projects

Info TE0722 is without DDR, so special FSBL (sources on reference designs) is needed, see also: DDR less ZYNQ Design

- Run on Vivado TCL: TE::sw_run_hsi

...

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp zynq_fsbl_app

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

...

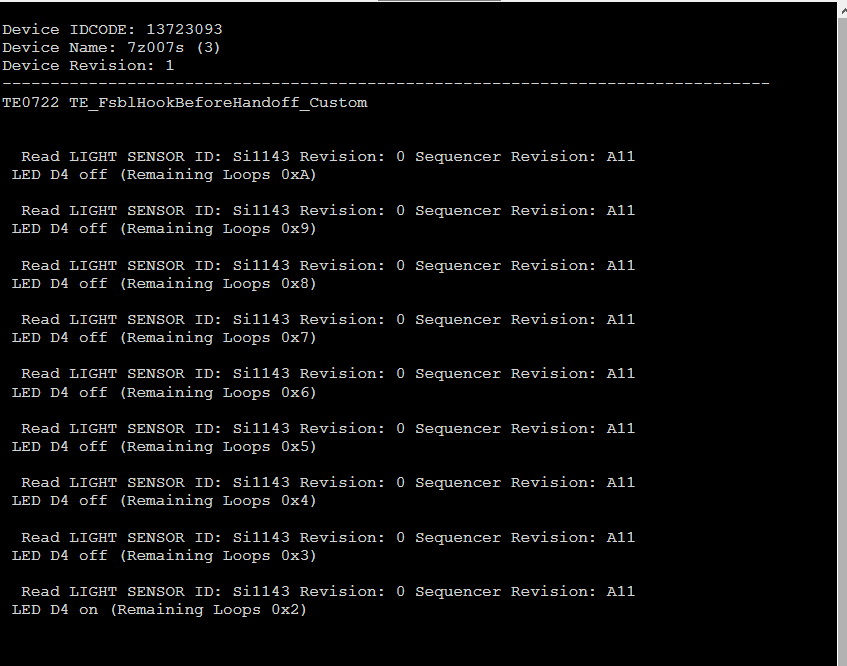

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Output:

- Default output appears only 10 time. Reboot device: force ResN Pin to GND for short time, location see: TE0722 Getting Started

Started

alternately: comment define #define ENABLE_TE_HOOKS_BH on te_fsbl_hooks.h to disable Sensor and LED access example and regenerate FSBL and Boot.bin again

- Default output appears only 10 time. Reboot device: force ResN Pin to GND for short time, location see: TE0722 Getting Started

Vivado HW Manager

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

---------------------------------------------------------- FPGA Example scuMCS Firmware to configure SI5338 and Reset System. srec_spi_bootloaderTE modified 2018.3 SREC Bootloader to load app or second bootloader from flash into DDR Descriptions:

xilisf_v5_11TE modified 2018.3 xilisf_v5_11

---------------------------------------------------------- Zynq Example: zynq_fsblTE modified 2018.3 FSBL General:

Module Specific:

zynq_fsbl_flashTE modified 2018.3 FSBL General:

ZynqMP Example: ---------------------------------------------------------- zynqmp_fsblTE modified 2018.3 FSBL General:

Module Specific:

zynqmp_fsbl_flashTE modified 2018.3 FSBL General:

zynqmp_pmufwXilinx default PMU firmware. ---------------------------------------------------------- General Example: hello_te0820Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output. u-bootU-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin. |

Source location: \sw_lib\sw_apps

...

Boot.bin. |

Source location: \sw_lib\sw_apps

zynq_fsbl

TE modified 2018.3 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

- Disable Memory initialisation on main.c

zynq_fsbl_app

TE modified 2018.3 FSBL

General:

...

- Add Files: all TE Files start with te_*

- Example app for LED access over MIO and sensor access over I2C

zynq_fsbl_flash

TE modified 2018.3 FSBL

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

...