- Created by Thomas Dück, last modified on 17 06, 2021

You are viewing an old version of this page. View the current version.

Compare with Current View Page History

« Previous Version 11 Next »

Quick Start

The most Trenz Electronic FPGA Reference Designs are TCL-script based projects.

The "normal" Quartus project will be generated in the subfolder "/quartus/" and the additional software part will be generated in the subfolder "/software/" after executing scripts.

To create project do the following steps:

- Execute "create_project_win.cmd" or "create_project_linux.sh"

- Select your board in "Board selection"

- Click on "Create project" button

For more details and manual configuration of design basic settings, see Reference Design - Getting Started.

For Problems, please check Checklist / Troubleshoot at first.

Zip Project Delivery

Zip Name Description

| Description | PCB Name | Project Name+(opt. Variant) | supported Quartus Version | Date | ||||

|---|---|---|---|---|---|---|---|---|

| Example: | TEI0006 | - | test_board(_noprebuilt) | - | quartus_20.4 | - | 20210616153551 | .zip |

Last supported Release

| Type or File | Version |

|---|---|

| Quartus Prime | 20.1 lite / 20.4 pro |

| Trenz Project Scripts | 20.0 |

| Trenz <board_series>_devices.csv | 1.1 |

| Trenz zip_ignore_list.csv | 1.2 |

| Trenz mod_list.csv | 1.2 |

| Trenz apps_list.csv | 1.0 |

Currently limitations of functionality

- Quartus Prime Lite 19.1 for Windows: requires a patch

- Reason: error message when generating any EMIF IP or Cyclone® V/Arria® V HPS IP

- Workaround: See https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/tools/2020/fatal--cannot-generate-ip-in-a-windows-evironment-.html

- Quartus Prime Lite 20.1.1 for Windows:

- Reason: Error: (11133): IP component with file "<path to file>" upgrade failed

- Workaround: Add "<ALIAS>GPIO Lite Intel FPGA IP v20.1</ALIAS>" to *.lst file in Quartus installation directory: e.g. C:\intelFPGA_lite\20.1\ip\altera\altera_gpio_lite\altera_gpio_lite_wizard.lst

- Quartus Prime Lite 19.1 for Windows: requires a patch

Directory structure

| File or Directory | Type | Description |

|---|---|---|

| <project folder> | work, base directory | Base directory with predefined batch files (*.cmd, *.sh) to create quartus project, open quartus project or program device |

| <project folder>/backup/ | generated | (Optional) Directory for project backups |

| <project folder>/board_files/ | source | Local list of available board variants (<board_series>_devices.csv) |

| <project folder>/log/ | generated | (Temporary) Directory with quartus log files (used only with predefined commands from tcl scripts, otherwise this logs will be writen into the quartus work directory) |

| <project folder>/prebuilt/ | prebuilt | Contains subfolders for different board variants |

| <project folder>/prebuilt/<board_part_shortname> | prebuilt | Directory with prebuilt programming files (*.pof, *.sof or *.jic) for FPGA and different source files for hardware (*.sopcinfo) and software (*.elf) included in subfolders |

| <project folder>/prebuilt/<board_part_shortname>/programming_files/ | prebuilt | Directory with prebuilt programming files (*.pof, *.sof or *.jic) |

| <project folder>/prebuilt/<board_part_shortname>/hardware/ | prebuilt | Directory with prebuilt hardware sources (*.sopcinfo) |

| <project folder>/prebuilt/<board_part_shortname>/software/ | prebuilt | Directory with prebuilt software sources (*.elf) |

| <project folder>/quartus/ | generated | (Temporary) Directory where quartus project is created. Quartus project file is <project_name>.qpf |

| <project folder>/scripts/ | source | TCL scripts to build a project |

| <project folder>/settings/ | source | (Optional) Additional design settings: zip_ignore_list.csv, mod_list.csv, design_basic_settings.tcl |

<project folder>/software/ | generated | (Temporary) Directory with additional software |

| <project folder>/source_files/ | source | Directory with source files needed for create project |

<project folder>/source_files/quartus/ <project folder>/source_files/<Board Part Shortname>/quartus | source | Source files for quartus project optional, source files for specific assembly variants |

<project folder>/source_files/software/ <project folder>/source_files/<Board Part Shortname>/software | source | Source files for additional software optional, source files for specific assembly variants |

Command Files

create_project_win.cmd/create_project_linux.sh

Use to create project, open project or program device.

'Create Project' GUI

- Board selection

Select your board from listed modules. To find easier the correct board you can use the filter function. Click on "Clear filter" button to reset the filter and show all available modules.

- Documentation

Some links to more information about the board, reference design, schematics and create_project_win.cmd/create_project_linux.sh gui.

- Messages

Messagebox shows different info, warning and error messages.

- Buttons

- Create project→ start create project from source files for selected board in "Board selection".

- Open project → open existing project in quartus prime gui.

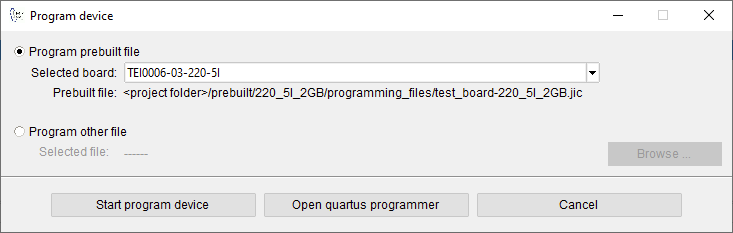

- Program device → opens "Program device" window:

Program device window - example image

Program device window - example image

- Select between "Program prebuilt file" (if available, download reference design with prebuilt files is required) and "Program other file" (select your own generated file via "Browse ..." button).

- Buttons:

- Browse ... → choose path to own generated programming file

- Start program device → start program device with selected programming file

- Open quartus programmer → open Quartus Programmer GUI

- Cancel → Quit "Program device" window

Design Environment - Usage

Reference Design - Getting Started

- Install "Quartus Prime Lite Edition Version 20.1.1" or "Quartus Prime Pro Edition Version 20.4" (depending on used FPGA: See https://www.intel.com/content/www/us/en/programmable/downloads/download-center.html)

Create project:

- Run "create_project_win.cmd" or "create_project_linux.sh"

- "<project folder>/settings/desgin_basic_settings.tcl" will be configured automatically

- select your Board in "Board selection" section

- click on "Create project" to generate project for selected board

Manual configuration of the design basic settings:

- Open “<project folder>/settings/design_basic_settings.tcl” with a text editor:

Set correct quartus environment:

Example for quartus lite edition:

QUARTUS_PATH_WIN=C:/intelFPGA_lite (quartus installation path for Win OS)

QUARTUS_PATH_LINUX=~/intelFPGA_lite (quartus installation path for Linux OS)

QUARTUS_VERSION=20.1

QUARTUS_EDITION=Lite

Example for quartus pro edition:

QUARTUS_PATH_WIN=C:/intelFPGA_pro (quartus installation path for Win OS)

QUARTUS_PATH_LINUX=~/intelFPGA_pro (quartus installation path for Linux OS)

QUARTUS_VERSION=20.4

QUARTUS_EDITION=Pro

Software settings are searched in (e.g. for Win OS):

%QUARTUS_PATH_WIN%/%QUARTUS_VERSION%/quartus/

%QUARTUS_PATH_WIN%/%QUARTUS_VERSION%/nios2eds/

Example directory: C:/intelFPGA_pro/20.4/

Attention: Scripts are supported only with predefined quartus version!

Programming FPGA or flash memory:

- General steps:

1. Connect your Hardware-Modul to the PC via JTAG

2. Open create_project_win.cmd/create_project_linux.sh

3. Select correct board in "Board selection"

4. Click on "Program device" button → The "Program device" window opens. - Program with prebuilt files: (download reference design with prebuilt files is required)

4. Select "Program prebuilt file"

5. Click on "Start program device" button - Program with own generated files:

6. Select "Program other file"

7. Click on "Browse ..." to choose path to your own generated file (supported file types: *.jic, *.pof, *.sof, *.elf)

8. Click on "Start program device" button - Program device via Quartus Programmer:

9. Click on "Open quartus programmer"

10. Select from Programmer top menu: Edit → Hardware Setup, select "Arrow-USB-Blaster *" and close window

11. Click on "Add File..." and choose correct programming file

12. Enable "Program/Configure" checkbox and click on "Start" to program the device with the selected programming file

Hardware Design

Device list CSV Description

Device list csv file is used for TE-Scripts only.

| Name | Description | Value |

|---|---|---|

| ID | ID to identify the board variant of the module series, used in TE-Scripts | Number, should be unique in csv list |

| PRODID | Product ID | Product Name |

| FAMILY | FPGA family, used in Quartus and TE-Scripts | device family, which is available in Quartus, ex. MAX 10 |

| DEVICE | FPGA device, used in Quartus and TE-Scripts | device, which is available in Quartus, ex. 10M08SAU169C8G |

| SHORTNAME | Subdirectory name, used for multi board projects to get correct sources and save prebuilt data | name to save prebuilt files or search for sources |

| FLASHTYP | Flash typ used for programming Devices via Quartus/LabTools | "<Flash Name from Quartus>|<SPI Interface>" or "NA" , NA is not defined |

| FLASH_SIZE | Size of Module Flash | use MB, for ex. "64MB" or "NA" if not available |

| DDR_DEV | DDR Module | DDR module name |

| DDR_SIZE | Size of Module DDR | use GB or MB, for ex. "2GB" or "512MB" or "NA" if not available |

| PCB_REV | Supported PCB Revision | "<supported PCB Revision>|<supported PCB Revision>", for ex. "REV02" or "REV03|REV02" |

| NOTES | Additional notes |

SDC Conventions

- All *.sdc from <project folder>/source_files/quartus/ are load into the quartus project on project creation.

Advanced Usage

Attention not all features of the TE-Scripts are supported in the advanced usage!

User defined device list csv file

To modifiy current device csv list, make a copy of the original csv and rename with suffix "_mod.csv", ex.TEI0006_devices.csv as TEI0006_devices_mod.csv. Scripts use modified csv instead of the original file.

User defined Settings

ZIP ignore list:

Files which should not be added in the backup file can be defined in this file: "<project folder>/settings/zip_ignore_list.csv". This file will be loaded automatically on script initialisation.

mod list:

List with commands to modify source files during project creation (<project folder>/settings/mod_list.csv).

apps list:

List with software projects assigned to the correct quartus project and *.sopcinfo file (<project folder>/source_files/software/apps_list.csv).

Qsys preset files:

Predefined settings for Qsys IP Components (<project folder>/source_files/quartus/ip/presets/*.qprs). They will be copied to <project folder>/quartus/ip/presets folder on project creation.

Checklist / Troubleshoot

- Are you using exactly the same Quartus version? If not then the scripts will not work, no need to try.

- Are you using Quartus on Windows PC? Quartus works in Linux also, but the scripts are tested on Windows only.

- Win OS only: Use short path name, OS allows only 256 characters in normal path.

- Linux OS only: Use bash as shell and add access rights to bash files. Check with "ls /bin/sh". It should be display: /bin/sh -> bash. Access rights can be changed with "chmod"

- Are space character on the project path? Somtimes TCL-Scripts can't handle this correctly. Remove spaces from project path.

- Did you have the newest reference design build version? Maybe it's only a bug from a older version.

- On project creation process old files will be deleted. Sometimes the access will be denied by os (synchronisiation problem) and the scripts canceled. Please try again.

- If nothing helps, send a mail to Trenz Electronic Support (support[at]trenz-electronic.de) with subject line "[TE-Reference Designs] ", the complete zip-name from your reference design.

References

- Intel Quartus Prime User Guide: Getting Started (UG-20129)

- Intel Quartus Prime User Guide: Platform Designer (UG-20130)

- Intel Quartus Prime User Guide: Design Compilation (UG-20132)

- Intel Quartus Prime User Guide: Scripting (UG-20144)

Document Change History

To get content of older revision got to "Change History" of this page and select older revision number.

| Date | Revision | Quartus Version | Authors | Description |

|---|---|---|---|---|

Error rendering macro 'page-info' Ambiguous method overloading for method jdk.proxy244.$Proxy3557#hasContentLevelPermission. Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.pages.Page] due to overlapping prototypes between: [interface com.atlassian.confluence.user.ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] [interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] | Error rendering macro 'page-info' Ambiguous method overloading for method jdk.proxy244.$Proxy3557#hasContentLevelPermission. Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.pages.Page] due to overlapping prototypes between: [interface com.atlassian.confluence.user.ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] [interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] | 20.1 Lite 20.4 Pro | Error rendering macro 'page-info' Ambiguous method overloading for method jdk.proxy244.$Proxy3557#hasContentLevelPermission. Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.pages.Page] due to overlapping prototypes between: [interface com.atlassian.confluence.user.ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] [interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] | Work in process ...

|

2020-05-13 | v.9 | 19.1 Lite 19.4 Pro | Thomas Dück |

|

| 2019-11-11 | v.5 | 18.1 | Thomas Dück |

|

| 2019-10-29 | v.4 | 18.1 | Thomas Dück |

|

| All | Error rendering macro 'page-info' Ambiguous method overloading for method jdk.proxy244.$Proxy3557#hasContentLevelPermission.

Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.pages.Page] due to overlapping prototypes between:

[interface com.atlassian.confluence.user.ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject]

[interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] |

Table of contents

- No labels