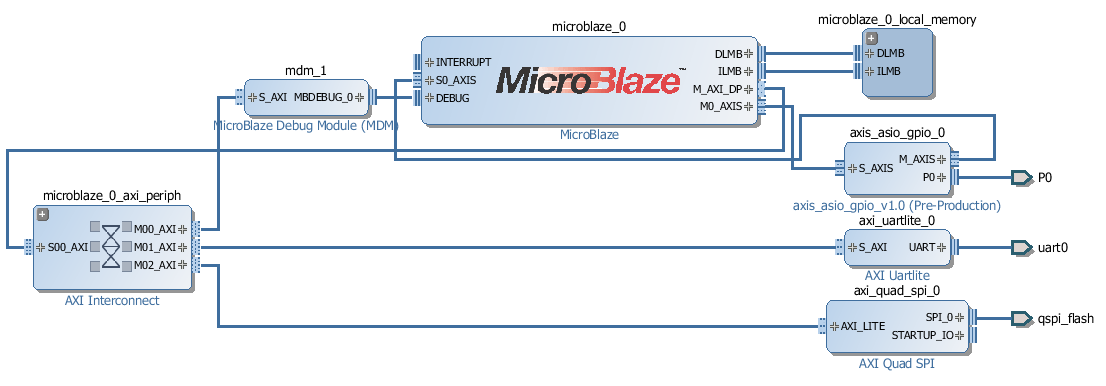

ASIO (A Simple IO) is re-implementation of ASIO IP Cores developed around 2004. ASIO GPIO Demos allocate all FPGA I/O pins that are not used for on-board components except single UART as ASIO I/O - bit addressable GPIO.

Example ASIO Demo for TE0711 SoM: a total of 196 I/O pins are connected to single ASIO GPIO IP Core. All ports are mapped to FPGA pins using Vivado board part flow, no manual constraints entered.

TEST

This design has been tested on following boards (with TE0702 as the carrier board).

Because of the limit structure on the TE0702, some PINs can't be tested.

TE0710-02-35-2CF (104 B2B Pins soll be tested, 100 of them Test completed. These Pins havn't been tested: J2_32, J2_34, J2_36, J2_38 )

TE0710-02-100-2CF (104 B2B Pins soll be tested, 100 of them Test completed. These Pins havn't been tested: J2_32, J2_34, J2_36, J2_38 )

TE0711-01-35-2C (170 B2B Pins soll be tested, all of them the test completed. )

TE0711-01-100-2C (170 B2B Pins soll be tested, all of them the test completed. )

TE0712-01-200-2C (150 B2B Pins soll be tested, 146 of them Test completed. These Pins havn't been tested: J3_47, J3_49, J3_51, J3_53 )

TE0712-01-200-2C (150 B2B Pins soll be tested, 146 of them Test completed. These Pins havn't been tested: J3_47, J3_49, J3_51, J3_53 )

TE0741-02-070-2CF ( 85 B2B Pins soll be tested, 76 of them Test completed. These Pins havn't been tested: J2_29, J2_31, J2_33, J2_35, J2_37, J3_47, J3_49, J3_51, J3_53 )

TE0741-02-160-2CF (135 B2B Pins soll be tested, 131 of them Test completed. These Pins havn't been tested: J3_47, J3_49, J3_51, J3_53 )

TE0741-02-325-2CF (135 B2B Pins soll be tested, 131 of them Test completed. These Pins havn't been tested: J3_47, J3_49, J3_51, J3_53 )

Overview

Content Tools