| The EEPROM switch should be enabled, or these two commands will fail. |

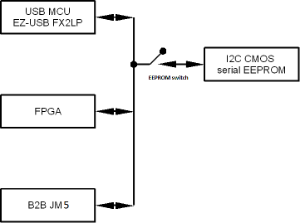

TE USB FX2 module has a flexible IIC (aka I2C) bus on-board as outlined in the figure below.

|

I2C pins on B2B connector J(M)5 cannot be used as GPIOs (general purpose I/Os), as these bus signals are pulled up to 3.3V. |

The I2C signals on the TE USB FX2 module are listed and described in the table below

|

If the FPGA is set to I2C master mode, it can write to or read from serial EEPROM (always slave mode) and B2B connector J(M)5 (attached device set to slave mode).

If the device attached to the I2C port of B2B J(M)5 connector is set to master mode, it can write to or read from serial EEPROM (always slave mode) and FPGA I2C port (set to slave mode).

| The USB FX2 microcontroller can operate just in I2C master mode (default operation). If the user wants to set another device attached to the I2C bus as master device, the USB FX2 microcontroller shall three-state (Z = high impedance) its SCL and SDA pins. |

The I2C bus is typically used by the USB FX2 microcontroller to write USB firmware to the serial EEPROM. In this case, the I2C port of the FPGA must be set in slave mode (SCL pin as input), the device attached to the I2C port of B2B J(M)5 connector must be set to slave mode.

Possible I2C operation modes are summarized in the table below.

|

If the TE USB FX2 module exit from reset or is powered on, the IIC EEPROM content programs/configures the USB FX2 microcontroller RAM |

The user can use CyConsole ("Lg EEPROM") and CyControl ("Program>FX2 64KB EEPROM") or Linux_FUT to directly program (write) the .iic Firmware file into the IIC EEPROM connected to USB FX2 microcontroller.

The user can also use OpenFutNet: if used for firmware recovery boot or firmware update both EEPROM and RAM are programmed (written).

The user can also use fx2loader (see also here) or fxload ( see also here) to directly program (write) the .iic Firmware file into the IIC EEPROM connected to USB FX2 microcontroller.

The firmware actually changes (it runs on USB FX2 microcontroller's RAM) only when

|

It is an implicit (or explicit) step necessary to write a new firmware in the IIC EEPROM. See the section "(Implicit Two-Step) recovery boot and (Explicit Two-Step) recovery boot. |

To default, the FX2 microcontroller hardware (i.e with EEPROM isolated =>hardware's first stage loader) enumerates the USB FX2LP microcontroller chip as VID=0x04B4 (Cypress) and PID=0x8613 (FX2LP), and provides support for loading firmware into RAM. To default, using the FX2 microcontroller hardware (i.e with EEPROM isolated => hardware's first stage loader ) it is possible to write a new firmware in RAM but not in EEPROM. To write a new firmware in FX2 microcontroller's EEPROM, a firmware supporting EEPROM writing should already be running in FX2 microcontroller's RAM (Vend_Ax.hex is normally used). |

The user can use CyConsole ("Options" > "EZ-USB Interface" > "Download" and a .hex or .bix file) or CyControl ("Program FX2 > RAM" and a .hex or .iic file) to directly program the firmware file (.hex, .bix or .iic file) into the USB FX2 microcontroller's RAM.

The user can also use OpenFutNet: if used for Firwmare Recovery Boot or Firmware Upgade both EEPROM and RAM are programmed.

The user can also use fx2loader (see also here) or fxload ( see also here) to directly program the firmware file into the USB FX2 microcontroller's RAM.

| If you don't also write the IIC EEPROM ("Options" > "EZ-USB Interface" > "Lg EEPROM" for CyConsole and "Program>FX2 64KB EEPROM" for CyControl), the new firmware is lost if the TE USB FX2 module goes under reset or power off/on cycle. |

| |||||||||||||||||||||||||||||||||||||||||||||

(1) Reference design: Logical Architecture Layer = Reference Architecture Layer and FX2 firmware= Reference FX2 firmware

(2) MB Commands require the XPS_I2C_SLAVE custom IP block and a proper FX2 interrupt handler (i2c_slave_int_handler() function in interrupt.c) running on MicroBlaze.

MB Commands require the XPS_I2C_SLAVE custom IP block and a proper FX2 interrupt handler (i2c_slave_int_handler() function in interrupt.c running on MicroBlaze); the FX2 interrupt handler is called to handle the signal interrupt xps_i2c_slave_0_IP2INTC_Irpt. The i2c_slave_int_handler() function actually execute the I2C delivered MB Command; when MicroBlaze's software wants to send information to the host computer (through USB FX2 microcontroller), it should write MB2FX2_REGs of XPS_I2C_SLAVE custom IP block. The IP block will rise (USB_INT => INT0) pin INT0 output as a flag. The FX2 microcontroller will manage this flag indication (INT0=1 => FPGA_INT0=1); after this, the FX2 microcontroller could read the registers (MB2FX2_REGs) of XPS_I2C_SLAVE custom IP block.