This demo provides an example on how to use the communication interface provided in the modules firmware to setup the pre-amplification and trigger an ADC measurement. This measurement is converted to show it's value over time, and it's Fast Fourier Transformation / its frequency spectrum.

The download of the demo contains the demo in a separate folder, a folder with setup notebooks, the FPGA Design file and a the related wiki pages in pdf format. The demo consist of two files, one is the notebook which contains the GUI and the other is a code module, containing the functional part of the demo. These files must be in the same folder when running the demo. The modules ADC is controlled via the Intel Max 10 FPGA. In shipment condition, the FPGA is programmed with the necessary FPGA Design to run this demo.

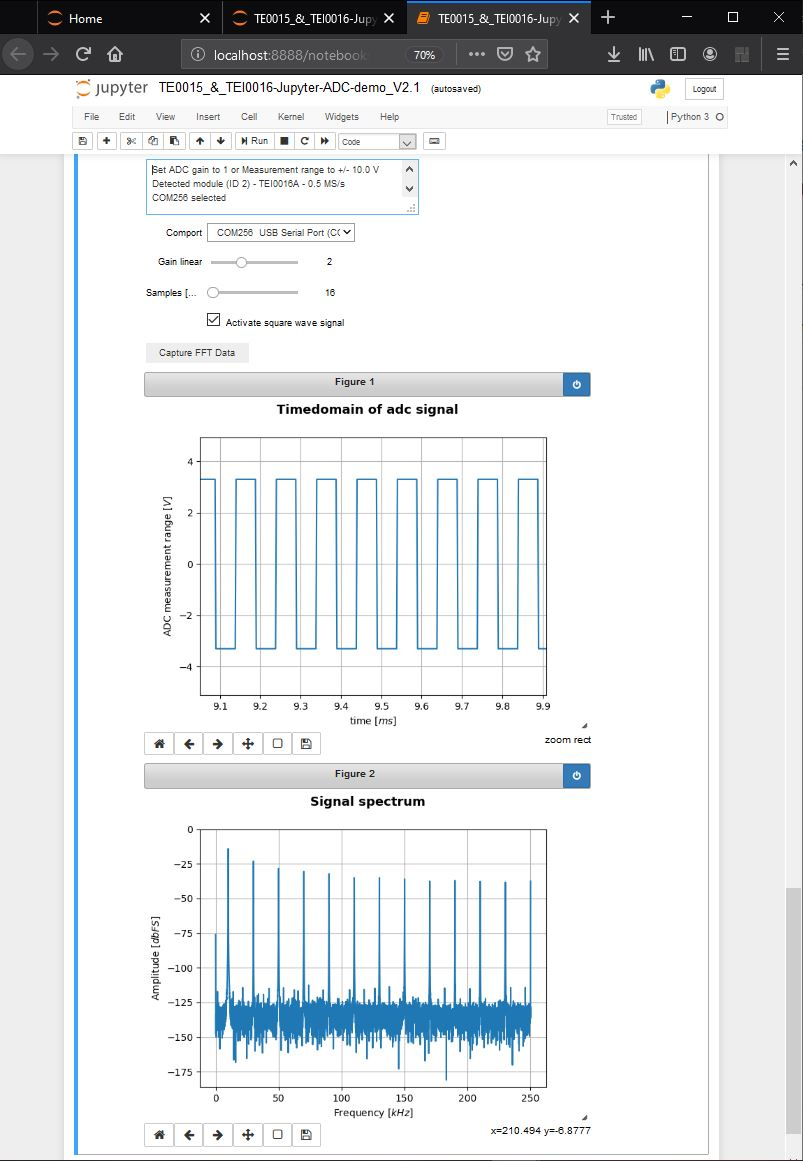

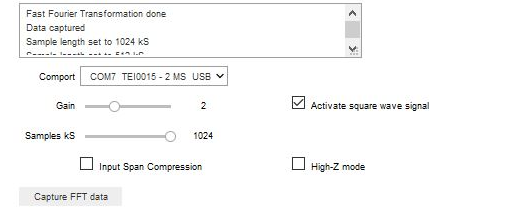

Drop-down List "Comport" :

- COM-port list for selecting a COM-port.

Listed are the port, the modules name and its USB ID

During notebook initialization, ports are scanned

Slider "Gain" :

Select the pre-amplification gain of the module

Different values in dependency to the module

Slider "Samples kS" :

Slider to set the samples to evaluate

Range is from 16 kS to 1024 kS

Check box "Activate square wave signal" :

Activates the modules square wave generator

10 kHz, +3.3V, 50% duty cycle, signal available with and without 180° phase shift

Check box "Input span compression" :

Mode of the modules ADC in which it's reference voltage is reduced to 80% to give head room in case the supply voltage is near to the reference voltage

Not available on all modules, greyed out / deactivated for these modules

Check box "High-Z mode" :

Mode of the modules ADC in which it reduces its current consumption. Not applicable to signal greater then 100 kHz

Not available on all modules, greyed out / deactivated for these modules

Button "Capture FFT data" :

Re-applies the appointed GUI values and features to the module and triggers a signal measurement followed by the data converting and plotting

This demo is designed with the focus of capturing signals. Therefore the module works like a storage oscilloscope. After a trigger event, the module saves 1 million samples of ADC measurement in its SDRAM.

The demo scans for existing comports in its initialisation phase. So the module needs to be connected to the computer prior to running the demo.

When this demo runs, it displays a graphical user interface, setup the comport, the demo automatically selects the module. After this, the demo and the module can communicate.

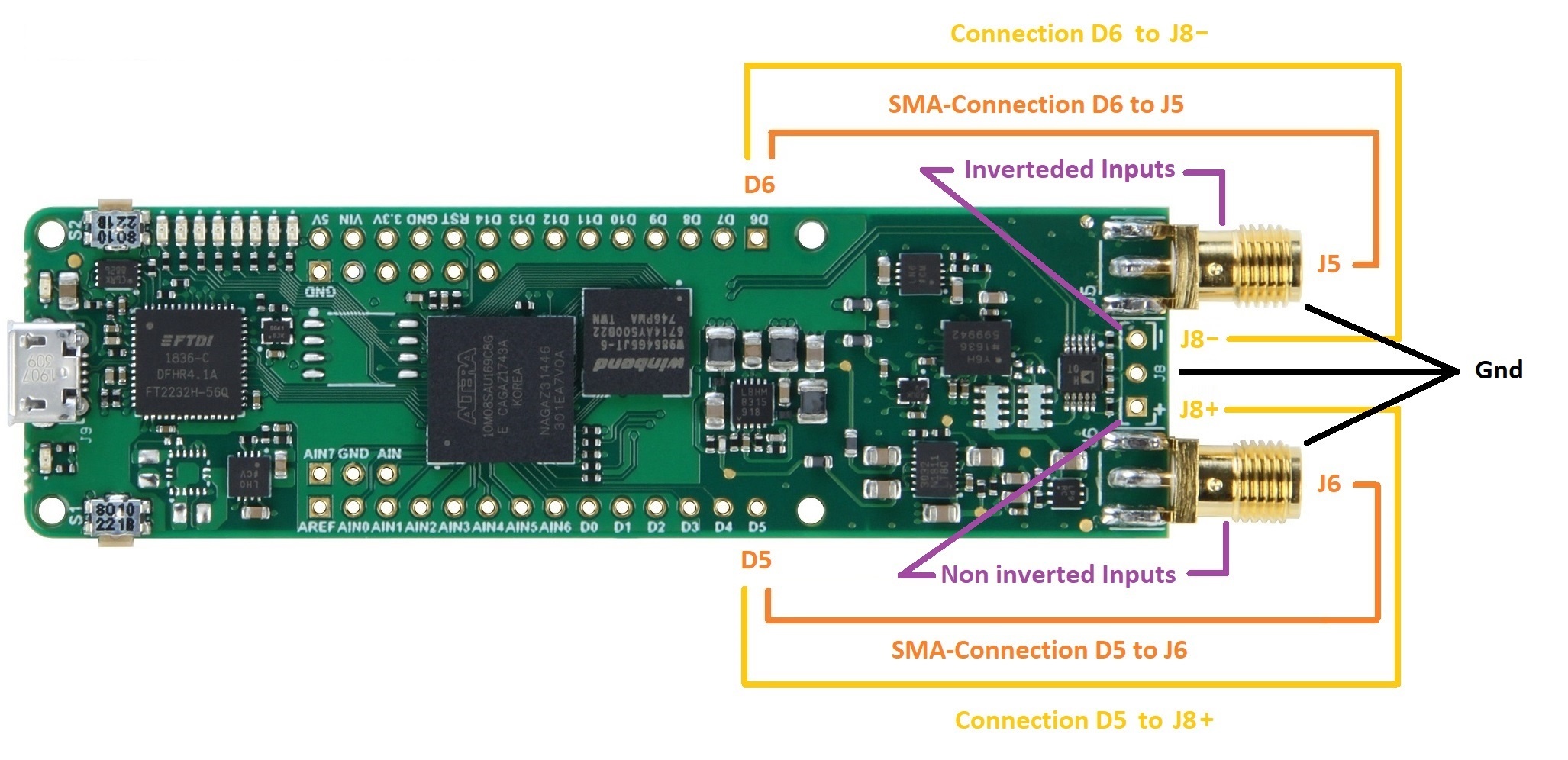

The module offers a Non inverted input and an inverted input. The inputs are accessible through either a SMA connection or a breakout connection.

Inverted inputs are J5 and -J8

Non inverted inputs are J6 and +J8

Now supply a signal to the inputs.

An other option is to use the modules square wave signal output. Connect the digital outputs D5 and D6 to the inputs as you like and activate the signal through the checkbox. Be careful, do not shorten the outputs D5 or D6 to ground.

One can set up a pre amplification gain of the input signal and the amount of samples to be processed. By pressing the button Capture FFT data, the input signal will be plotted and shown.

To communicate with the module, a serial comport port with a speed set to 115200 bits needs to be opened. Commands consists of a single character in UTF-8 encoding. It is good practice to communication with the module following these steps:

These steps apply also for read operations.

The module provides a method to gather highly accurate consecutive ADC measurements in a single event. In this mode of operation, one mega sample of ADC values are performed and stored inside the modules SD-RAM.

The following step should be taken in this mode:

After a trigger event, the one mega sample of data is stored until your retrigger. So processing the data can be done for each chunk individually or the whole one mega sample.

Information to convert the RAW ADC data into standard integer values.

Resolution: 18-bit in 5 nibbles

Maximum sampling rate: 2 MSPS

Order of Values:

| Hex | Dec | Hex | Dec | ||

|---|---|---|---|---|---|

| Mid scale | 0x00000 | 0 | |||

| Positive 1 LSB | 0x00001 | 1 | to full scale -1 LSB | 0x1ffff | 131071 |

| Negative full scale | 0x20000 | 131072 | to -1 LSB | 0x3FFFF | 262143 |

The layout of the ADC circuit is further described in the Analog Devices circuit note CN-0385.

Resolution: 16-bit in 4 nibbles

Maximum sampling rate: 0.5 MSps / 1 MSps

Order of Values:

| Hex | Dec | Hex | Dec | ||

|---|---|---|---|---|---|

| Negative full scale is | 0x0000 | 0 | to -1 LSB | 0x7fff | 32767 |

| Mid scale is | 0x8000 | 32768 | |||

| Positive 1 LSB | 0x8001 | 32769 | to full scale | 0xffff | 65536 |

The layout of the ADC circuit is further described in the Analog Devices circuit note CN-0393.

Resolution: 18-bit in 5 nibbles

Maximum sampling rate: 2 MSPS

Order of Values:

| Hex | Dec | Hex | Dec | ||

|---|---|---|---|---|---|

| Mid scale | 0x00000 | 0 | |||

| Positive 1 LSB | 0x00001 | 1 | to full scale -1 LSB | 0x1ffff | 131071 |

| Negative full scale | 0x20000 | 131072 | to -1 LSB | 0x3FFFF | 262143 |