Template Revision 3.1

Template Change history:

|

Important General Note:

|

----------------------------------------------------------------------- |

Note for Download Link of the Scroll ignore macro:

|

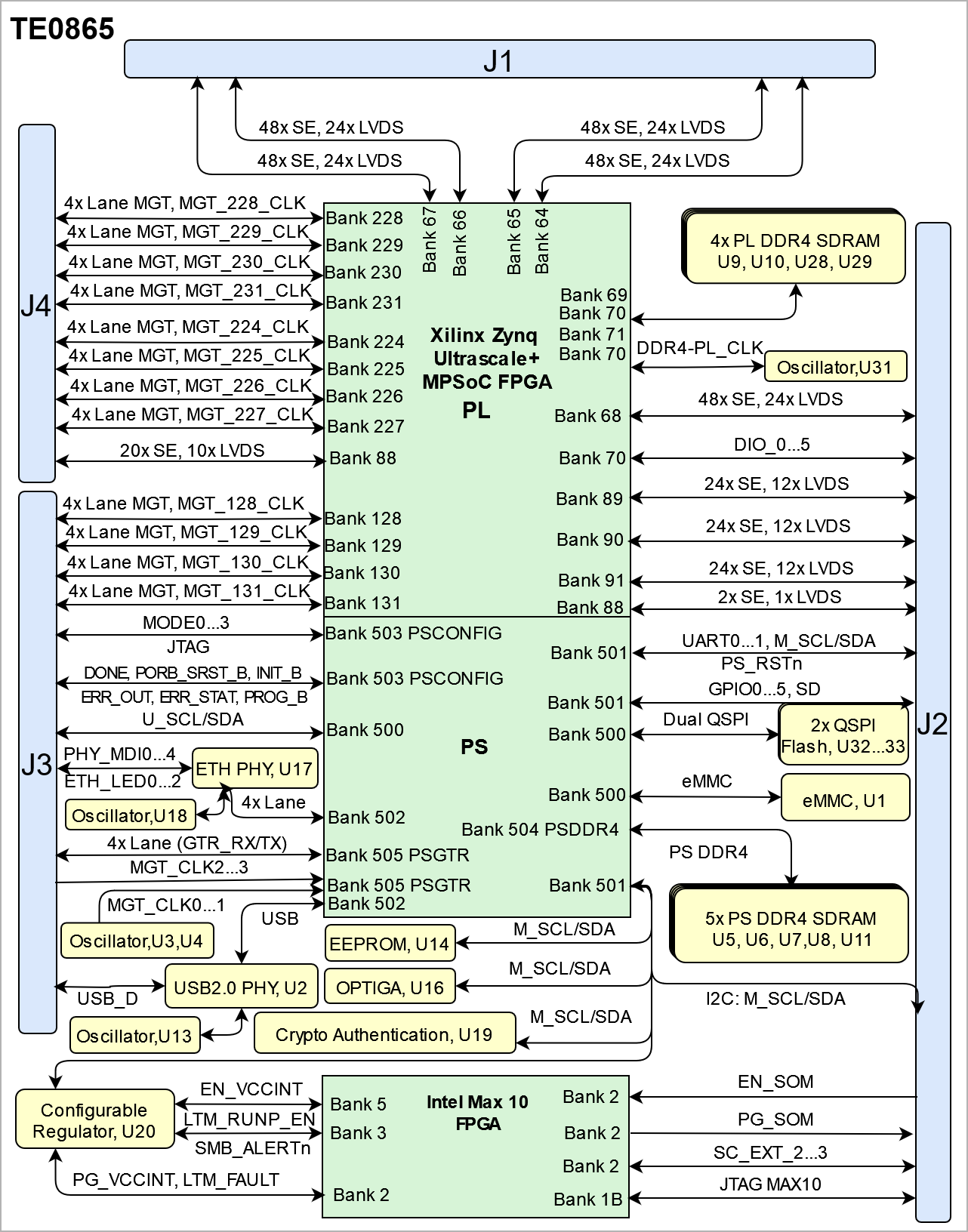

Overview

The Trenz Electronic TE0865 is an industrial/extended grade module based on Xilinx Zunq UltraScale+ MPSoC. The TE0865 is equipped with 4x 2GB DDR4 SDRAM connected to Programmable Logic(PL) and 5x 2GB DDR4 SDRAM connected to Processing System(PS), 8 GB eMMC, 2x 64MB Quad SPI Flash, Gigabit Ethernet Transceiver, USB Transceiver, Ultra micro power terminal and an Intel MAx 10 as system controller CPLD.

Refer to http://trenz.org/te0865-info for the current online version of this manual and other available documentation.

Notes :

|

Key Features

Note: → See examples fro different types <Series Name> TRM Template section examples#%3CSeriesName%3ETRMTemplatesectionexamples-KeyFeatures |

|

Block Diagram

add drawIO object in Scroll Ignore section and add reference image in Scroll Only.

|

|

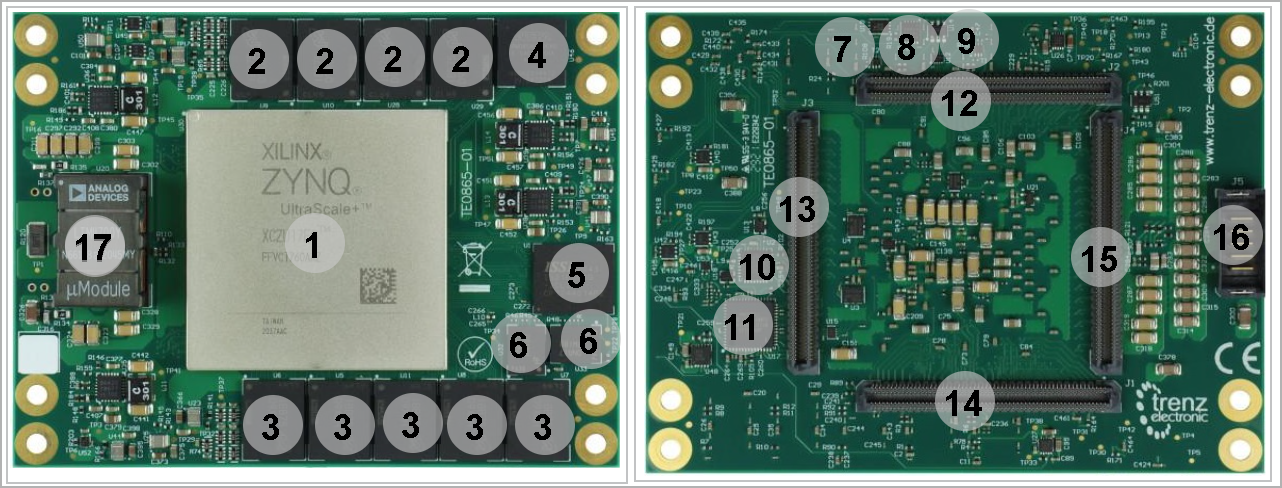

Main Components

Notes :

|

|

- ZYNQ Ultrascale+ MPSoC FPGA, U30

- PL DDR4 SDRAM, U9, U10, U28, U29

- PS DDR4 SDRAM, U5...U8, U11

- Intel MAX 10 FPGA, U46

- eMMC RAM, U1

- Dual QSPI Flash, U32, U33

- Crypto Authentication IC, U19

- OPTIGA Trust M Authentication IC, U16

- EEPROM MAC Address, U14

- USB2.0 Transceiver, U2

- Gigabit Ethernet Transceiver, U17

- B2B Connector, J2

- B2B Connector, J3

- B2B Connector, J1

- B2B Connector, J4

- Power Terminal, J5

Initial Delivery State

|

|

Configuration Signals

|

|

Signals, Interfaces and Pins

For subsection examples see: <Series Name> TRM Template section examples#%3CSeriesName%3ETRMTemplatesectionexamples-Signals,InterfacesandPins

|

B2B SoC/FPGA IOs

B2B JTAG Interface

B2B ETH Interface

B2B USB Interface

SD Card Connector

SMA Connector

MIO

|

MIO Pins

Only for SoC Modules(Xilinx MIO, for Intel and MicroChip SoC please change MIO to syntax of the manufacturer). you must fill the table below with group of MIOs which are connected to a specific components or peripherals, you do not have to specify pins in B2B, Just mention which B2B is connected to MIOs. The rest is clear in the Schematic. MIO Pins are only for SoC like Zynq, U+Zynq and Versal, for other FPGA modules remove this chapter Example:

|

|

Test Points

you must fill the table below with group of Test Point which are indicated as TP in a schematic. If there is no Test Point remarked in the schematic, delet the Test Point section. Example:

|

|

On-board Peripherals

Notes : In the on-board peripheral table "chip/Interface" must be linked to the corresponding chapter or subsection by assigning advance link using: #NameOfTheSection Example: #ClockSources, #CPLD, #QuadSPIFlash |

|

For example subsections see: <Series Name> TRM Template section examples#%3CSeriesName%3ETRMTemplatesectionexamples-On-boardPeripherals |

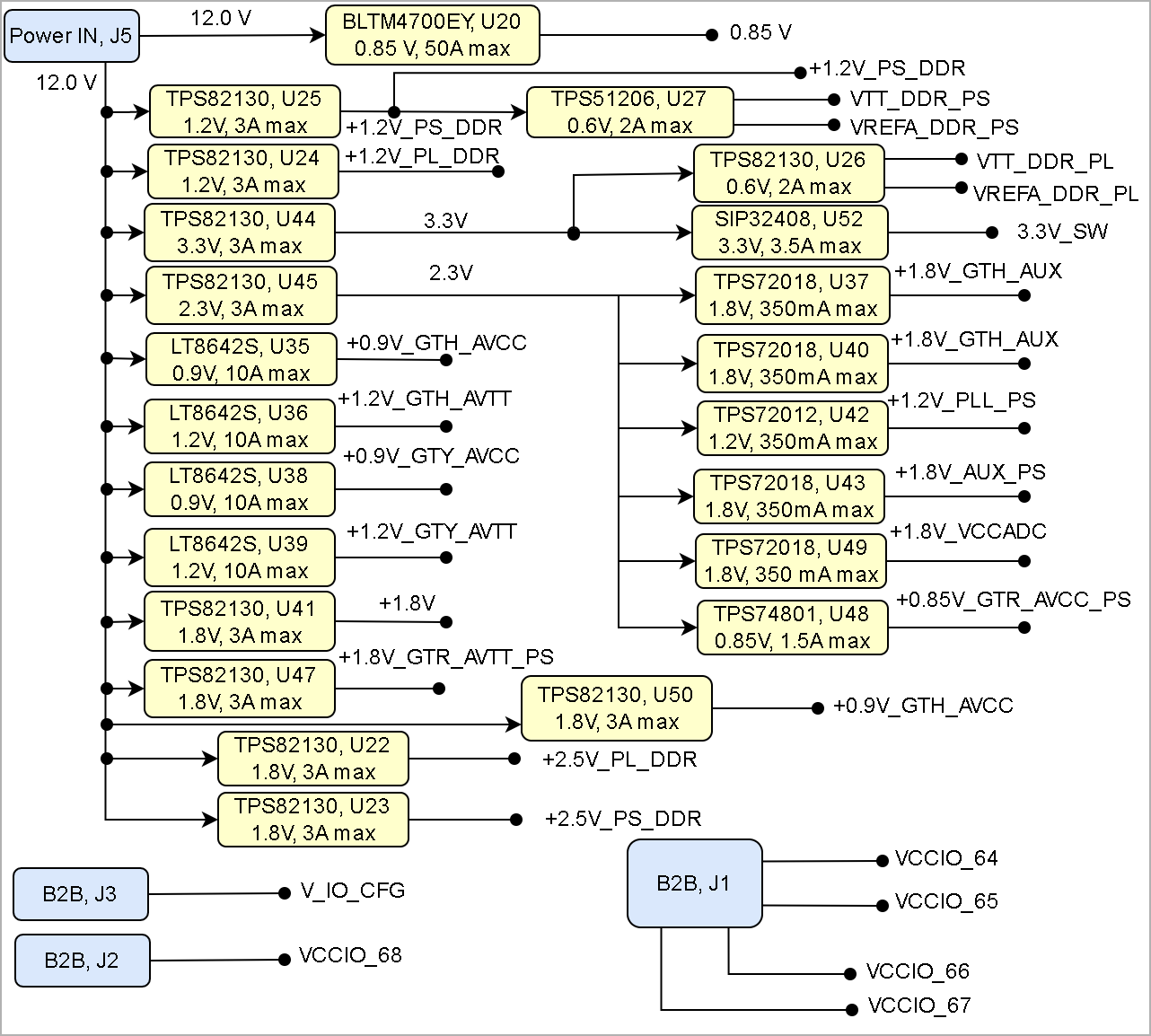

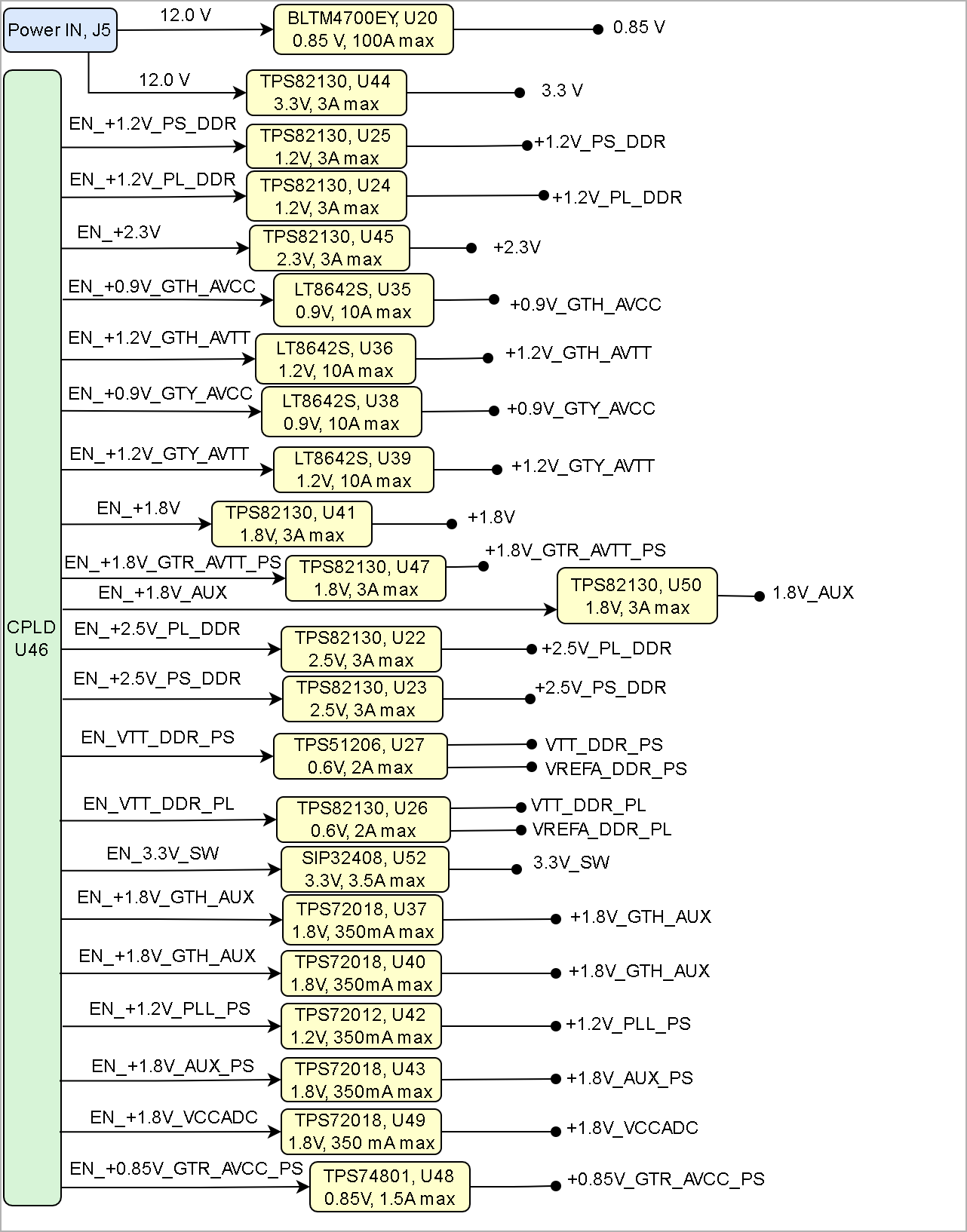

Power and Power-On Sequence

In 'Power and Power-on Sequence' section there are three important digrams which must be drawn:

|

Power Supply

Power supply with minimum current capability of xx A for system startup is recommended.

Power Consumption

|

* TBD - To Be Determined

Power Distribution Dependencies

|

Power-On Sequence

|

Voltage Monitor Circuit

|

Power Rails

|

Bank Voltages

|

Board to Board Connectors

|

Technical Specifications

Absolute Maximum Ratings

|

Recommended Operating Conditions

Operating temperature range depends also on customer design and cooling solution. Please contact us for options.

|

Components are mainly classified in 3 temperature groups, according to range specifications: commercial: 0°C - 75°C extended: 0°C - 85°C industrial: -40°C - 85°C

Classification of the module can be locked up here: Article Number Information i.e.: TE0803-03-5D"I"21-AS (The I indicates industrial)

The actual operation temperature range depends on the FPGA/SoC design/utilization and cooling, as well as other variables. Please note: These are only indications!

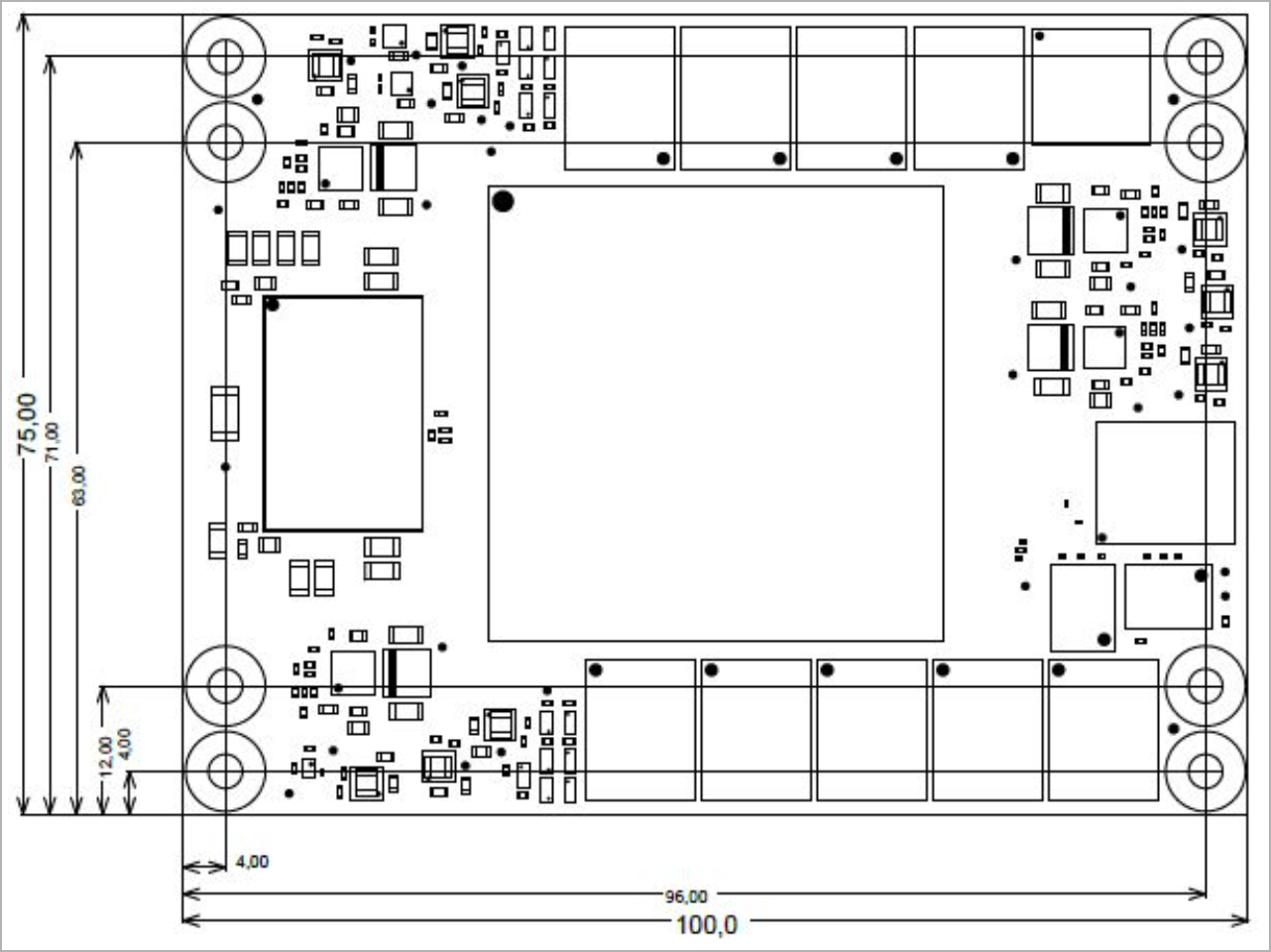

Physical Dimensions

Module size: 75 mm × 100 mm. Please download the assembly diagram for exact numbers.

Mating height with standard connectors: 5 mm.

PCB thickness: 2 mm.

In 'Physical Dimension' section, top and bottom view of module must be inserted, information regarding physical dimensions can be obtained through webpage for product in Shop.Trenz, (Download> Documents> Assembly part) for every SoM. For Example: for Module TE0728, Physical Dimension information can be captured by snipping tools from the link below:

|

|

Currently Offered Variants

Set correct link to the shop page overview table of the product on English and German. Example for TE0706: ENG Page: https://shop.trenz-electronic.de/en/search?sSearch=TE0706 DEU Page: https://shop.trenz-electronic.de/de/search?sSearch=TE0706 |

| ||||

Revision History

Hardware Revision History

Set correct links to download Carrier, e.g. TE0706 REV02: TE0706-02 -> https://shop.trenz-electronic.de/Download/?path=Trenz_Electronic/Modules_and_Module_Carriers/4x5/4x5_Carriers/TE0706/REV02/Documents Note:

|

|

|

Hardware revision number can be found on the PCB board together with the module model number separated by the dash.

Document Change History

|

|

Disclaimer

|

|