Template Revision 1.0 - on construction Design Name always "TE Series Name" + Design name, for example "TE0720 Test Board" |

Important General Note:

|

Overview

Notes :

|

This demo is a Webserver which utilizes SmartFusion2 SoC ARM Cortex-M3, Ethernet, USB / COM-port, Real Time Clock and the on-board LEDs.

The demo is offered in two variants, one which is stored into the embedded non-volatile memory (eNVM) and the seconde one which stored to the external DDR3/L SDRAM memory and therefore volatile.

Refer to http://trenz.org/tem0005-info for the current online version of this manual and other available documentation.

Key Features

Notes :

|

|

Revision History

Notes :

|

|

Release Notes and Know Issues

Notes :

|

|

Requirements

Software

Notes :

|

|

Hardware

Notes :

|

Design supports following modules:

|

Additional hardware Requirements:

|

Content

Notes :

|

Content of the zip archive "TEM0005-01-010C_ReferenceDesigns01_LibXY.Z-SCX.Y_Date-Time":

Design Sources

|

Download

The Trenz Electronic Reference Designs and Demos are usable with the specified Microsemi Libero / SoftConsole version. Usage of a different Microsemi Libero / SoftConsole software versions is not recommended.

|

Reference Designs / Demos are available via the following link:

The download is a ZIP compressed archive. Extract the archive before usage.

Design Flow

Notes :

|

The Hardware and Software Reference / Demo -Designs Projects are available as a prebuild zip archive. The archive contains a Libero Hardware Project and a SoftConsole Workspace folder, they were created and tested in windows environment.

This SoftConsole Workspace contains the Software Projects Webserver, Hello World and SoC erase flash. The board configuration file "microsemi-smartfusion2-smartberry-ddr.cfg" which is required for the usage of the Software projects via the IDE SoftConsole.

Launch

Note:

|

Executing a Reference / Demo Design on a module requires the powering of it and a JTAG or UART Connection for Programming and Communication. Often the programming is a two fold process, where the first programming configures the FPGA and the second programming flashes Software code to be executed inside the FPGA / ARM processor.

Connecting

Connect the carriers micro USB connector to your host pc and power it via barrel connector (5 V, plus pole inside), this powers the module and a simultaneous JTAG and UART connection is possible.

Only necessary for running the Demo Webserver:

The demo is configured to establish a network connection via the DHCP protocol, therefore, if a a free router port is used, no further port setup is required.

If a "direct Ethernet Connection" between Host PC and module is used, the user must know how to setup this connection type. Further down in this chapter is explained how to setup the Demo Webserver and recompile it, so that it uses a static IP.

Driver check

When the module is connected via USB cable to your demo host computer, in the Windows Device Manager appear the following tree board driver related devices:

In section Ports (COM & LPT):

- FlashPro5 Port (ComX)

In section Universal Serial Bus controllers:

- USB FP5 Serial Converter A

- USB FP5 Serial Converter B

The Device Manager is accessible via "Right mouse click context menu" from the Windows Start Menu Button. When these devices are not visible, the driver installation through libero could be faulty.

Programming the Hardware design

Via Libero

Programming of the Hardware reference Design requires to open the FPGA Design IDE Libero.

|

The Hardware Reference Design can be opened via "Project > Open Project" in the top right corner of Libero (picture above - upper green rectangle). A file dialogue opens, point the dialogue along the extracted download to the folder containing the Hardware Reference Design.

Disk :\ Path-to-the-demo-archive \ Extracted ZIP-archive \ Libero-RefDesign_vXY\

Double left mouse click onto the project file "Referenz-Design_XY .prjx" to open it. The board is automatically selected and setup to be flashed by Libero.

In the upper left section of Libero, select the tab "Design Flow" (picture above - lover green rectangle) and flash it to the board via "Program Design > and double left mouse click onto "Run PROGRAM Action" (picture above - row with blue background).

Warnings should not affect the functionality of a Reference / Demo -Design.

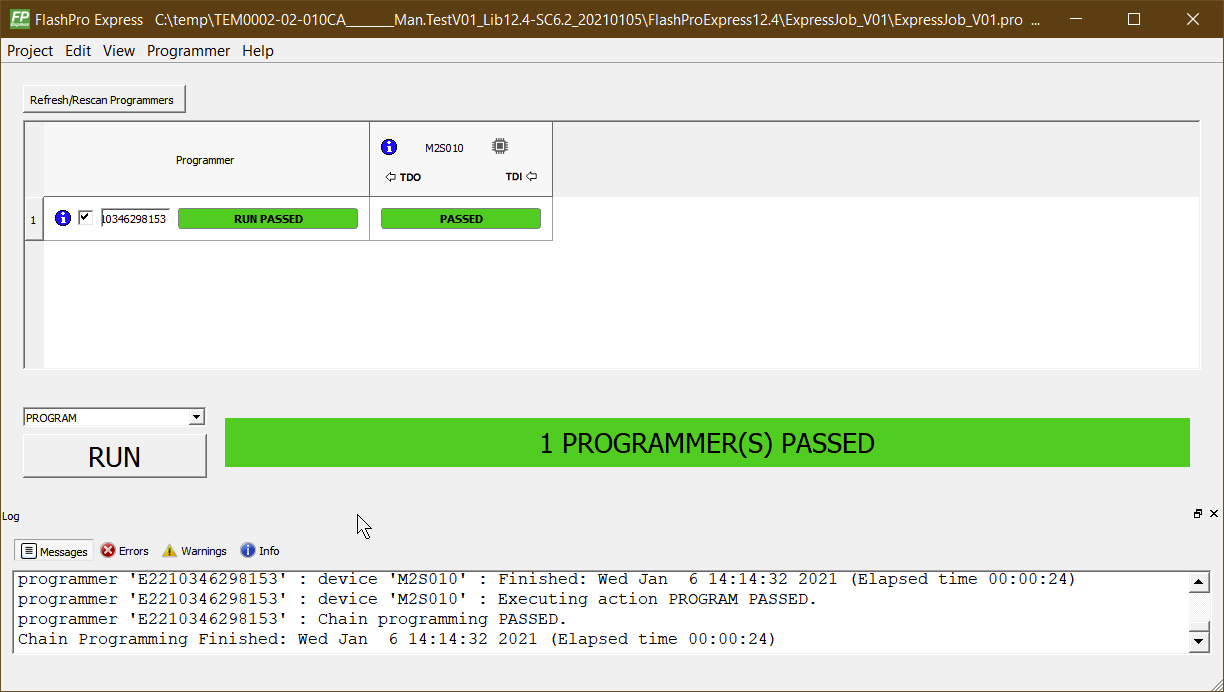

Via FlashPro Express

Open "FlashPro Express", to the left, in section "Job Project", click on "Open..." .

In the appearing file dialogue, point to the projects "Programming job file (.pro-file)" and confirm.

The programm windows changes through opening the file. Now click "Refresh/Rescan Programmers", wait untill the scan is finished.

Click "RUN" to programm the module.

When the programming is done, you can close FlashPro Express.

UART connection

Before flashing any Software Project to the module, open a comport terminal to the boards comport, so that it's messages can be captured.

Programming a Software project

Open SoftConsole and press "Browse..." near the right edge. A file dialogue opens, point the dialogue along the extracted download to the folder containing the SoftConsole Workspace.

Disk :\ Path-to-the-demo-archive \ Extracted ZIP-archive \ SC-Workspace \

Confirm your selection by pressing "Ok" , the dialogue closes, and open The SoftConsole by pressing "Launch"

|

Subsequently the program opens and shows the software project's which are contained inside the workspace. The projects and their files can be accessed in the section "Project Explorer".

|

To simply run a Project, press the triangle right to the button marked with a "R" in the picture above and select a demo.

Pressing the triangle next to the button marked with "D" let you select which variant to be executed in debug mode.

Debug controls - Resume - Pause - Stop

Switch between Debug and Run perspective (upper right corner program window)

|

System Design - Libero

Note:

|

Smart Design

|

Constrains

IO constrains

# Microsemi I/O Physical Design Constraints file

# User I/O Constraints file

# Version: v12.4 12.900.0.16

# Family: SmartFusion2 , Die: M2S010 , Package: 400 VF

# Date generated: Wed May 26 09:19:42 2021

#

# User Locked I/O Bank Settings

#

#

# Unlocked I/O Bank Settings

# The I/O Bank Settings can be locked by directly editing this file

# or by making changes in the I/O Attribute Editor

#

#

# User Locked I/O settings

#

set_io CLK0_PAD \

-pinname Y12 \

-fixed yes \

-DIRECTION INPUT

set_io ETH_COL \

-pinname D2 \

-fixed yes \

-DIRECTION INPUT

set_io ETH_CRS \

-pinname E3 \

-fixed yes \

-DIRECTION INPUT

set_io ETH_MDC \

-pinname F3 \

-fixed yes \

-DIRECTION OUTPUT

set_io ETH_MDIO \

-pinname F4 \

-fixed yes \

-DIRECTION INOUT

set_io ETH_RST \

-pinname H6 \

-fixed yes \

-DIRECTION OUTPUT

set_io ETH_RXC \

-pinname G1 \

-fixed yes \

-DIRECTION INPUT

set_io ETH_RXDV \

-pinname E1 \

-fixed yes \

-DIRECTION INPUT

set_io {ETH_RXD[0]} \

-pinname J7 \

-fixed yes \

-DIRECTION INPUT

set_io {ETH_RXD[1]} \

-pinname F1 \

-fixed yes \

-DIRECTION INPUT

set_io {ETH_RXD[2]} \

-pinname H5 \

-fixed yes \

-DIRECTION INPUT

set_io {ETH_RXD[3]} \

-pinname H4 \

-fixed yes \

-DIRECTION INPUT

set_io ETH_RXER \

-pinname E2 \

-fixed yes \

-DIRECTION INPUT

set_io ETH_TXC \

-pinname G2 \

-fixed yes \

-DIRECTION INPUT

set_io {ETH_TXD[0]} \

-pinname G4 \

-fixed yes \

-DIRECTION OUTPUT

set_io {ETH_TXD[1]} \

-pinname F5 \

-fixed yes \

-DIRECTION OUTPUT

set_io {ETH_TXD[2]} \

-pinname G6 \

-fixed yes \

-DIRECTION OUTPUT

set_io {ETH_TXD[3]} \

-pinname F7 \

-fixed yes \

-DIRECTION OUTPUT

set_io ETH_TX_EN \

-pinname G3 \

-fixed yes \

-DIRECTION OUTPUT

set_io LED3_Y13 \

-pinname Y13 \

-fixed yes \

-DIRECTION OUTPUT

set_io LED4_Y10 \

-pinname Y10 \

-fixed yes \

-DIRECTION OUTPUT

set_io TASTER_C19 \

-pinname C19 \

-fixed yes \

-DIRECTION INPUT

set_io U6_EN_VADJ_N20 \

-pinname N20 \

-fixed yes \

-DIRECTION OUTPUT

set_io U6_SEL_VADJ_R15 \

-pinname R15 \

-fixed yes \

-DIRECTION OUTPUT

#

# Dedicated Peripheral I/O Settings

#

#

# Unlocked I/O settings

# The I/Os in this section are unplaced or placed but are not locked

# the other listed attributes have been applied

#

#

#Ports using Dedicated Pins

#

set_io DEVRST_N \

-pinname U17 \

-DIRECTION INPUT

set_io XTL \

-pinname Y18 \

-DIRECTION INPUT

|

Clock constrains

create_clock -name {XTAL_12MHz} -period 83.3333 -waveform {0 41.6667 } [ get_ports { XTL } ]

create_clock -name {Clk0pad_30MHz_Y12} -period 33.3333 -waveform {0 16.6667 } [ get_ports { CLK0_PAD } ]

create_clock -name {SoC_sb_0___SoC_sb_MSS_0___FIC_2_APB_M_PCLK} -period 10 -waveform {0 5 } [ get_nets { SoC_sb_0/SoC_sb_MSS_0/FIC_2_APB_M_PCLK } ]

create_clock -name {SoC_sb_0___FABOSC_0___N_RCOSC_25_50MHZ_CLKOUT} -period 10 -waveform {0 5 } [ get_nets { SoC_sb_0/FABOSC_0/N_RCOSC_25_50MHZ_CLKOUT } ]

create_clock -name {MAC_RXC_TXC} -period 40 -waveform {0 20 } [ get_ports { ETH_RXC ETH_TXC } ]

create_clock -name {SoC_sb_0___CCC_0___GL0} -period 10000 -waveform {0 5000 } [ get_nets { SoC_sb_0/CCC_0/GL0_net } ]

create_clock -name {FCCC_C0_FCCC_C0_0_FCCC___GL0_net_inferred_clock} -period 10000 -waveform {0 5000 } [ get_pins { FCCC_C0_0/FCCC_C0_0/CCC_INST/GL0 } ]

|

Software Design - SoftConsole

Note:

|

---------------------------------------------------------- FPGA Example HEADING: scu MCS Firmware to configure SI5338 and Reset System. HEADING: srec_spi_bootloader TE modified 2019.2 SREC Bootloader to load app or second bootloader from flash into DDR Descriptions:

HEADING: xilisf_v5_11 TE modified 2019.2 xilisf_v5_11

---------------------------------------------------------- Zynq Example: HEADING: zynq_fsbl TE modified 2019.2 FSBL General:

Module Specific:

HEADING: zynq_fsbl_flash TE modified 2019.2 FSBL General:

ZynqMP Example: ---------------------------------------------------------- HEADING: zynqmp_fsbl TE modified 2019.2 FSBL General:

Module Specific:

HEADING: zynqmp_fsbl_flash TE modified 2019.2 FSBL General:

HEADING: zynqmp_pmufw Xilinx default PMU firmware. ---------------------------------------------------------- General Example: HEADING: hello_te0820 Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output. HEADING: u-boot U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin. |

Applications

Webserver

The demo projects "Webserver_DHCP" and "Webserver_DDR_STATIC" are identical variants of the demo, they only differ in their memory location:

- Webserver_DHCP - Application code is stored to the FPGA's embedded non-volatile memory (eNVM)

- Webserver_DDR_STATIC - Application code is stored to the FPGA's external volatile memory (DDR3 RAM) and lost during power down or reset

Initialization UART messages after programming:

|

Webpage in the browser:

|

Static IP configuration

To change IP and Gateway Address of the project Webserver_DDR_STATIC, open the project in SoftConsole. Open the file main_WebServer_DDR_Static and scroll to line 253. Change the addresses to your needs.

|

Disengage the DHCP service

To disengaging the DHCP mode one has to setup up an IP and Gateway Address in the code, this is discribed in the chapter above. Alternativly, the demo hosts IP Address can be changed.

Furthermore the corresponding compiler flag needs to be deleted in the project setting. To do so, in the "Project Explorer" tab, right mouse click onto the project and select Properties in the appearing menu.

|

In the left section of the properties window select "C/C++ Build > Settings" in the right section select the tab "Tool Settings > GNU ARM Cross C Compiler > Preprocessor" under "Defined symbols (-D)" delete the compiler flag "NET_USE_DHCP" and press "Apply". Confirm the following dialogue and press "Cancel".

Lastly, the project needs to be recompiled. In the top menu of the SoftConsole select "Project > Build ALL / Build Project".

Warnings should not affect the demo and can be ignored.

HelloWorld

Hello World example as endless loop. Each loop contains the updated current loop and RTC/system time.

The user LED's are continuously blinking. The user buttons responds with a message at any time.

UART output:

|

SoC-erase

The SoC's embedded non-volatile memory (eNVM) can only be erased from within.

|

Appx. A: Change History and Legal Notices

Document Change History

To get content of older revision got to "Change History" of this page and select older document revision number.

|

|

Legal Notices

|