Design Name is always "TE Series Name" + Design name, for example "TE0720 Test Board"

|

Important General Note:

|

Overview

Notes :

|

Refer to http://trenz.org/te0717-info for the current online version of this manual and other available documentation.

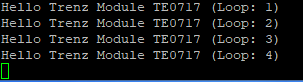

This example showcases a simple MicroBlaze Design that executes in an endless loop letting the red LED blink and prints "Hello Trenz Module TE0717" via UART for 10 minutes.

Key Features

Notes :

|

|

Revision History

Notes :

|

|

Release Notes and Know Issues

Notes :

|

|

Requirements

Software

Notes :

|

|

Hardware

Notes :

|

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on "<project folder>\board_files\*_board_files.csv"

Design supports following modules:

*used as reference |

Design supports following carriers:

*used as reference |

Additional HW Requirements:

*used as reference |

Content

Notes :

|

For general structure and usage of the reference design, see Project Delivery - AMD devices

Design Sources

|

Additional Sources

|

Prebuilt

Notes :

|

|

Download

Reference Design is only usable with the specified Vivado/Vitis/PetaLinux version. Do never use different Versions of Xilinx Software for the same Project.

|

Reference Design is available on:

Design Flow

Notes :

|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first launch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

- Xilinx Development Tools#XilinxSoftware-BasicUserGuides

- Vivado Projects - TE Reference Design

- Project Delivery.

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/Vitis GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

Caution! Win OS has a 260 character limit for path lengths which can affect the Vivado tools. To avoid this issue, use Virtual Drive or the shortest possible names and directory locations for the reference design (for example "x:\<project folder>") |

Run _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

------------------------Set design paths---------------------------- -- Run Design with: _create_win_setup -- Use Design Path: <absolute project path> -------------------------------------------------------------------- -------------------------TE Reference Design--------------------------- -------------------------------------------------------------------- -- (0) Module selection guide, project creation...prebuilt export... -- (1) Create minimum setup of CMD-Files and exit Batch -- (2) Create maximum setup of CMD-Files and exit Batch -- (3) (internal only) Dev -- (4) (internal only) Prod -- (c) Go to CMD-File Generation (Manual setup) -- (d) Go to Documentation (Web Documentation) -- (g) Install Board Files from Xilinx Board Store (beta) -- (a) Start design with unsupported Vivado Version (beta) -- (x) Exit Batch (nothing is done!) ---- Select (ex.:'0' for module selection guide):

- Press 0 and enter to start "Module Selection Guide"

- Create project and follow instructions of the product selection guide, settings file will be configured automatically during this process.

optional for manual changes: Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see also Vivado Board Part Flow

Create hardware description file (.xsa file) and export to prebuilt folder

TE::hw_build_design -export_prebuilt

Using Vivado GUI is the same, except file export to prebuilt folder.

- Generate Programming Files with Vitis

Run on Vivado TCL:

TE::sw_run_vitis -all

- Copy "\prebuilt\software\<short name>\hello_te0717.elf" into "\firmware\microblaze_0\"

- Regenerate Vivado Project or Update Bitfile only, with new "hello_te0717.elf"

TCL scripts generate also platform project, this must be done manually in case GUI is used. See Vitis

Launch

Note:

|

Programming

Check Module and Carrier TRMs for proper HW configuration before you try any design. Reference Design is also available with prebuilt files. It's recommended to use TE prebuilt files for first launch. |

Xilinx documentation for programming and debugging: Vivado/Vitis/SDSoC-Xilinx Software Programming and Debugging

Get prebuilt boot binaries

- Run _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell

- Press 0 and enter to start "Module Selection Guide"

- Select assembly version

- Validate selection

Select create and open delivery binary folder

Note: Folder "<project folder>\_binaries_<Article Name>" with subfolder "boot_<app name>" for different applications will be generated

QSPI-Boot mode

- Connect JTAG and power on carrier with module

Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

TE::pr_program_flash -swapp hello_te0717

- Press the reset button to start the application and see the output in the console

JTAG

- Connect JTAG and power on PCB

- Open Vivado HW Manager

- Program FPGA with Bitfile from "prebuilt\hardware\<short dir>\"

Usage

- Prepare HW like described on section Programming

- Connect UART USB (most cases same as JTAG)

Select QSPI as Boot Mode

Note: See TRM of the Carrier, which is used.

Power On PCB

1. FPGA Loads Bitfile(spi bootloader included) from Flash

2. The spi bootloader loads the hello_te0717.elf application from address 0x005e0000 to RAM

3. Hello Trenz will be run on UART console for 10 minutes.

info: Do not reboot, if Bitfile programming over JTAG is used as programming method.

UART

Open Serial Console (e.g. putty)

- Speed: 9600

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

This step depends on Xilinx Device/Hardware

for Zynq-7000 series

1. Zynq Boot ROM loads FSBL from SD/QSPI into OCM,

2. FSBL init the PS, programs the PL using the bitstream and loads U-boot from SD/QSPI into DDR,

3. U-boot loads Linux (image.ub) from SD/QSPI/... into DDR

for ZynqMP???

1. ZynqMP Boot ROM loads FSBL from SD/QSPI into OCM,

2. FSBL init the PS, programs the PL using the bitstream and loads PMU, ATF and U-boot from SD/QSPI into DDR,

3. U-boot loads Linux (image.ub) from SD/QSPI/... into DDR

for Microblaze with Linux

1. FPGA Loads Bitfile from Flash,

2. MCS Firmware configure SI5338 and starts Microblaze, (only if mcs is available)

3. SREC Bootloader from Bitfile Firmware loads U-Boot into DDR (This takes a while),

4. U-boot loads Linux from QSPI Flash into DDR

for native FPGA

...

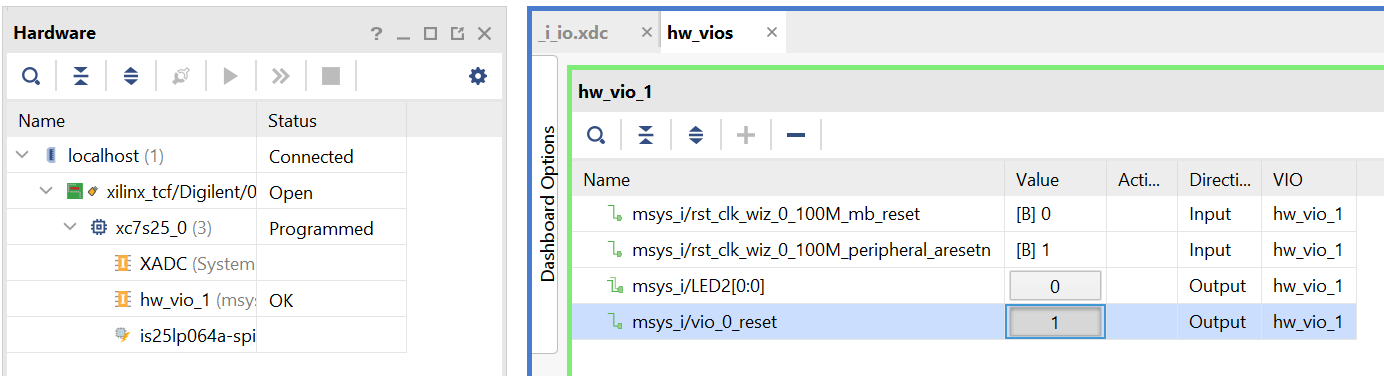

Vivado HW Manager

Note:

|

Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder)

- Control:

- LED2 (green LED)

- reset MicroBlaze (active low)

- Monitoring:

- Reset of Periphery and MicroBlaze

|

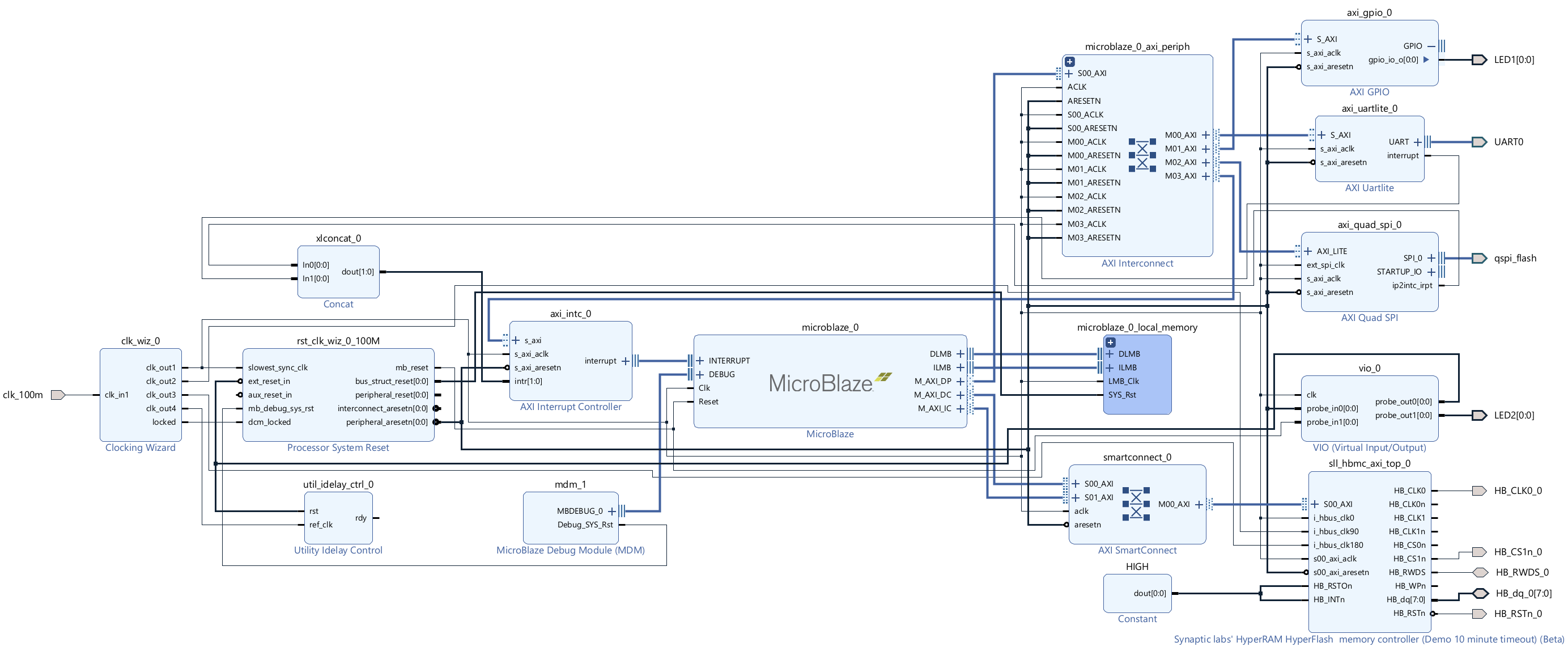

System Design - Vivado

Note:

|

Block Design

|

Constraints

Basic module constraints

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design] set_property BITSTREAM.CONFIG.CONFIGRATE 66 [current_design] set_property CONFIG_VOLTAGE 3.3 [current_design] set_property CFGBVS VCCO [current_design] set_property CONFIG_MODE SPIx4 [current_design] set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR YES [current_design] set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design] set_property BITSTREAM.CONFIG.M1PIN PULLNONE [current_design] set_property BITSTREAM.CONFIG.M2PIN PULLNONE [current_design] set_property BITSTREAM.CONFIG.M0PIN PULLNONE [current_design] set_property BITSTREAM.CONFIG.USR_ACCESS TIMESTAMP [current_design] |

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLDOWN [current_design] # # # |

Design specific constraints

set_property PACKAGE_PIN G11 [get_ports clk_100m]

set_property IOSTANDARD LVCMOS33 [get_ports clk_100m]

set_property IOSTANDARD LVCMOS33 [get_ports {LED1[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED2[0]}]

set_property PACKAGE_PIN D14 [get_ports {LED1[0]}]

set_property PACKAGE_PIN C14 [get_ports {LED2[0]}] |

set_property PACKAGE_PIN F13 [get_ports HB_CLK0_0]

#set_property PACKAGE_PIN A14 [get_ports HB_CLK0n_0]

set_property PACKAGE_PIN A13 [get_ports {HB_dq_0[0]}]

set_property PACKAGE_PIN B13 [get_ports {HB_dq_0[1]}]

set_property PACKAGE_PIN D12 [get_ports {HB_dq_0[2]}]

set_property PACKAGE_PIN D13 [get_ports {HB_dq_0[3]}]

set_property PACKAGE_PIN A12 [get_ports {HB_dq_0[4]}]

set_property PACKAGE_PIN G14 [get_ports {HB_dq_0[5]}]

set_property PACKAGE_PIN F14 [get_ports {HB_dq_0[6]}]

set_property PACKAGE_PIN B14 [get_ports {HB_dq_0[7]}]

set_property PACKAGE_PIN E13 [get_ports HB_RWDS_0]

set_property PACKAGE_PIN E12 [get_ports HB_CS1n_0]

set_property PACKAGE_PIN F12 [get_ports HB_RSTn_0]

#set_property PACKAGE_PIN A18 [get_ports HB_CS0n_0 ]

#set_property PACKAGE_PIN J18 [get_ports HB_INTn_0 ]

#set_property PACKAGE_PIN C17 [get_ports HB_RSTOn_0]

#

# FPGA Pin Voltage assignment

#

set_property IOSTANDARD LVCMOS33 [get_ports HB_CLK0_0]

#set_property IOSTANDARD LVCMOS33 [get_ports HB_CLK0n_0]

set_property IOSTANDARD LVCMOS33 [get_ports {HB_dq_0[*]}]

set_property IOSTANDARD LVCMOS33 [get_ports HB_CS1n_0]

set_property IOSTANDARD LVCMOS33 [get_ports HB_RSTn_0]

set_property IOSTANDARD LVCMOS33 [get_ports HB_RWDS_0]

#set_property IOSTANDARD LVCMOS18 [get_ports HB_CS0n_0]

#set_property IOSTANDARD LVCMOS18 [get_ports HB_INTn_0]

#set_property IOSTANDARD LVCMOS18 [get_ports HB_RSTOn_0]

#set_property PULLUP true [get_ports HB_RSTOn_0]

#set_property PULLUP true [get_ports HB_INTn_0]

#

#Hyperbus Clock - change according to clk pin on PLL

#

#create_generated_clock -name clk_0 -source [get_pins msys_i/clk_wiz_0/inst/mmcm_adv_inst/CLKIN1] -master_clock clk_100m [get_pins msys_i/clk_wiz_0/inst/mmcm_adv_inst/CLKOUT0]

#create_generated_clock -name clk_90 -source [get_pins msys_i/clk_wiz_0/inst/mmcm_adv_inst/CLKIN1] -master_clock clk_100m [get_pins msys_i/clk_wiz_0/inst/mmcm_adv_inst/CLKOUT1]

#create_generated_clock -name clk_180 -source [get_pins msys_i/clk_wiz_0/inst/mmcm_adv_inst/CLKIN1] -master_clock clk_100m [get_pins msys_i/clk_wiz_0/inst/mmcm_adv_inst/CLKOUT2]

#

#100Mhz clock freqeuncy - change accordingly

#

set hbus_freq_ns 10

set dqs_in_min_dly -0.5

set dqs_in_max_dly 0.5

set HB_dq_ports [get_ports HB_dq_0[*]]

#

#Create RDS clock and RDS virtual clock

#

create_clock -period $hbus_freq_ns -name rwds_clk [get_ports HB_RWDS_0]

create_clock -period $hbus_freq_ns -name virt_rwds_clk

#

#Input Delay Constraint - HB_RWDS-HB_DQ

#

set_input_delay -clock [get_clocks virt_rwds_clk] -max ${dqs_in_max_dly} ${HB_dq_ports}

set_input_delay -clock [get_clocks virt_rwds_clk] -clock_fall -max ${dqs_in_max_dly} ${HB_dq_ports} -add_delay

set_input_delay -clock [get_clocks virt_rwds_clk] -min ${dqs_in_min_dly} ${HB_dq_ports} -add_delay

set_input_delay -clock [get_clocks virt_rwds_clk] -clock_fall -min ${dqs_in_min_dly} ${HB_dq_ports} -add_delay

set_multicycle_path -setup -end -rise_from [get_clocks virt_rwds_clk] -rise_to [get_clocks rwds_clk] 0

set_multicycle_path -setup -end -fall_from [get_clocks virt_rwds_clk] -fall_to [get_clocks rwds_clk] 0

set_false_path -fall_from [get_clocks virt_rwds_clk] -rise_to [get_clocks rwds_clk] -setup

set_false_path -rise_from [get_clocks virt_rwds_clk] -fall_to [get_clocks rwds_clk] -setup

set_false_path -fall_from [get_clocks virt_rwds_clk] -fall_to [get_clocks rwds_clk] -hold

set_false_path -rise_from [get_clocks virt_rwds_clk] -rise_to [get_clocks rwds_clk] -hold

#set_false_path -from [get_clocks clk_0] -to [get_clocks rwds_clk]

#set_false_path -from [get_clocks rwds_clk] -to [get_clocks clk_0]

set_false_path -from [get_clocks rwds_clk] -to [get_clocks -of_objects [get_pins msys_i/clk_wiz_0/inst/mmcm_adv_inst/CLKOUT0]]

set_false_path -from [get_clocks -of_objects [get_pins msys_i/clk_wiz_0/inst/mmcm_adv_inst/CLKOUT0]] -to [get_clocks rwds_clk]

#

#Output Delay Constraint - HB_CLK0-HB_DQ

#

create_generated_clock -name HB_CLK0_0 -source [get_pins */*/*/U_IO/U_CLK0/dq_idx_[0].ODDR_inst/C] -multiply_by 1 -invert [get_ports HB_CLK0_0]

set_output_delay -clock [get_clocks HB_CLK0_0] -min -1.000 ${HB_dq_ports}

set_output_delay -clock [get_clocks HB_CLK0_0] -max 1.000 ${HB_dq_ports}

set_output_delay -clock [get_clocks HB_CLK0_0] -min -1.000 ${HB_dq_ports} -clock_fall -add_delay

set_output_delay -clock [get_clocks HB_CLK0_0] -max 1.000 ${HB_dq_ports} -clock_fall -add_delay

set_false_path -from [get_pins */*/*/U_HBC/*/dq_io_tri_reg/C] -to ${HB_dq_ports}

#set_false_path -from * -to [get_pins */*/inst/*/i_iavs0_270_rstn_1_reg/CLR]

#set_false_path -from * -to [get_pins */*/inst/*/i_iavs0_270_rstn_2_reg/CLR]

#set_false_path -from * -to [get_pins */*/inst/*/i_iavs0_270_rstn_3_reg/CLR]

|

Software Design - Vitis

Note:

|

For Vitis project creation, follow instructions from:

Application

---------------------------------------------------------- FPGA Example scuMCS Firmware to configure SI5338 and Reset System. srec_spi_bootloaderTE modified 2021.2 SREC Bootloader to load app or second bootloader from flash into DDR Descriptions:

xilisf_v5_11TE modified 2021.2 xilisf_v5_11

---------------------------------------------------------- Zynq Example: fsblTE modified 2021.2 FSBL General:

Module Specific:

fsbl_flashTE modified 2021.2 FSBL General:

ZynqMP Example: ---------------------------------------------------------- zynqmp_fsblTE modified 2021.2 FSBL General:

Module Specific:

zynqmp_fsbl_flashTE modified 2021.2 FSBL General:

zynqmp_pmufwXilinx default PMU firmware. ---------------------------------------------------------- General Example: hello_te0820Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output. u-bootU-Boot.elf is generated with PetaLinux. Vitis is used to generate Boot.bin. |

Template location: "<project folder>\sw_lib\sw_apps\"

Hello TE0717

Trenz Hello World example as endless loop

Template location: \sw_lib\sw_apps\hello_te0717

The printed Text and the blinking of the red LED1 can be modified

spi_bootloader

TE modified SPI Bootloader from Henrik Brix Andersen.

Bootloader to load app or second bootloader from flash into DDR.

Here it loads the hello_te0717.elf from QSPI-Flash to RAM.

Descriptions:

- Modified Files: bootloader.c

- Changes:

- Change the SPI defines in the header

- Add some reiteration in the frist spi read call

Additional Software

| Note: |

No additional software is needed.

App. A: Change History and Legal Notices

Document Change History

To get content of older revision go to "Change History" of this page and select older document revision number.

|

|

Legal Notices

|

|