This is preliminary based on Vivado 2016.1 release, the "DDR Less" flow should become even easier with the next Vivado releases. Hope remains. |

Thats all, PS will load the FPGA bitstream and then do nothing. There is no need to patch the init tcl script, it does not include the DDR init so it will not freeze.

Do not add "hello.elf" as application to the BOOT.BIN, it would yield in non bootable boot image |

Loading application to be run after bitstream loading is also possible, more FSBL changes are needed then.

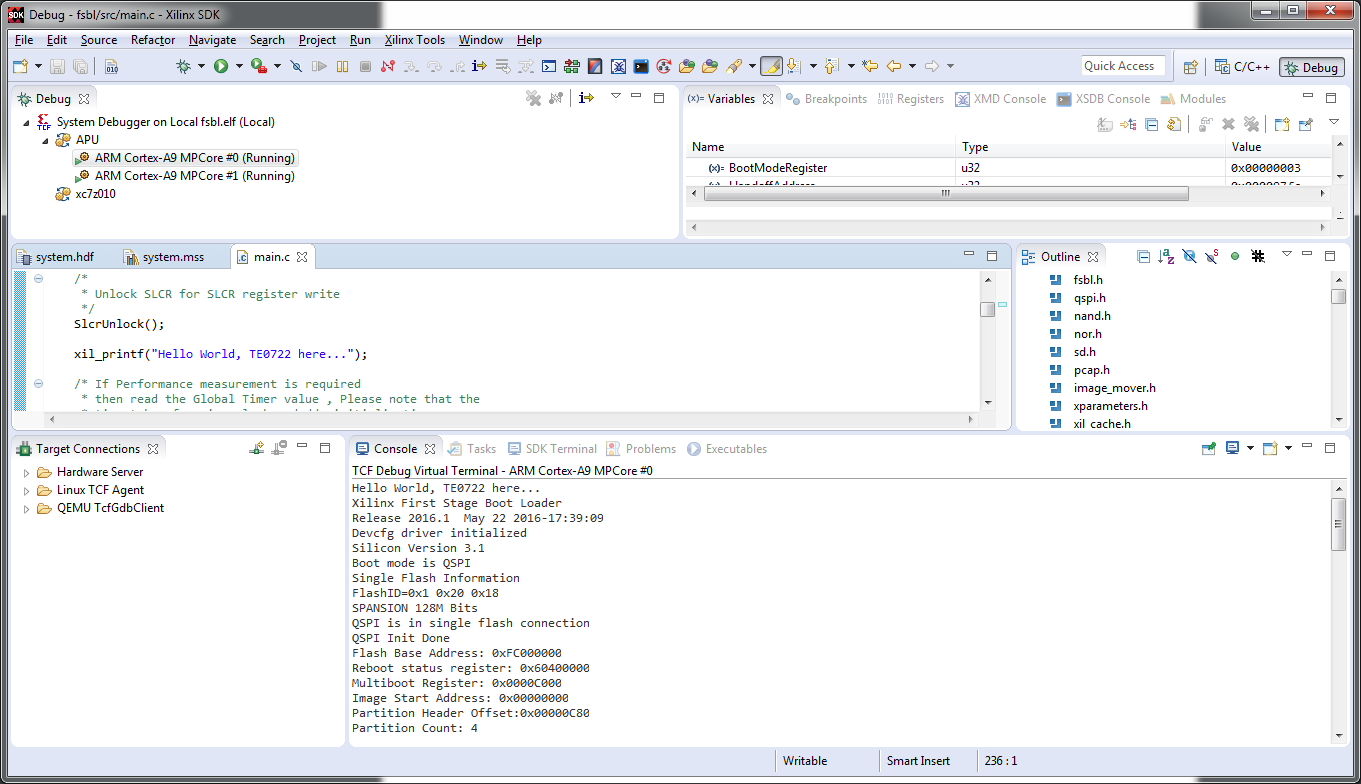

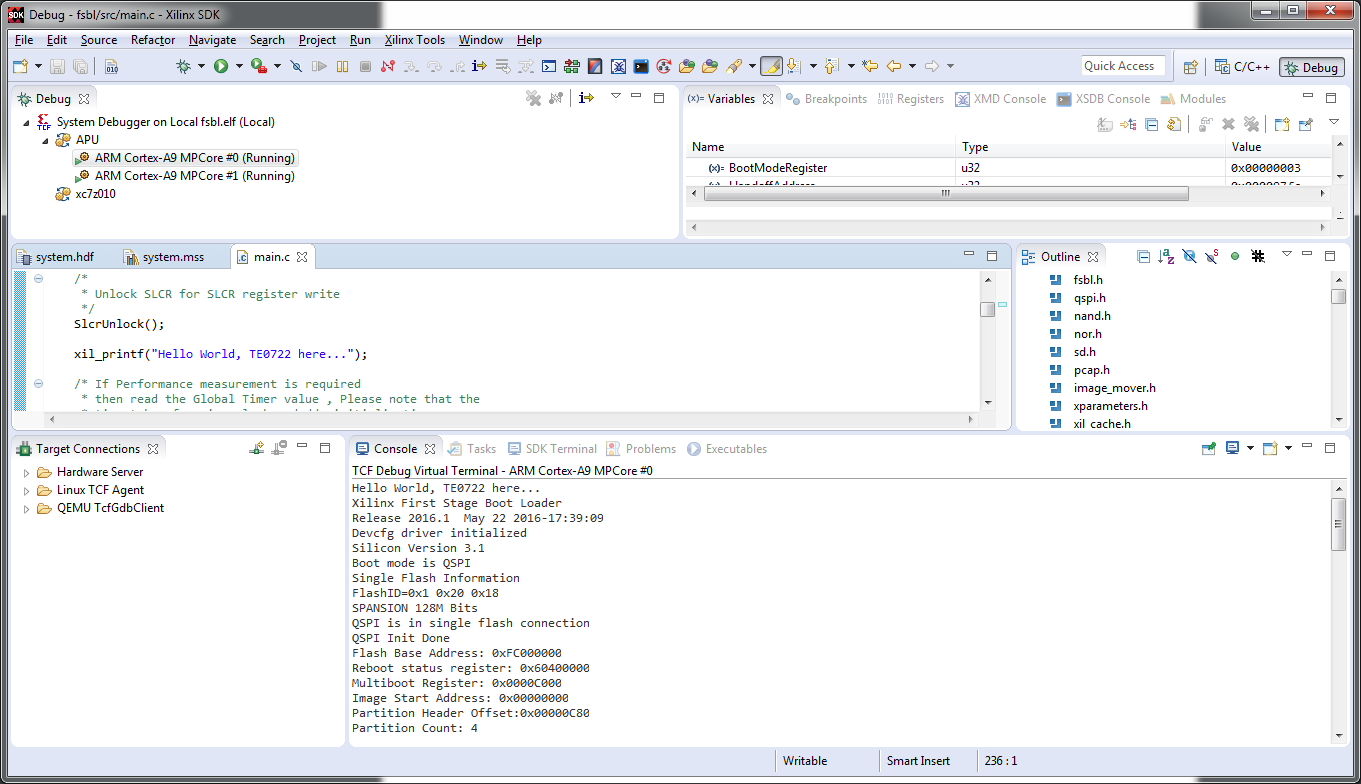

Example DDR less Zynq system debug session, FSBL with JTAG DCC console running on TE0722.