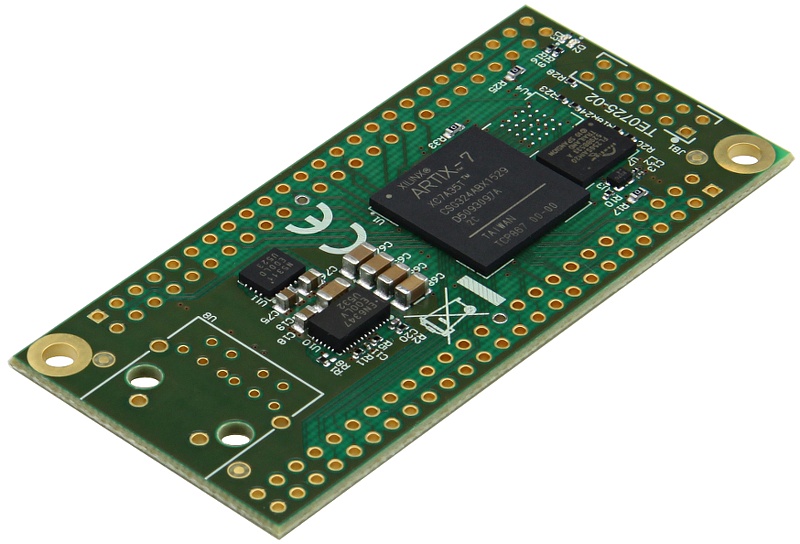

The Trenz Electronic TE0725 is a low cost small-sized FPGA module integrating a Xilinx Artix-7 (15-100T) and 32 MByte Flash memory for configuration and operation.

The 2 x 50 pin headers with a 2,54mm standard pitch are perfect for breadboard or low cost dual PCB design.

|

|

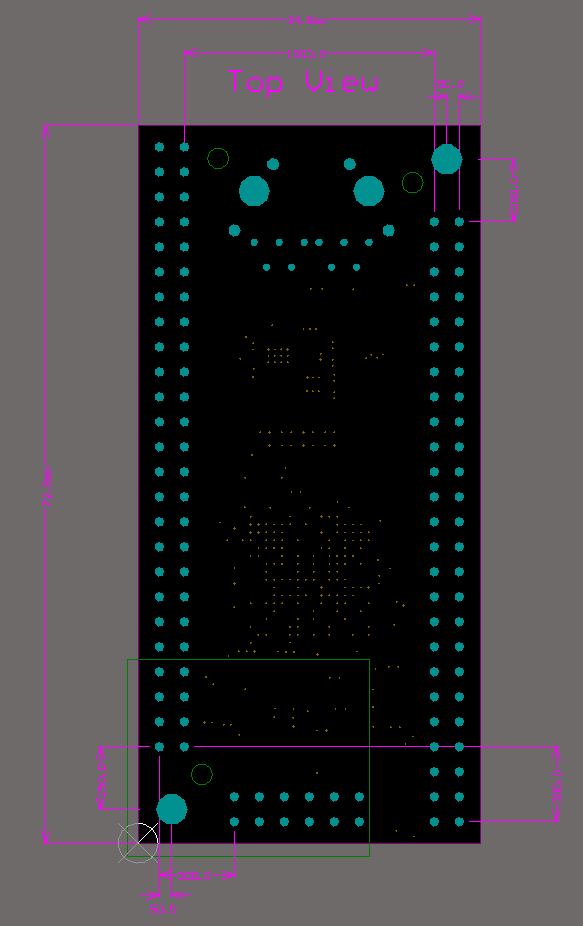

| Top View | Bottom View |

Xilinx Artix-7 XC7A35T (A15 to A100T)

Commercial Temperature Grade (Industrial on Request)

32 MByte Flash Memory

2 x 50 Pin Headers with 2,54mm Pitch, Ideal for Breadboard Use

3.3V Single Power Supply with On-Board Voltage Regulators

Size 73 x 35 mm

JTAG/UART Connector

2 LED's

...

| Bank | VCCIO | B2B I/O | Notes |

|---|---|---|---|

| 0 | 3.3V | 0 | JTAG |

| 14 | 3.3V | 0 (3) | 3 I/O in XMOD-JTAG - for use as UART |

| 15 | 1.8V | 0 | used for optional hyper RAM |

| 16 | 2.5V | 0 | used for optional optical fiber |

| 34 | User select | 42 | 0R resistor option to select 3.3V |

| 35 | User select | 42 | 0R resistor option to select 3.3V |

| Bitrate MB/s | Notes | |

|---|---|---|

AFBR-59F2Z | 250 |

JTAG access to the Xilinx Artix-7 device is provided through connector JB1.

| TCK | JB1: 4 |

| TDO | JB1: 8 |

| TDI | JB1: 10 |

| TMS | JB1: 12 |

Connector JB1 (2 x 6 pin Header) is directly compatible to XMOD JTAG Adapter TE0790. This adapter can be inserted from top onto the TE0725, if JB1 is fitted with male pin header. Optionally JB1 can be fitted with pin header from bottom, in that case the JTAG cable connector must be on the base board.

When using XMOD-JTAG in JB1 then additionally USB UART is usable, and the push-button on XMOD works as configuration reset.

When using XMOD-JTAG please check the switch settings on XMOD to be sure the power and I/O reference are supplied correctly. TE0790 can in some case be used to power up TE0725, this is however not recommended. TE0790-01 has not enough power for TE0725 (LED Blink may work, for larger designs the XMOD delivered power may be not sufficient).

| LED | Color | FPGA | |

|---|---|---|---|

| D2 | green | M16 | |

| D3 | red | DONE | Active Low |

All connectors are are for 100mil headers, all connector locations are in 100 mil grid.

| LED | Color | FPGA | |

|---|---|---|---|

| D2 | green | M16 | |

| D3 | red | DONE | Active Low |

For startup, a power supply with minimum current capability of 1A is recommended.

Single 3.3V Power supply required.

| FPGA | Design | Typical Power, 25C ambient |

|---|---|---|

| A35T | not configured | TBD |

| A35T | LED Blinky | 170mW (typical) |

| A100T | not configured | TBD |

TBD - To Be Determined.

Measurements and placement of the connectors and mounting holes. All 100 mil pin headers are in 100 mil grid, the M3 mounting holes are in 50 mil grid aligned to the centers of the 100mil headers. The module is symmetrical, turning it 180 degrees will keep all I/O and Power Pins in both 50 pin headers in compatible places.

| Date | Revision | Notes | PCN | Documentation link |

|---|---|---|---|---|

| - | 01 | Prototypes | ||

| - | 02 | First production release |

Hardware revision number is printed on the PCB board together with the module model number separated by the dash.

| Date | Revision | Contributors | Description |

|---|---|---|---|

| 2016-12-02 | Jan Kumann | Initial version |