Table of Contents

Download PDF version of this document. |

Table of Contents |

Refer to https://shop.trenz-electronic.de/en/Download/?path=Trenz_Electronic/carrier_boards/TE0706 for downloadable version of this manual and additional technical documentation of the product. |

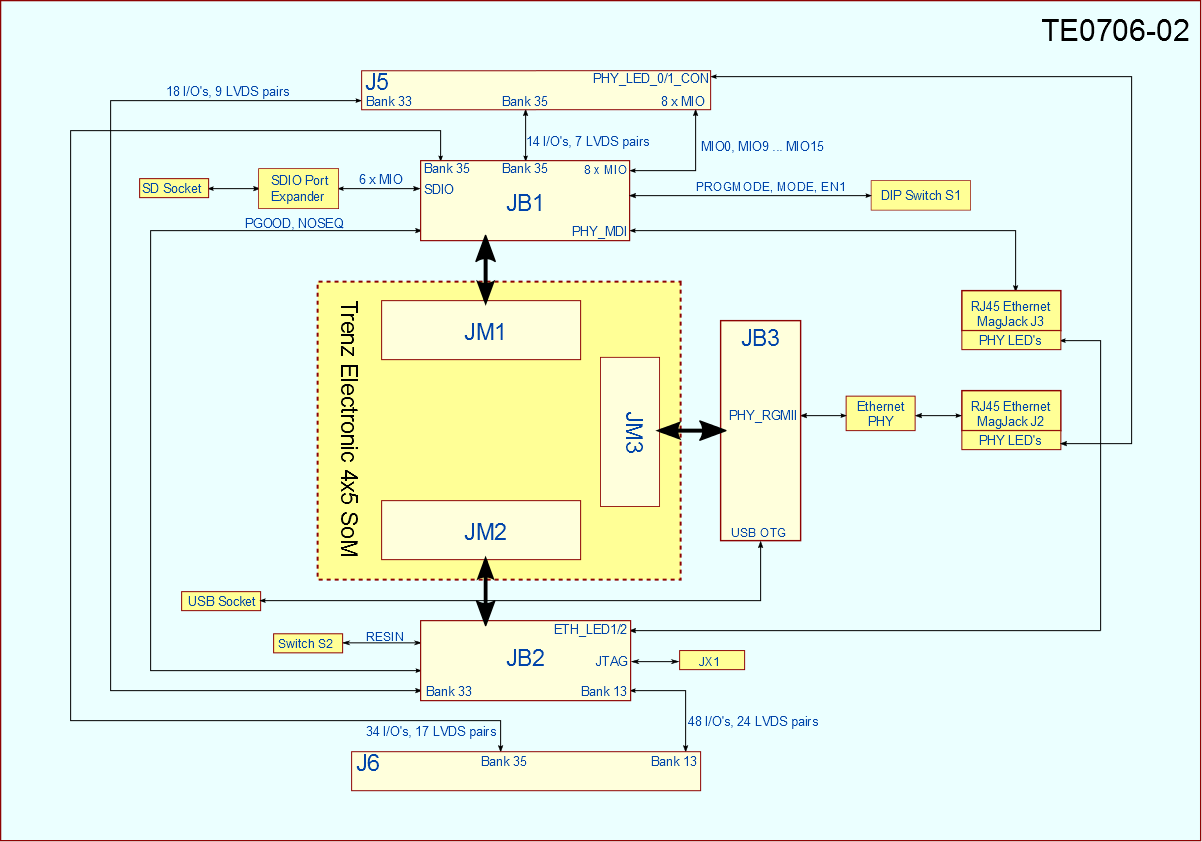

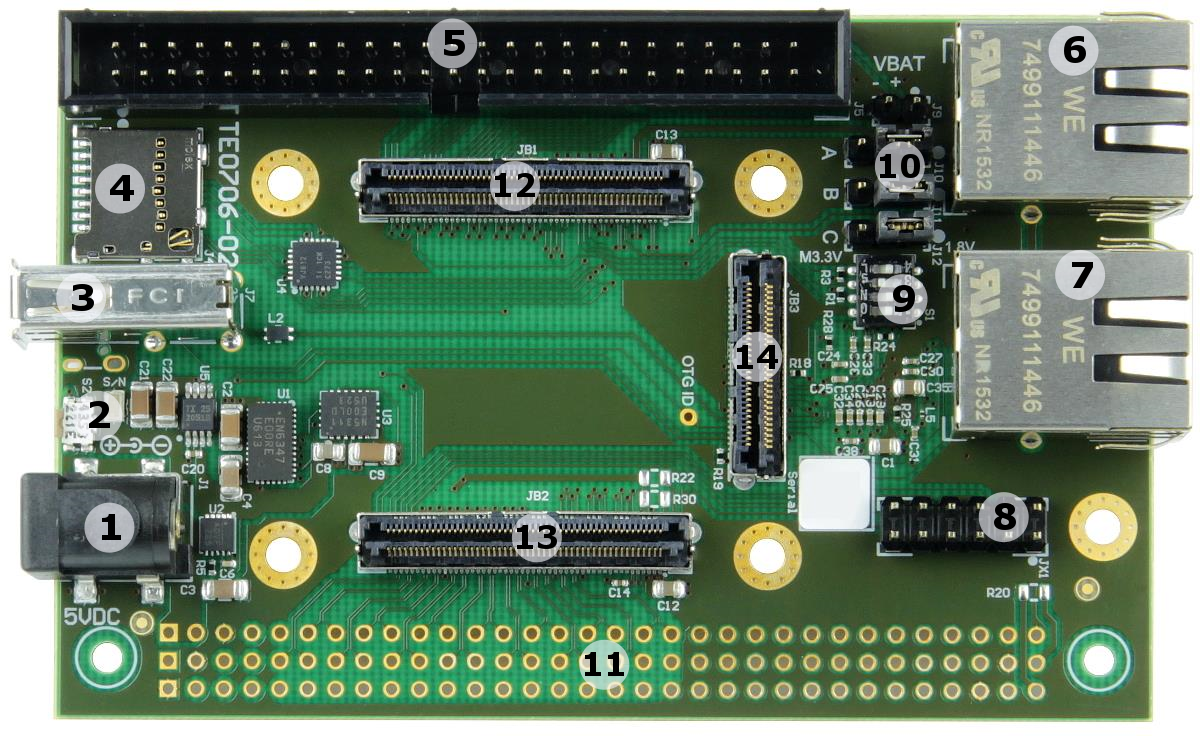

The Trenz Electronic TE0706 is a baseboard intended for use with 4x5 SoMs manufactured by the company. Baseboard exposes MIO- and PS/PL-pins of the SoM to accessible connectors and provides a whole range of on-board components for SoMs evaluation and testing.

See page "4x5 cm carriers" for information about the SoMs supported by the TE0706.

Board is shipped in following configuration:

Different delivery configurations are available upon request.

For detailed information about the B2B pin out, please refer to the Master Pin-out Table.

JTAG access to the SoMs Xilinx Zynq chip on the SoM is provided via 12-pin header JX1 and controlled by DIP switch S1-2. JTAG pins are routed to the JB2 and JX1 connectors as follows:

JTAG Signal | B2B Connector | 12-pin header JX1 |

|---|---|---|

| TMS | JB2-94 | 12 |

| TDO | JB2-98 | 8 |

| TDI | JB2-96 | 10 |

| TCK | JB2-100 | 4 |

Micro SD Card socket is not directly wired to the B2B connector pins, but through a Texas Instruments TXS02612 SDIO port expander, which is needed for voltage translation due to the different voltage levels of the Micro SD Card and MIO bank 501 of the Xilinx Zynq 7000 chip. The Micro SD Card has 3.3 V signal voltage-level, but the MIO Bank 501 on the Xilinx Zynq 7000 chip is set to 1.8 V.

The TE0706-02 is equipped with a Marvell Alaska 88E1512 Gigabit Ethernet PHY (U6) connected to the B2B connector JB3. The I/O Voltage is fixed at 1.8V. The reference clock input of the PHY is supplied by on-board 25MHz oscillator (U7).

PHY (U6) interface connections:

| PHY | B2B-pin | Notes |

|---|---|---|

| MDC/MDIO | JB3-49, JB3-51 | - |

| LED0 | - | Connected to Ethernet jack J2 LED0 (green). |

| LED1 | - | Connected to Ethernet jack J2 LED1 (green). |

| INT | JB3-33 | - |

| CONFIG | JB3-60 | - |

| RESET | JB3-53 | - |

| RGMII | JB3-37 - JB-44, JB3-47, JB3-57 - JB-59 | 12 pins. |

| SGMII | - | Not connected. |

| MDI | - | Connected to Gigabit-Ethernet MagJack J2. |

RJ45 Gigabit Ethernet MagJack J3

The TE0706-02 carrier board is also equipped with a second Gigabit-Ethernet MagJack J3, which is connected via MDI to the B2B connector JB1.

There is usually a corresponding Gigabit Ethernet PHY on 4x5 SoMs (e.g. TE0715 or TE0720), which can be used in conjunction with the baseboard MagJack J3.

TE0706-02 board has one physical USB type A socket J7 routed to B2B connector JB3. The corresponding USB-transceiver on 4x5 SoMs varies in order of the used SoM model.

There is also the option to equip a micro USB 2.0 type B receptacle socket (J8) to the board as alternative.

| Note: Pin OTG-ID is only assigned to USB 2.0 type B socket. |

| Switch | Signal Name | ON | OFF | Notes |

|---|---|---|---|---|

| S1-1 | - | - | - | Not connected |

| S1-2 | PROGMODE | JTAG enabled for programing SoM FPGA | JTAG enabled for programing SoM CPLD | - |

| S1-3 | MODE | Drive SoM SC CPLD pin 'MODE' low | leave SoM SC CPLD pin 'MODE' open | Boot mode configuration, if supported by SoM. (Depends also on SoM SC CPLD firmware). |

| S1-4 | EN1 | Drive SoM SC CPLD pin 'EN1' low | drive SoM SC CPLD pin 'EN1' high | Usually used to enable/disable FPGA core-voltage supply. (Depends also on SoM SC CPLD firmware). Note: Power-on sequence will be intermitted when S1-4 is set to OFF and functionality is supported by SoM. |

Power supply with minimum current capability of 3A for system startup is recommended.

TE0706-02 needs one single power supply with nominal of 5V.

| Power Input Pin | Max Current |

|---|---|

| VIN | 4A |

Typical power consumption for TE0706-02 in conjunction with different 4x5 SoMs under certain configurations will be determined soon.

It is not allowed to feed any voltage to any external I/O pin before there is no power indication on M3.3VOUT pins. Presence of 3.3V on B2B JB2 connector pins 9 and 11 indicates that module is properly powered up and ready.

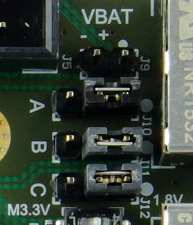

If VCCIOA or VCCIOC will be powered through the dedicated pins of external connector J6, then corresponding VCCIO jumpers J10 and J12 should be removed.

Refer to the 4x5 Module Integration Guide for VCCIO voltage options.

Baseboard supply voltage | Baseboard B2B connector pins | Standard assignment of PL I/O bank supply voltages on TE 4x5 module's B2B connectors |

|---|---|---|

| VCCIOA | JB1-10, JB1-12 | VCCIOA (JM1-9, JM1-11) |

| VCCIOB | JB2-6 | VCCIOC (JM2-5) |

| VCCIOC | JB2-8, JB2-10 | VCCIOD (JM2-7, JM2-9) |

| Fixed 1.8V | JB2-2, JB2-4 | VCCIOB (JM2-1, JM2-3) |

Note: The corresponding PL I/O bank supply voltages of the 4x5 SoM to the selectable baseboard voltages VCCIOA, VCCIOB and VCCIOC are depending on the mounted 4x5 SoM and varying in order of the used model. Refer to the SoMs schematic for information about the specific pin assignments on module's B2B-connectors regarding the PL I/O bank supply voltages and to the 4x5 Module integration Guide for VCCIO voltage options. |

Following table describes how baseboard supply voltages VCCIOA, VCCIOB, VCCIOC and 1.8V are connected to the PL I/O bank voltages on different supported 4x5 SoMs:

Baseboard supply voltage | TE0710 | TE0711 | TE0712 | TE0713 | TE0715 xx-15 | TE0715 xx-30 | TE0720 | TE0741 | TE0841 |

|---|---|---|---|---|---|---|---|---|---|

| VCCIOA | Bank 15, VCCIOA | Bank 15, VCCIOA | Bank 16, VCCIOA | Bank 16, VCCIOA | Bank 13, VCCIOA | Bank 13, VCCIOA | Bank 35, VCCIOA | Bank 13, VCCIOA | Bank 64, VCCIOA |

| VCCIOB | - | - | - | - | Bank 34, VCCIOC | Bank 34, HP bank, VCCIOC | Bank 33, VCCIOC | Bank 15, VCCIOC | Bank 68, HP bank, VCCIOC |

| VCCIOC | Bank 34, VCCIOD | Bank 35, VCCIOD | Bank 15, VCCIOD | Bank 15, VCCIOD | Bank 35, VCCIOD | Bank 35, HP bank, VCCIOD | Bank 13, VCCIOD | Bank 12, VCCIOD | Bank 67, HP bank, VCCIOD |

| Fixed 1.8V | - | Bank 34, VCCIOB | Bank 13, VCCIOB | Bank 13, VCCIOB | - | - | Bank 34, VCCIOB | Bank 16, VCCIOB | Bank 66, HP bank, VCCIOB |

Jumper settings to configure VCCIOA, VCCIOB and VCCIOC voltages supplied by the baseboard.

Jumper J10 | 1-2 | 2-3 | Voltage |

|---|---|---|---|

VCCIOA | ON | OFF | 1.8 V |

| VCCIOA | OFF | ON | 3.3 V |

Jumper J11 | 1-2 | 2-3 | Voltage |

|---|---|---|---|

| VCCIOB | ON | OFF | 1.8 V |

| VCCIOB | OFF | ON | 3.3 V |

Jumper J12 | 1-2 | 2-3 | Voltage |

|---|---|---|---|

| VCCIOC | ON | OFF | 1.8 V |

| VCCIOC | OFF | ON | 3.3 V |

| Header J9 provides the possibility to connect battery-buffered supply voltage to SoM's VBAT pin. |

Parameter | Min | Max | Units | Reference document |

|---|---|---|---|---|

Supply voltage VIN | -0.3 | 7 | V | EN6347QI / EN5311QI datasheet. Note: USB-VBUS = VIN, if enabled. |

Storage temperature | -55 | +125 | °C | Marvell 88E1512 datasheet. |

Parameter | Min | Max | Units | Reference document |

|---|---|---|---|---|

Supply Voltage Vin | 4.75 | 5.25 | V | - |

| Operating temperature | 0 | +70 | °C | Commercial grade. |

| Assembly variants for higher storage temperature range are available on request. |

| Please check components datasheets for complete list of absolute maximum and recommended operating ratings. |

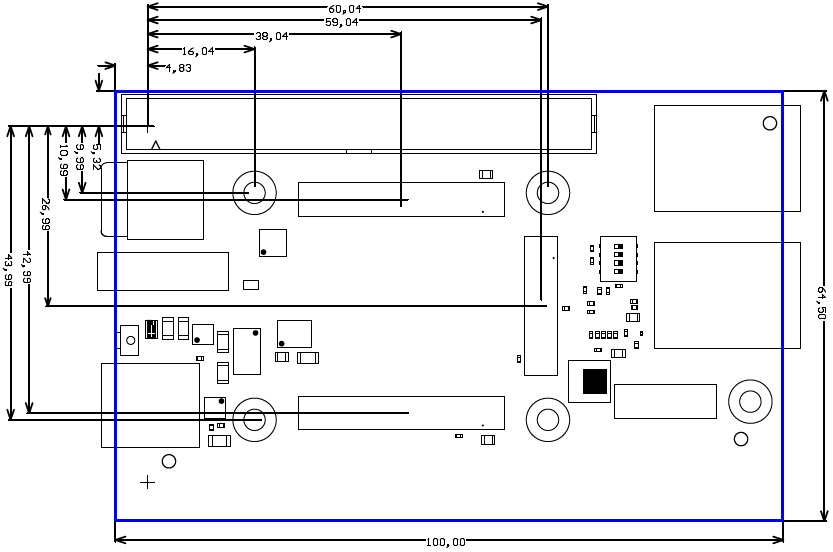

Board size: PCB 100mm × 64.5mm. Notice that the USB type A socket on the left and the Ethernet RJ-45 jacks on the right are hanging slightly over the edge of the PCB making the total width of the longer side approximately 106mm. Please download the assembly diagram for exact numbers.

Mating height of the module with standard connectors: 8mm

PCB thickness: 1.65mm

Highest parts on the PCB are USB type A socket and the Ethernet RJ-45 jacks, approximately 15mm. Please download the step model for exact numbers.

All dimensions are given in millimeters.

Commercial grade: 0°C to +70°C.

Industrial grade: -40°C to +85°C.

Board operating temperature range depends also on customer design and cooling solution. Please contact us for options.

115g - Plain baseboard.

13g - VG96 connector.

| Date | Revision | Notes | PCN | Documents |

|---|---|---|---|---|

| 2016-06-28 | 02 | First production revision | - | |

- | 01 | Prototypes | - |

Hardware revision number is printed on the PCB board next to the module model number separated by the dash.

Date | Revision | Contributors | Description |

|---|---|---|---|

| 2017-01-19 | Ali Naseri, Jan Kumann | Hardware revision 02 specific changes. | |

| 2016-01-06 | V1 | Ali Naseri | Initial document. |