Table of Contents

Download PDF Version of this Document. |

Table of Contents |

Refer to https://shop.trenz-electronic.de/de/Download/?path=Trenz_Electronic/carrier_boards/TEBA0841 for downloadable version of this manual and additional technical documentation of the product. |

The Trenz Electronic TEBA0841 Carrier Board is a base-board for 4 x5 SoMs, which is dedicated to test- and evaluation-purposes of Multi-gigabit transceiver units of Trenz Electronic 4x5 SoMs.

This base-board provides also soldering-pads as place-holders for pin-headers as option to get access to the PS- and PL-IO-banks of the mounted SoM.

See page "4 x 5 cm carriers" to get information about the SoMs supported by the TEBA0841 Carrier Board.

Figure 1: TEBA0841-01 Block Diagram

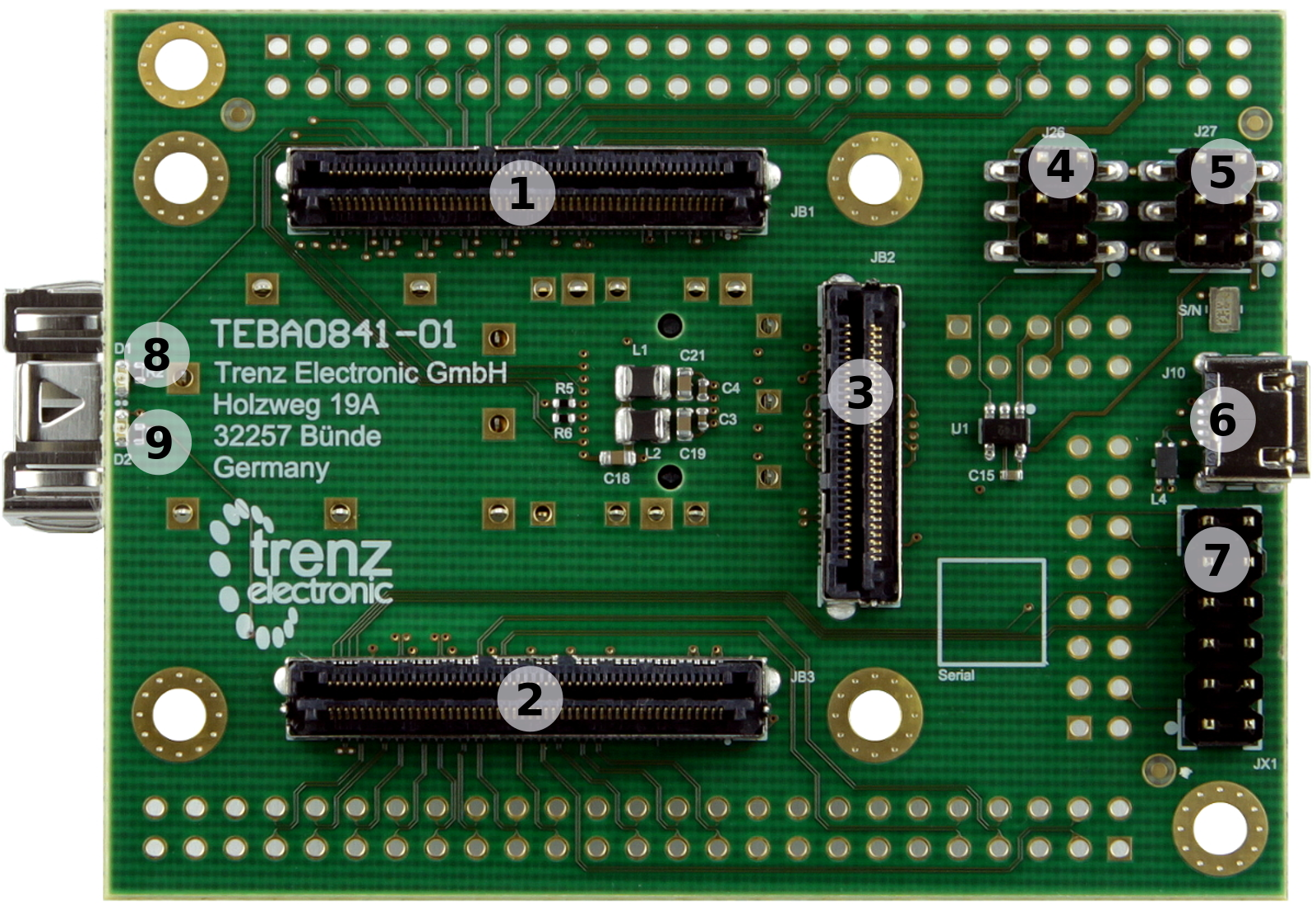

Figure 2: 4x5 SoM carrier board TEBA0841-01

TEBA0841-01:

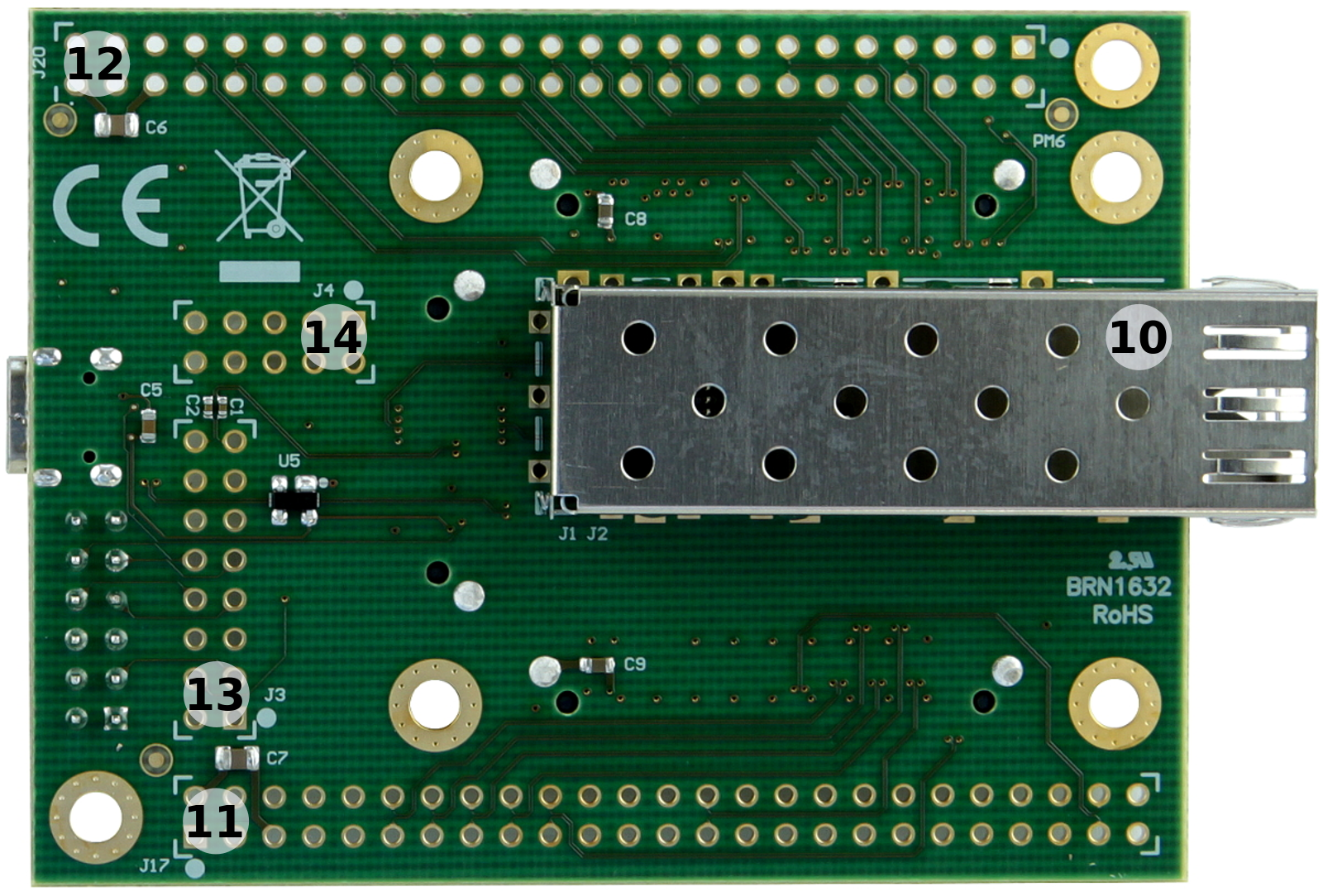

On the TEBA0841 Carrier Board is a SFP+ connector J1 (board-rev. 01: Molex 74441-0001). The connector is embedded into a SFP cage J2 (board-rev. 01: Molex 74737-0009).

The RX-/TX-data-lanes are connected to B2B-connector JB2, the control-lines are connected to pins on B2B-connector JB1 and are MIO-pins in standard TE module's pin-assignment.

On this SFP+ connector, on both 4 x 5 SoMs TE0741 and TE0841 MGT-lane 3 is accessible.

The pin-assignment of the SFP connector is in detail as fellows:

| SFP+ pin | SFP+ pin netname | B2B |

|---|---|---|

| Transmit Data + (pin 18) | MGT_TX3_P | JB2-26 |

| Transmit Data - (pin 19) | MGT_TX3_N | JB2-28 |

| Receive Data + (pin 13) | MGT_RX3_P | JB2-25 |

| Receive Data - (pin 12) | MGT_RX3_N | JB2-27 |

| Receive Fault (pin 2) | MIO10 | JB1-96 |

| Receive disable (pin 3) | not connected | - |

| MOD-DEF2 (pin 4) | MIO13 | JB1-98 |

| MOD-DEF1 (pin 5) | MIO12 | JB1-100 |

| MOD-DEF0 (pin 6) | MIO11 | JB1-94 |

| RS0 (pin 7) | not connected | - |

| LOS (pin 8) | MIO0 | JB1-88 |

| RS1 (pin 9) | not connected | - |

Table 1: SFP+ connector pin-assignment

The TEBA0841 Carrier Board is mainly for the 4 x 5 SoMs TE0841 and TE0741. This SoMs have GTX-Transceiver units on their FPGA-modules with up to 8 available MGT-lanes. To test this MGT-lanes, the RX/TX differential pairs are bridged, hence the transmitted data on this MGT-lanes are received simultaneously by the same MGT-lane.

The MGT-lane pins are bridged as fellows, if 4 x 5 SoM TE0741 is mounted:

| MGT-lane | B2B TX diff-pair | B2B RX diff-pair | B2B-pins bridged |

|---|---|---|---|

| MGT-lane 0 | JB2-8 (MGT_TX0_N) JB2-10 (MGT_TX0_P) | JB2-7 (MGT_RX0_N) JB2-9 (MGT_RX0_P) | JB2-7 to JB2-8 bridged JB2-9 to JB2-10 bridged |

| MGT-lane 1 | JB2-14 (MGT_TX1_N) JB2-16 (MGT_TX1_P) | JB2-13 (MGT_RX1_N) JB2-15 (MGT_RX1_P) | JB2-13 to JB2-14 bridged JB2-15 to JB2-16 bridged |

| MGT-lane 2 | JB1-20 (MGT_TX2_N) JB1-22 (MGT_TX2_P) | JB1-19 (MGT_RX2_N) JB1-21 (MGT_RX2_P) | JB1-19 to JB1-20 bridged JB1-21 to JB1-22 bridged |

| MGT-lane 7 | JB1-3 (MGT_TX7_P) JB1-5 (MGT_TX7_N) | JB1-9 (MGT_RX7_P) JB1-11 (MGT_RX7_N) | JB1-3 to JB1-9 bridged JB1-5 to JB1-11 bridged |

| MGT-lane 6 | JB1-15 (MGT_TX6_P) JB1-17 (MGT_TX6_N) | JB1-21 (MGT_RX6_P) JB1-23 (MGT_RX6_N) | JB1-15 to JB1-21 bridged JB1-17 to JB1-23 bridged |

Table 2: Bridging-table of the MGT-lanes for mounted 4 x 5 SoM TE0741.

| Note: The MGT-lanes of 4 x 5 SoM TE0841 have other designations. |

The TEBA0841 carrier board has one physical USB-connector J10, which is available as Micro-USB port. The USB interface J10 can be operated in Device- and OTG-modes. The Micro-USB port-pins are routed to the USB-OTG-interface on B2B-connector JB2. There are usually corresponding USB-PHYs on SoMs supported by the Carrier Board TEBA0841.

The JTAG-interface of the mounted 4 x 5 SoM can be accessed via header JX1. This header has a 'XMOD FTDI JTAG Adapter'-compatible pin-assignment.

| JX1 pin | JX1 pin net name | B2B |

|---|---|---|

| C (pin 4) | TCK | JB3-100 |

| D (pin 8) | TDO | JB3-98 |

| F (pin 10) | TDI | JB3-96 |

| H (pin 12) | TMS | JB3-94 |

| A (pin 3) | MIO15 | JB1-86 |

| B (pin 7) | MIO14 | JB1-91 |

| E (pin 9) | BOOTMODE | JB1-90 |

| G (pin 11) | RESIN | JB3-17 |

Table 3: JTAG header JX1 pin-assignment

There is also the option to mount and solder a 2-row 16-pin header to the place-holder J3, which has the same pin-assignment as header JX1, but with also two additional pins (15,16) as LVDS-pair, to put an external reference clock-signal to the mounted 4 x 5 SoM. The clock-signal is put to to the SoM via B2B-connector pins JB2-32 (MGT_CLK0_N) and JB2-34 (MGT_CLK0_P).

On both interfaces (JX1, J3), the pins with the net-names MIO14 and MIO15 are available as user IO's which could be used as UART-interface for example.

There are two LEDs D1 (green) and D2 (red) available to the user. The green LED D1 is connected to the pin MIO9 (JB1-92), the red LED D2 is connected to the pin JB3-90 with the net name 'RLED'.

The place-holder J4 with solder-pads to mount a 2-row 10-pin header provides the capability, to access via this header the SDIO-port of the mounted 4 x 5 SoM, if available. For this purpose, there is also voltage-translation via SDIO port expander (e.g. Texas Instruments TXS02612) necessary due to the different voltage levels of the Micro SD Card (3.3V) and MIO bank of the Xilinx Zynq-chip (1.8V).

The place-holders J17 and J20 with solder-pads to mount 2-row 50-pin headers provide the capability to access the PL IO-bank pins of the mounted 4 x 5 SoM.

With mounted header J17 there are 42 IO's of PL-IO-bank 13 of the 4 x 5 SoM available (B2B-connector JB3), which are also usable as 21 LVDS-pairs. On this header the IO's are operable with fixed (3.3V) or selectable VCCIO-voltage VCCIOD.

On header J20 there are 42 IO's available of PL-IO-bank 35 (B2B-connector JB1). This IO's are also usable as 21 LVDS-pairs and operable with fixed (3.3V) or selectable VCCIO-voltage VCCIOA.

Power supply with minimum current capability of 3A at 12V for system startup is recommended.

The on-board voltages of the carrier board will be powered up simultaneously after one single power-supply with a nominal voltage of 12V is connected to the power-jack J10.

The PL IO-bank supply voltage FMC_VADJ will be available after the output of the 5.0V-DCDC-converter is active and the pin EN_FMC of the SC-CPLD is asserted.

Figure 3: Power-Up sequence diagram

On the TE0705 carrier board different VCCIO configurations can be chosen by jumper J21 and DIP-switch S3.

The purpose of the jumper and the DIP-switch S3 of the Carrier Board will be explained in the following sections.

On the TE0705 carrier board all PL IO-bank's supply voltages of the 4x5 SoM (VCCIOA, VCCIOB, VCCIOC, VCCIOD; see 4x5 Module Integration Guide) are connected to the VCCIO-voltage VIOTB, which is either fixed to 3.3V (J21: 1-2, 3) or selectable with the adjustable supply-voltage VADJ (J21: 1, 2-3). The supply-voltages have following pin-assignments on B2B-connectors:

base-board supply-voltages | base-board B2B connector-pins | standard assignment of PL IO-bank supply-voltages on TE 4x5 module's B2B connectors | base-board voltages and signals connected with |

|---|---|---|---|

| VIOTB | JB1-10, JB1-12, JB2-2, JB2-4, JB2-6, JB2-8, JB2-10 | VCCIOA (JM1-9, JM1-11), VCCIOB (JM2-1, JM2-3), VCCIOC (JM2-5), VCCIOD (JM2-7, JM2-9) | VCCIO3 (Systm-Controller-CPLD pin 5, 11, 23), J15 VTREF, J11, J13, J2, J5 and J6 VCCIO |

Table 4: base-board supply-voltage VIOTB

Note: The corresponding PL IO-voltage supply voltages of the 4x5 SoM to the selectable base-board voltage VIOTB are depending on the mounted 4x5 SoM and varying in order of the used model. Refer to SoM's schematic to get information about the specific pin-assignment on module's B2B-connectors regarding PL IO-bank supply voltages and to the 4x5 Module integration Guide for VCCIO voltage options. |

Following table describes how to configure the base-board supply-voltages by jumpers:

base-board supply-voltages vs voltage-levels | VIOTB | USB-VBUS |

|---|---|---|

| 3V3 | J21: 1-2, 3 | - |

| VADJ | J21: 1, 2-3 | - |

| 5V0 intern | - | J9: 1-2, 3 & J19: 1-2 (J20: 1-2: additional decoupling-capacitor 100 µF) |

| Vbus extern | - | J9: 1, 2-3 & J19: open |

Table 5: Configuration of base-board supply-voltages via jumpers. Jumper-Notification: 'Jx: 1-2, 3' means pins 1 and 2 are connected, 3 is open. 'Jx: 1, 2-3' means pins 2 and 3 are connected, 1 is open

| It is recommended to set and measure the PL IO-bank supply-voltages before mounting of TE 4x5 module to avoid failures and damages to the functionality of the mounted SoM. |

| Parameter | Min | Max | Units | Notes |

|---|---|---|---|---|

Vin supply voltage | 11.4 | 12.6 | V | 12.0V supply voltage ± 5% |

Storage Temperature | -55 | 125 | °C | Lattice MachX02 family data sheet |

| Parameter | Min | Max | Units | Notes |

|---|---|---|---|---|

| Vin supply voltage | 11.4 | 12.6 | V | - |

Board size: PCB 170.4 mm × 98 mm. Notice that some parts the are hanging slightly over the edge of the PCB like the mini USB-jacks (ca. 1.4 mm) and the Ethernet RJ-45 jack (ca 2.2 mm), which determine the total physical dimensions of the carrier board. Please download the assembly diagram for exact numbers.

Mating height of the module with standard connectors: 8mm

PCB thickness: ca. 1.65mm

Highest part on the PCB is the Ethernet RJ-45 jack, which has an approximately 17 mm overall hight. Please download the step model for exact numbers.

All dimensions are given in mm.

Figure 4: Physical Dimensions of the TE0705-04 carrier board

Commercial grade: 0°C to +70°C.

Board operating temperature range depends also on customer design and cooling solution. Please contact us for options.

ca. 110 g - Plain board

| date | revision | authors | description |

|---|---|---|---|

| 2017-02-10 | Ali Naseri | current TRM for TEBA0841-01 | |

| 2017-01-30 | 0.1 | Ali Naseri | Initial document |

| Date | Revision | Notes | PCN | Documentation link |

|---|---|---|---|---|

| 2016-10-04 | 04 | |||

| - | 03 | |||

| - | 02 | |||

| - | 01 |

Figure 5: Hardware revision Number

Hardware revision number is printed on the PCB board next to the model number separated by the dash.