Table of Contents

Download PDF Version of this Document. |

Table of Contents |

Refer to https://shop.trenz-electronic.de/de/Download/?path=Trenz_Electronic/carrier_boards/TEBB0714 for downloadable version of this manual and additional technical documentation of the product. |

The Trenz Electronic TEBB0714 is a base-board for test- and evaluation-purposes, especially for the Multi-gigabit transceiver units of the TE0714 module. Although this base-board is dedicated to the TE0714 module, it is also compatible with other Trenz Electronic 4 x 5 cm SoMs. See page "4 x 5 cm carriers" to get information about the SoMs supported by the TEBB0714 base-board.

This base-board provides also soldering-pads as place-holders for pin-headers as option to get access to the PL-IO-banks of the mounted SoM.

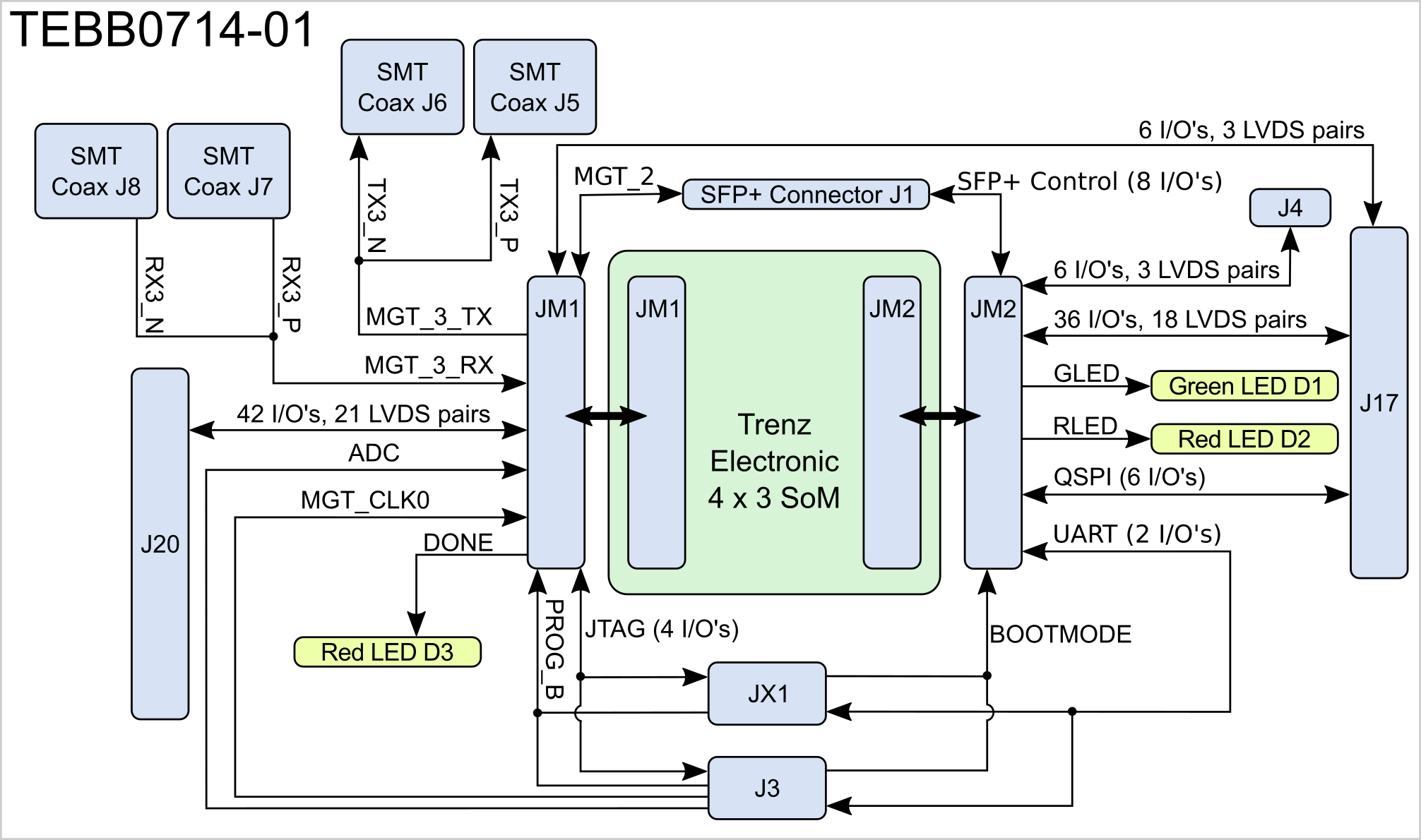

Figure 1: TEBB0714 -01 Block Diagram

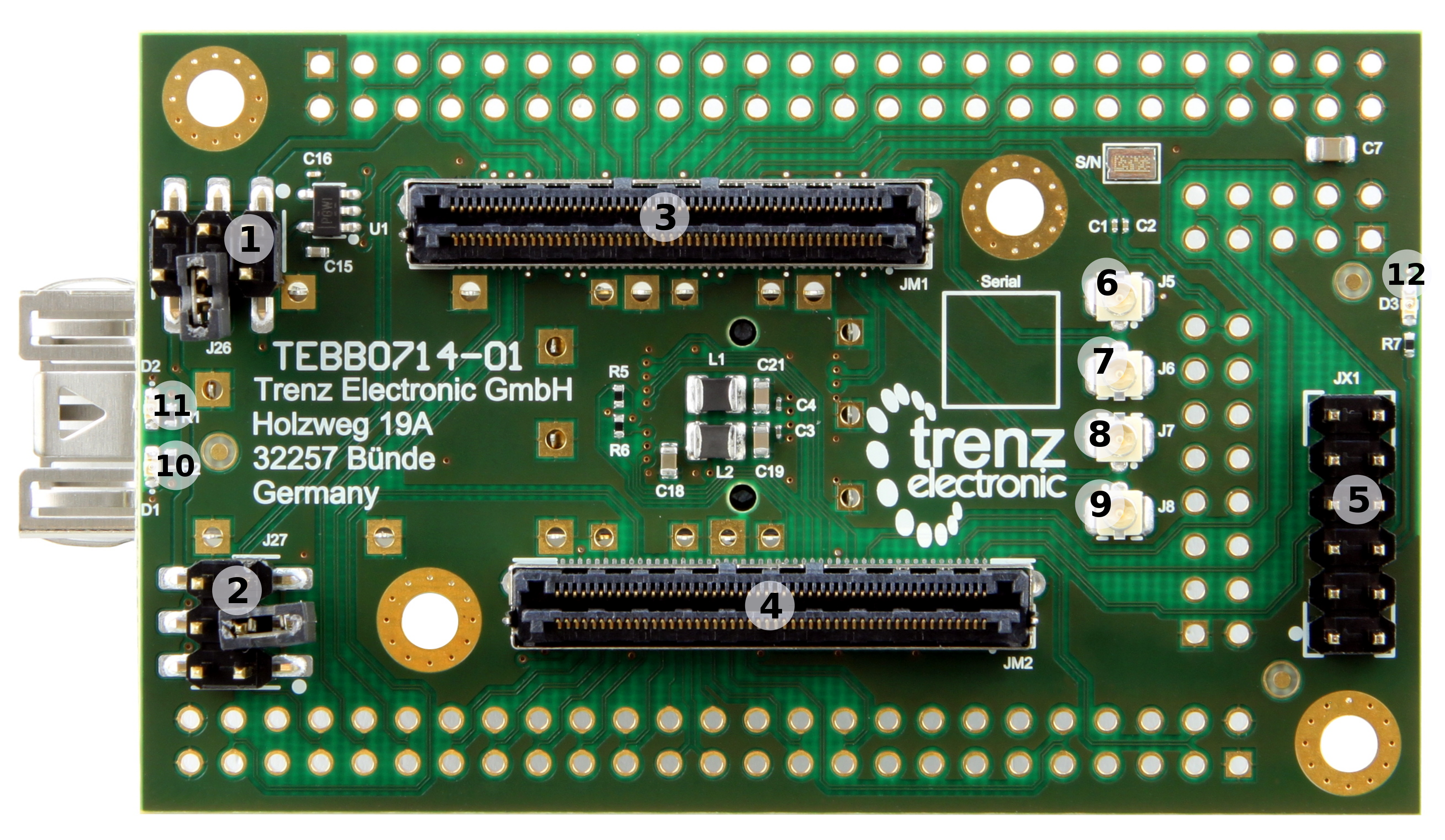

Figure 2: 4 x 5 cm SoM carrier board TEBB0714-01

TEBB0714 -01:

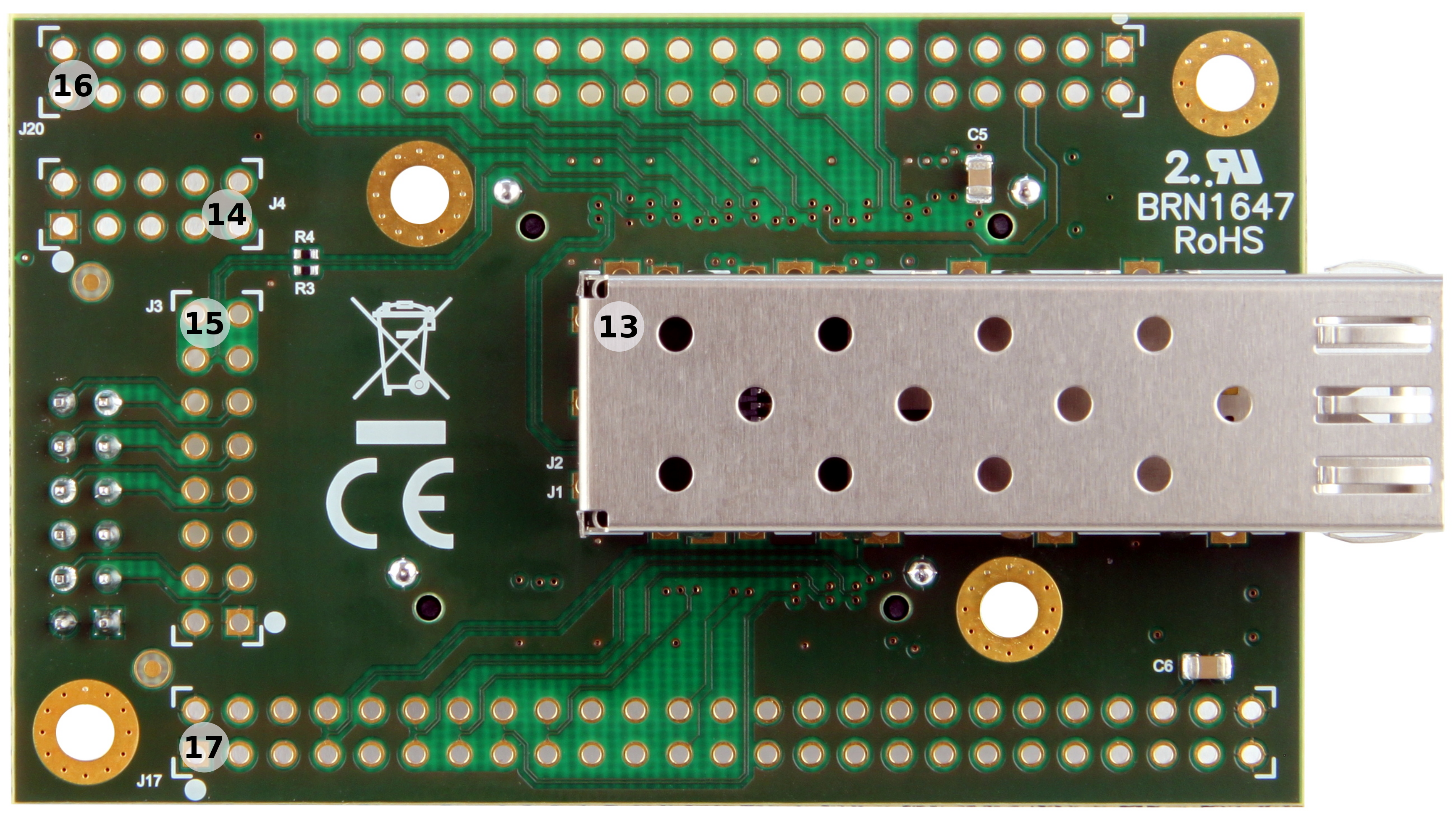

The TEBB0714 Carrier Board there provides a SFP+ connector J1 (Molex 74441-0001 at board-rev. 01 ). The connector is embedded into a SFP cage J2 (Molex 74737-0009 at board-rev. 01).

The RX-/TX-data-lanes are connected to B2B-connector JM1, the control-lines are connected to pins on B2B-connector JM2.

On this SFP+ connector, MGT-lane 2 is accessible at mounted 4 x 5 SoM TE0714.

The pin-assignment of the SFP connector is in detail as fellows:

| SFP+ pin | SFP+ pin netname | B2B | Note |

|---|---|---|---|

| Transmit Data + (pin 18) | MGT_TX2_P | JM1-14 | - |

| Transmit Data - (pin 19) | MGT_TX2_N | JM1-16 | - |

| Receive Data + (pin 13) | MGT_RX2_P | JM1-7 | - |

| Receive Data - (pin 12) | MGT_RX2_N | JM1-9 | - |

| Transmit Fault (pin 2) | SFP0_TX_FAULT | JM2-42 | - |

| Transmit disable (pin 3) | SFP0_TX_DIS | JM2-44 | - |

| MOD-DEF2 (pin 4) | SFP0_SDA | JM2-46 | 3.3V pull-up, (usable as I²C-SDA) |

| MOD-DEF1 (pin 5) | SFP0_SCL | JM2-48 | 3.3V pull-up, (usable as I²C-SCL) |

| MOD-DEF0 (pin 6) | SFP0_M0DEF0 | JM2-40 | - |

| RS0 (pin 7) | SFP0_RS0 | JM2-38 | - |

| LOS (pin 8) | SFP0_LOS | JM2-34 | - |

| RS1 (pin 9) | SFP0_RS1 | JM2-32 | - |

Table 1: SFP+ connector pin-assignment

........

.........

The JTAG-interface of the mounted 4 x 5 SoM can be accessed via header JX1. This header has a 'XMOD FTDI JTAG Adapter'-compatible pin-assignment:

| JX1 pin | JX1 pin net-name | B2B |

|---|---|---|

| C (pin 4) | TCK | JM1-90 |

| D (pin 8) | TDO | JM1-88 |

| F (pin 10) | TDI | JM1-86 |

| H (pin 12) | TMS | JM1-92 |

| A (pin 3) | B14_L25 | JM2-97 |

| B (pin 7) | B14_L0 | JM2-99 |

| E (pin 9) | BOOTMODE | JM2-100 |

| G (pin 11) | PROG_B | JM2-94 |

Table 3: JTAG header JX1 pin-assignment

There is also the option to mount and solder a 2-row 16-pin header to the place-holder J3, which has the same pin-assignment as header JX1, but with two additional two pins (15,16) as LVDS-pair to supply the mounted 4 x 5 SoM with an external reference clock-signal. The clock-signal is linked to to the SoM via B2B-connector pins JB2-32 (MGT_CLK0_N) and JB2-34 (MGT_CLK0_P).

Further two additional pins (13, 14) are designated as LVDS-pair for analog signals and routed to the ADC-unit of the SoM. This LVDS-pair has 1K serial resistors on both conductors and has on the B2B-connector JM1 the pins JM1-25 and JM1-27 with the net-names 'ADC_P' and 'ADC_N'.

On both interfaces (JX1, J3), the pins with the net-names B14_L25 and B14_L0 are available as user IO's which could be used as UART-interface for example.

There are two LEDs D1 (green) and D2 (red) available to the user. The green LED D1 is connected to the B2B-connector pin JM2-26 with the net-name 'GLED', the red LED D2 is connected to the pin JM2-24 with the net name 'RLED'.

LED D3 (red) is linked to the SoM's output signal 'DONE' indicating that the FPGA-modul is programmed properly.

The place-holder J4 with solder-pads to mount a 2-row 10-pin header provides additional 3 LVDS-pairs with the pin-mapping 3-4, 7-8 and 9-10. The LVDS-pairs are operable with the VCCIOs 3.3V or 3.3V_OUT from mounted module.

The place-holders J17 and J20 with solder-pads to mount 2-row 50-pin headers provide the capability to access the PL IO-bank pins of the mounted 4 x 5 SoM.

With mounted header J20 there are 42 IO's of PL-IO-bank 34 of the 4 x 5 SoM available, which are also usable as 21 LVDS-pairs. On this header the IO's are operable with fixed 3.3V or selectable VCCIO-voltage VCCIO34.

On header J17 there are 36 IO's available of PL-IO-bank 14. This IO's are also usable as 18 LVDS-pairs and operable with fixed 3.3V or module's config-VCCIO V_CFG (depending on module's configuration: 3.3V or 1.8V). This header provides also a QSPI interface consisting of 6 IO's.

Power supply with minimum current capability of 3A at 3.3V for system startup is recommended.

The on-board voltages of the carrier board will be powered up with an external power-supply with nominal voltage of 3.3V.

The external power-supply can be connected to the board by the following pins:

| Connector | 3.3V pin | GND pin |

|---|---|---|

| JX1 | JX1-5, JX1-6, | JX1-1, JX1-2 |

| J3 | J3-5 | J3-1, J3-2 |

| J4 | J4-5 | J4-1, J4-2 |

| J20 | J20-5, J20-46 | J20-1 , J20-2 , J20-49 , J20-50 |

| J17 | J17-5, J17-46 | J17-1 , J17-2 , J17-49 , J17-50 |

Table 4: Connector-pins capable for external 3.3V power-supply

The PL IO-bank supply-voltages 1.8V, 2.5V and 3.3V will be available after the mounted module's 3.3V voltage level is present on B2B connector JM2 pins 10 and 12, meaning that all on-module voltages have become stable and module is properly powered up.

Note: The supply-voltages have low current dropout.

Figure 3: Power-On sequence diagram

On the TEBB0714 carrier board different VCCIO configurations can be chosen by the jumper J26 and J27.

The purpose of the jumper of the Carrier Board will be explained in the following sections.

On the TEBB0714 carrier board the PL IO-bank's supply voltages of the 4x5 SoM (VCCIOA, VCCIOD; see 4x5 Module Integration Guide) are connected to the base-board VCCIO-voltage VCCIOA and VCCIOD, which are selectable between the supply-voltages 1.8V, 2.5V and 3.3V via jumper J26 and J27.

baseboard supply-voltages | base-board B2B connector-pins | standard assignment of PL IO-bank supply-voltages on TE 4x5 module's B2B connectors-pins |

|---|---|---|

| VCCIOA | JB1-10, JB1-12 | VCCIOA (JM1-9, JM1-11) |

| VCCIOD | JB2-8, JB2-10 | VCCIOD (JM2-7, JM2-9) |

Table 5: base-board supply-voltages VCCIOA and VCCIOD

Note: The corresponding PL IO-voltage supply voltages of the 4x5 SoM to the selectable base-board voltage VCCIOA and VCCIOD are depending on the mounted 4x5 SoM and varying in order of the used model. Refer to SoM's schematic to get information about the specific pin-assignment on module's B2B-connectors regarding PL IO-bank supply-voltages and to the 4x5 Module integration Guide for VCCIO voltage options. |

Following table describes how to configure the base-board supply-voltages by jumpers:

base-board supply-voltages vs voltage-levels | VCCIOA | VCCIOD |

|---|---|---|

| 1.8V | J26: 1-2 | J27: 1-2 |

| 2.5V | J26: 3-4 | J27: 3-4 |

| 3.3V | J26: 5-6 | J27: 5-6 |

Table 6: Configuration of base-board supply-voltages via jumpers. Jumper-Notification: 'Jx: 1-2' means pins 1 and 2 are connected, 'Jx: 3-4' means pins 3 and 4 are connected, and so on.

| It is recommended to set and measure the PL IO-bank supply-voltages before mounting of TE 4x5 module to avoid failures and damages to the functionality of the mounted SoM. |

| Parameter | Min | Max | Units | Notes |

|---|---|---|---|---|

Vin supply voltage | 3.135 | 3.465 | V | 3.3V supply-voltage ± 5% |

Storage Temperature | -55 | 105 | °C | Molex 74441-0001 Product Specification |

| Parameter | Min | Max | Units | Notes |

|---|---|---|---|---|

| Vin supply voltage | 3.135 | 3.465 | V | - |

Board size: PCB 56.47 mm × 75 mm. Notice that some parts the are hanging slightly over the edge of the PCB like the mini USB-jacks and the SFP+ connector, which determine the total physical dimensions of the carrier board. Please download the assembly diagram for exact numbers.

Mating height of the module with standard connectors: 8mm

PCB thickness: ca. 1.65mm

Highest part on the PCB is the SFP+ connector, which has an approximately 11.3 mm overall hight. Please download the step model for exact numbers.

The dimensions are given in mm and mil (milli inch).

Figure 4: Physical Dimensions of the TEBA0841-01 carrier board

Commercial grade: 0°C to +70°C.

Board operating temperature range depends also on customer design and cooling solution. Please contact us for options.

ca. 32 g - Plain board

| date | revision | authors | description |

|---|---|---|---|

| 2017-02-08 | Ali Naseri | current TRM for TEBA0841-01 | |

| 2017-01-30 | 0.1 | Ali Naseri | Initial document |

| Date | Revision | Notes | PCN | Documentation link |

|---|---|---|---|---|

| - | 01 |

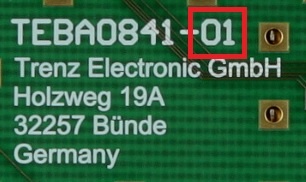

Figure 5: Hardware revision Number

Hardware revision number is printed on the PCB board next to the model number separated by the dash.