<!-- Template Revision 1.5 --> |

Online version of this manual and other related documents can be found at https://wiki.trenz-electronic.de/display/PD/SC-CPLD-Firmware |

Table of contents |

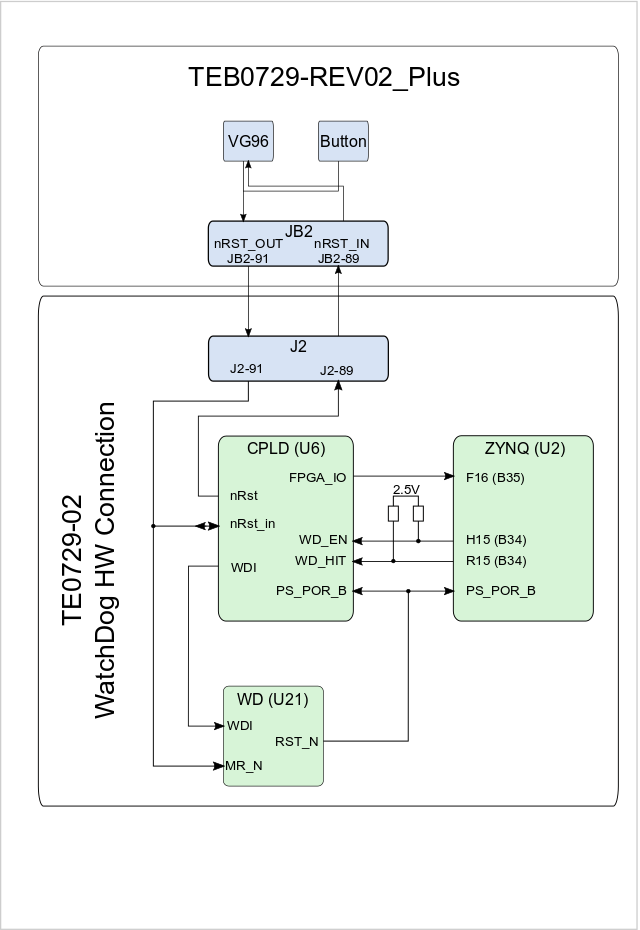

Firmware for PCB CPLD with designator U6. Second CPLD Device in Chain: LCMX02-256HC

Watchdog do not work correctly on all modules with Firmware released before 2017.08.22. Please update Firmware on CPLD. For questions, write to Trenz Electronic support. |

2 Firmware variants with swapped external reset input and output available.

Figure1: Firmware for TEB0729 without modification,

|  Figure2: Firmware for TEB0729 with modification,

|

See Document Change History

| Name / opt. VHD Name | Direction | Pin | Description |

|---|---|---|---|

| BOARD_STAT | out | 23 | STATUS to B2B |

| BOOT_MODE1 | in | 28 | Boot Mode Pin from B2B |

| BOOT_MODE2 | in | 27 | Boot Mode Pin from B2B |

| BOOT1 | out | 13 | Boot Mode Pin to FPGA (MIO4) |

| BOOT2 | out | 12 | Boot Mode Pin to FPGA (MIO5) |

| EN_3V3 | out | 25 | Enable 3.3V Switch |

| F_TCK | out | 8 | JTAG to FPGA |

| F_TDI | out | 9 | JTAG to FPGA |

| F_TDO | in | 11 | JTAG from FPGA |

| F_TMS | out | 10 | JTAG to FPGA |

| FPGA_IO | out | 5 | Status to FPGA |

| JTAGSEL | --- | 26 | Enable JTAG access to CPLD for Firmware update (zero: JTAG routed to FPGA, one: CPLD access) |

| nRST | inout | 16 | External Reset. Direction Firmware depends |

| nRST_IN | inout | 4 | External Reset. Direction Firmware depends |

| PS_POR_B | in | 14 | Reset from Watchdog to FPGA |

| TCK | in | 30 | JTAG from B2B |

| TDI | in | 32 | JTAG from B2B |

| TDO | out | 1 | JTAG to B2B |

| TMS | in | 29 | JTAG from B2B |

| WD_EN | in | 21 | Watchdog PL I/O |

| WD_HIT | in | 20 | Watchdog PL I/O |

| WDI | out | 17 | Watchdog trigger to external Watchdog IC |

JTAG signals routed directly through the CPLD to FPGA. Access between CPLD and FPGA can be multiplexed via JTAGSEL (logical one for CPLD, logical zero for FPGA) on J2-111.

3.3V (EN_3V3) is enabled.

Boot Mode Pins routed through the CPLD. MIO2 and MIO3 are connected to GND via resistor.

| Pin | FPGA IO | Value | |||

|---|---|---|---|---|---|

| BOOT1 (BMODE1) | MIO4 | 0 | 1 | 0 | 1 |

| BOOT2 (BMODE2) | MIO5 | 0 | 0 | 1 | 1 |

| Boot Modus | JTAG | not supported | QSPI | SD |

CPLD REV01 to REV02

To get content of older revision got to "Change History" of this page and select older document revision number.

<!-- Generate new entry: 1:add new row below first 2:Copy Page Information Macro(date+user) Preview, Page Information Macro Preview, CPLD/PCB(or update)to the empty row 3.Update Metadate =Page Information Macro Preview+1 --> |

| Date | Document Revision | CPLD Firmware Revision | Supported PCB Revision | Authors | Description |

|---|---|---|---|---|---|

| REV02 | REV02 | Work in progress | ||

| 2017-06-07 | REV02 | REV02 | Initial release | ||

| All |