Template Revision 2.12

- Module: TRM Name always "TE Series Name" +TRM

Example: "TE0728 TRM" - Carrier: TRM Name usually "TEB Series Name" +TRM

Example: "TEB0728 TRM"

|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

----------------------------------------------------------------------- |

Note for Download Link of the Scroll ignore macro: |

Table of Contents

|

Overview

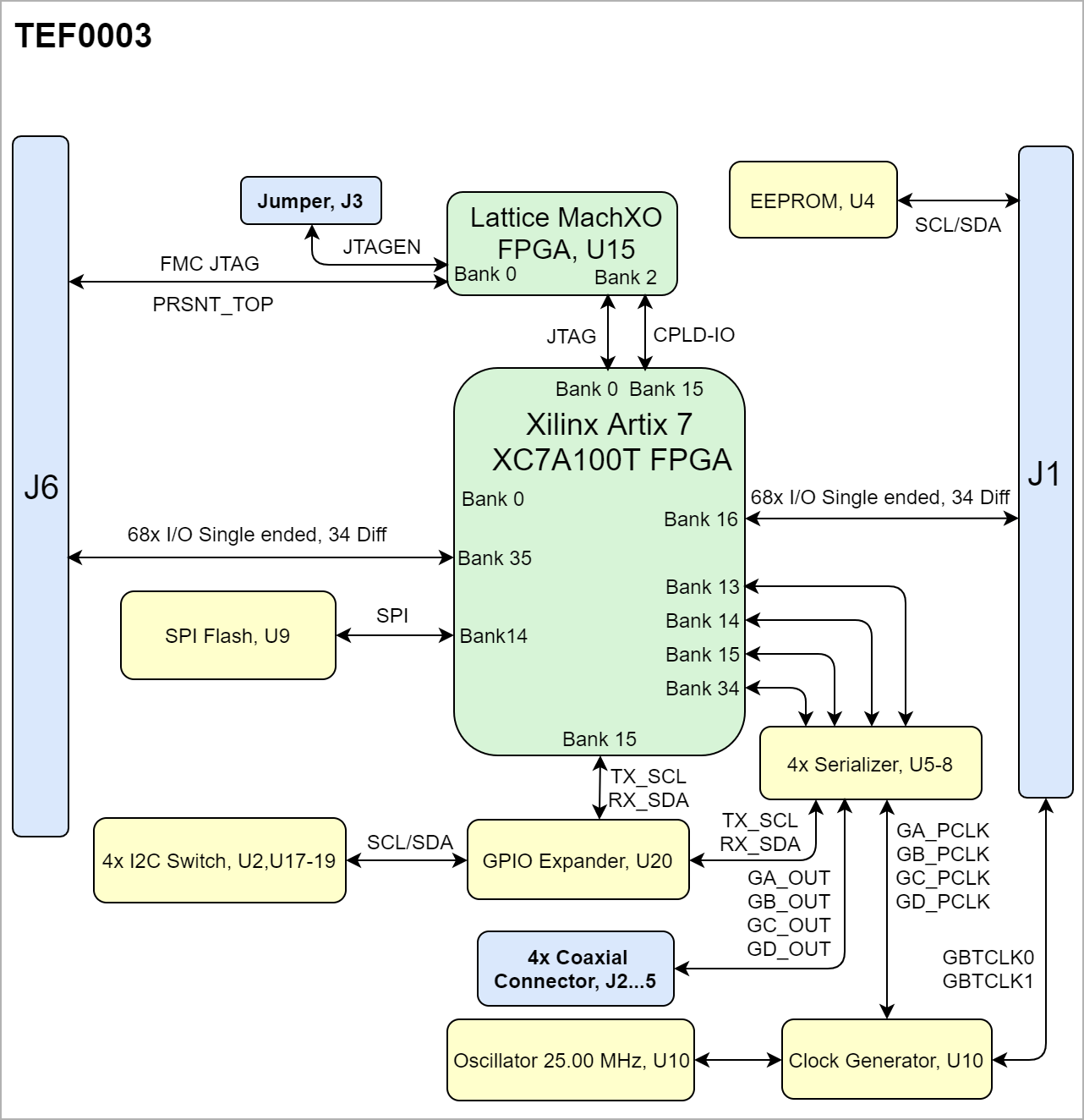

The Trenz Electronic TEF0003 is A FPGA Mezzanine Card (FMC) integrated with a Artix 7.

Refer to http://trenz.org/tef0003-info for the current online version of this manual and other available documentation.

Key Features

Note:

'description: Important components and connector or other Features of the module

→ please sort and indicate assembly options Key Features' must be split into 6 main groups: - FPGA/Module

- Package:

- Speed:

- Temperature:

- RAM/Storage

- On Board

- Interface

- E.g. ETH, USB, B2B, Display port

- Power

- E.g. Input supply voltage

- Dimension

|

- FPGA: Xilinx Artix 7 (XC7A100T)

- Package: FGG484 (Compatible with

- Speed: -1 (Slowest)

- Temperature: Industrial Grade (–40°C to +100°C)

- RAM/Storage:

- 1x NOR SPI FLASH (128M x 4)

- 1x EEPROM (16K x 8)

- On Board:

- 4x Deserializer IC (3.12 Gbps)

- 4x I2C and SMBus I/O Expander

- 1x Programable Clock Generator

- 1x Clock Generator

- Interface:

- 2x VITA 57 SEAM/SEAF Series system

- 4x Coaxial connectors

- Power:

- 4x Voltage Regulators

- 3.3 Supply Voltage

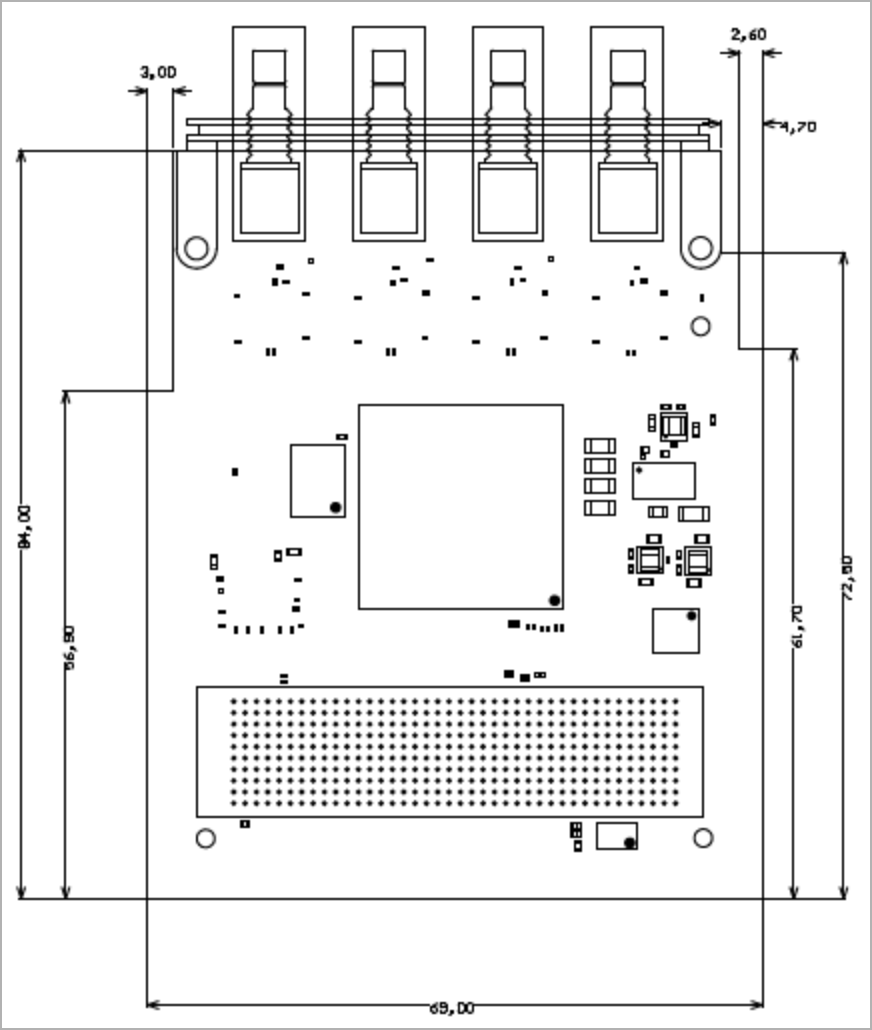

- Dimension: 72 mm x 65 mm

Block Diagram

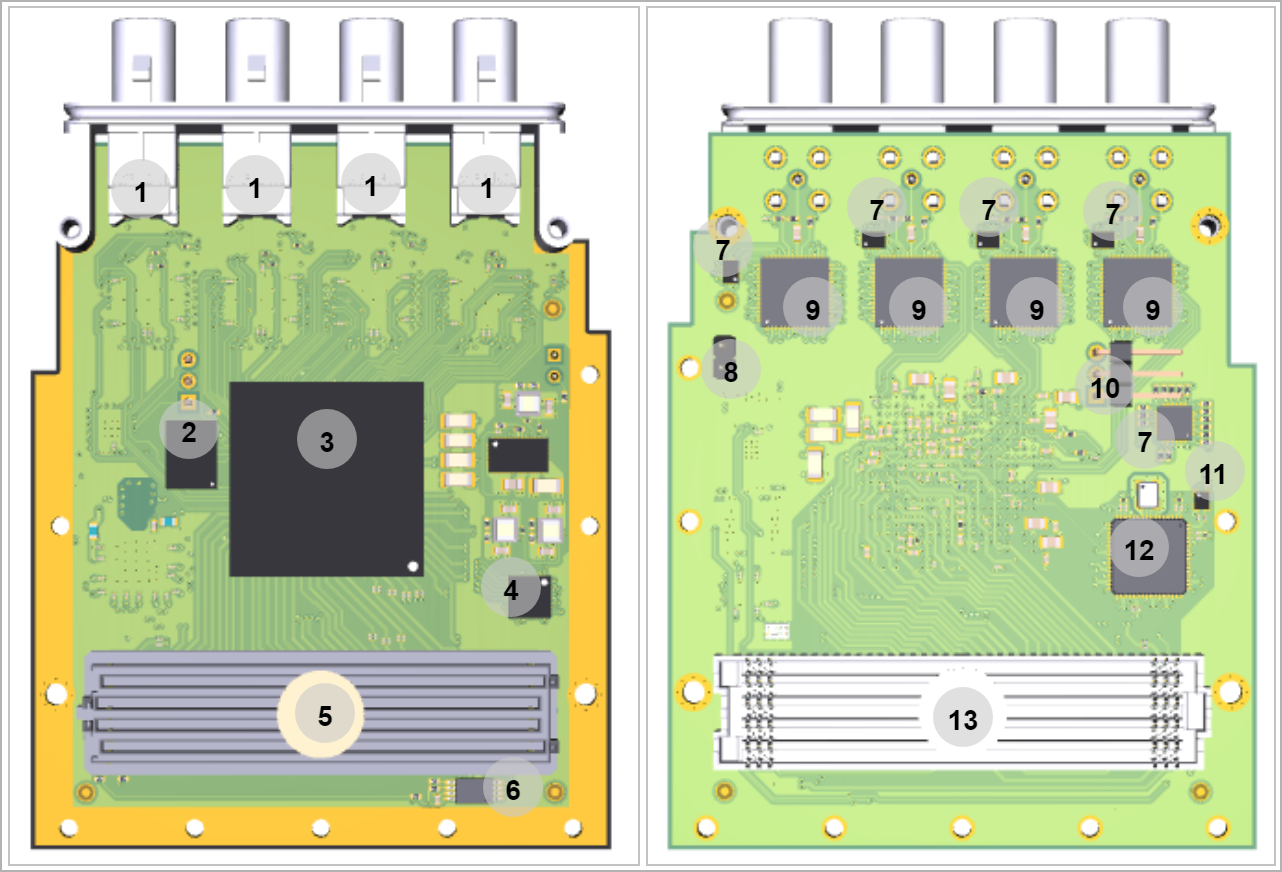

Main Components

Notes : - Picture of the PCB (top and bottom side) with labels of important components

- Add List below

|

- Coaxial Connectors, J2-5

- SPI Flash, U9

- Xilinx Artix 7 FPGA, U1

- Lattice MachXO FPGA, U15

- Vita 57 Connector, J1

- EEPROM, U4

- I2C Switches, U2, U17-20

- Jumper, J7

- Serializer, U5-8

- Connector Header, J8

- Oscillator 25MHz, U11

- Programmable Clock Generator, U10

- Vita 57 Connector, J6

Initial Delivery State

Notes : Only components like EEPROM, QSPI flash and DDR3 can be initialized by default at manufacture. If there is no components which might have initial data ( possible on carrier) you must keep the table empty |

Storage device name | Content | Notes |

|---|

SPI Flash | Not programmed |

| | EEPROM | Not Programmed |

|

|

Configuration Signals

- Overview of Boot Mode, Reset, Enables.

|

MODE Signal State M[2:0] | Boot Mode |

|---|

110 | Master SPI |

|

Signal | B2B | I/O | Note |

|---|

MUX_RESET | - | - |

|

|

Signals, Interfaces and Pins

Notes : - For carrier or stand-alone boards use subsection for every connector type (add designator on description, not on the subsection title), for example:

- For modules which needs carrier use only classes and refer to B2B connector if more than one is used, for example

|

Board to Board (B2B) I/Os

FPGA bank number and number of I/O signals connected to the B2B connector:

| FPGA | FPGA Bank | Connector Designator | I/O Signal Count | Voltage Level | Notes |

|---|

| Artix 7, U1 | 14 | J1 |

|

|

| | 15 | J1 |

|

|

| | 16 | J1 |

|

|

| | 34 | J1 |

|

|

| | Lattice MachXO, U | 0 | J6 |

|

|

| | 1 | J6 |

|

|

| | 2 | J6 |

|

|

| | 3 | J6 |

|

|

|

|

JTAG Interface

JTAG access to the TExxxx SoM through B2B connector JMX.

JTAG Signal | B2B Connector |

|---|

| TMS | J1 | | TDI | J1 | | TDO | J1 | | TCK | J1 | | JTAG_EN | J1 |

|

MIO Pins

you must fill the table below with group of MIOs which are connected to a specific components or peripherals, you do not have to specify pins in B2B, Just mention which B2B is connected to MIOs. The rest is clear in the Schematic. Example: | MIO Pin | Connected to | B2B | Notes |

|---|

| MIO12...14 | SPI_CS , SPI_DQ0... SPI_DQ3 SPI_SCK | J2 | QSPI |

|

| MIO Pin | Connected to | B2B | Notes |

|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

On-board Peripherals

Notes : - add subsection for every component which is important for design, for example:

- Two 100 Mbit Ethernet Transciever PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

Notes : In the on-board peripheral table "chip/Interface" must be linked to the corresponding chapter or subsection |

| Chip/Interface | Designator | Notes |

|---|

| EEPROM |

|

| | Clock Generator |

|

| | Oscillator |

|

| | SPI Flash |

|

|

|

Quad SPI Flash Memory

Notes : Minimum and Maximum density of quad SPI flash must be mentioned for other assembly options. |

| MIO Pin | Schematic | U?? Pin | Notes |

|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EEPROM

| MIO Pin | Schematic | U?? Pin | Notes |

|---|

|

|

|

|

|

|

|

|

|

| MIO Pin | I2C Address | Designator | Notes |

|---|

|

|

|

|

|

Ethernet

| Bank | Signal Name | ETH1 | ETH2 | Signal Description |

|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Clock Sources

| Designator | Description | Frequency | Note |

|---|

| U4 | Oscillator, 25 MHz | MHz |

| | U10 | Programmable Clock Generator | MHz |

|

|

Power and Power-On Sequence

In 'Power and Power-on Sequence' section there are three important digrams which must be drawn: - Power on-sequence

- Power distribution

- Voltage monitoring circuit

|

Power Supply

Power supply with minimum current capability of xx A for system startup is recommended.

Power Consumption

| Power Input Pin | Typical Current |

|---|

| VIN | TBD* |

|

* TBD - To Be Determined

Power Distribution Dependencies

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

|

Power-On Sequence

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

|

Voltage Monitor Circuit

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

|

Power Rails

| Power Rail Name | B2B Connector JM1 Pin | B2B Connector JM2 Pin | B2B Connector JM3 Pin | Direction | Notes |

|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bank Voltages

Board to Board Connectors

- This section is optional and only for modules.

use "include page" macro and link to the general B2B connector page of the module series, For example: 6 x 6 SoM LSHM B2B Connectors

|

Technical Specifications

Absolute Maximum Ratings

| Symbols | Description | Min | Max | Unit |

|---|

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

|

|

|

|

|

|

|

|

Recommended Operating Conditions

Operating temperature range depends also on customer design and cooling solution. Please contact us for options.

| Parameter | Min | Max | Units | Reference Document |

|---|

|

|

| V | See ???? datasheets. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| °C | See Xilinx ???? datasheet. |

|

|

| °C | See Xilinx ???? datasheet. |

|

Physical Dimensions

PCB thickness: 1.54 mm.

Currently Offered Variants

Revision History

Hardware Revision History

| Date | Revision | Changes | Documentation Link |

|---|

| 2017-06-27 | REV01 | Initial Release | REV01 |

|

Hardware revision number can be found on the PCB board together with the module model number separated by the dash.

Document Change History

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

| Date | Revision | Contributor | Description |

|---|

| |

| | -- | all |

| |

|

Disclaimer