Design Name always "TE Series Name" + Design name, for example "TEI0006 Test Board" | Date | Version | Changes | Author |

|---|

| 2023-09-13 | 2.3 | - update to 22.x

- "select COM Port" → Linux command changed

| TD | | 2022-06-15 | 2.2 | - add 'QSPI-Boot mode'

- add 'Get prebuilt boot binaries'

- changed SD-Boot mode chapter

- 'Device Tree' chapter expanded

| TD | | 2022-04-21 | 2.1 | | TD | | 2022-02-28 | 2.0 | - add yocto to

- Overview → Key Features

- Overview → Requirements

- Design Flow

- Launch

- add section 'Software Design - Yocto'

| TD | | 2021-06-15 | 1.2 | - table of content view

- template history

- placed a horizontal separation line under each chapter heading

- replaced <design name> by <project folder>

- update 19.x to 20.x

| JH,TD | | 2020-11-24 | 1.1 | - add fix table of content

- add table size as macro

| JH | | -- | 1.0 | -- | -- |

|

Important General Note: Export PDF to download, if vivado revision is changed! Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro - Use "Scroll Title" macro for pictures and table labels. Figure number must be set manually at the moment (automatically enumeration is planned by scrollPDF)

- ...

|

Overview

Quartus Design with NIOS V/m and software example "simple_socket_server" and "hello_tei0006".

Refer to http://trenz.org/tei0006-info for the current online version of this manual and other available documentation.

Key Features

Notes : - Add basic key futures, which can be tested with the design

|

- Quartus 22.4 Pro

- NIOS V/m

- UART

- ETH

- QSPI flash memory

- DDR3 memory

- User LED

|

Revision History

Notes : - add every update file on the download

- add design changes on description

|

| Date | Quartus | Project Built | Authors | Description |

|---|

| 2024-01-09 | 22.4 Pro | TEI0006-test_board-quartus_22.4.0-20240109135625.zip TEI0006-test_board_noprebuilt-quartus_22.4.0-20240109135551.zip | Thomas Dück | | | 2023-12-04 | 22.4 Pro | TEI0006-test_board_noprebuilt-quartus_22.4.0-20231204134534.zip TEI0006-test_board-quartus_22.4.0-20231204134455.zip | Thomas Dück | - update to Quartus Prime Pro 22.4

- TE scripts update

- new assembly variants

| | 2023-04-13 | 20.4 Pro | TEI0006-test_board_noprebuilt-quartus_20.4.0-20230411171022.zip TEI0006-test_board-quartus_20.4.0-20230411171231.zip | Thomas Dück | - change "Serial Flash Controller II" IP Core to "QUAD SPI Controller II" IP Core

- bugfix offset value of hex file

| | 2021-06-15 | 20.4 Pro | TEI0006-test_board_noprebuilt-quartus_20.4.0-20210615142627.zip TEI0006-test_board-quartus_20.4.0-20210615142455.zip | Thomas Dück | - update to Quartus Prime Pro 20.4

- TE scripts update

- new assembly variants

| | 2020-10-19 | 19.4 Pro | TEI0006-test_board_noprebuilt-quartus_19.4.0-20201019101920.zip TEI0006-test_board-quartus_19.4.0-20201019101840.zip | Thomas Dück | | | 2020-05-13 | 19.4 Pro | TEI0006-test_board_noprebuilt-quartus_19.4.0-20200513124953.zip TEI0006-test_board-quartus_19.4.0-20200513125247.zip | Thomas Dück | | | 2020-03-09 | 19.4 Pro | TEI0006-test_board-quartus_19.4-20200309134933.zip

TEI0006-test_board_noprebuilt-quartus_19.4-20200309135555.zip | Thomas Dück | |

|

Release Notes and Know Issues

Notes :- add known Design issues and general notes for the current revision

- do not delete known issue, add fixed version time stamp if issue fixed

|

| Issues | Description | Workaround | To be fixed version |

|---|

| No known issues | --- | --- | --- |

|

Requirements

Software

Notes : - list of software which was used to generate the design

|

| Software | Version | Note |

|---|

| Quartus Prime Pro | 22.4 | Nios V/m license is needed. For more information see: Intel Nios V Processors | | Ashling RiscFree IDE for Intel FPGAs | 22.4 | needed |

|

Hardware

Notes : - list of software which was used to generate the design

- mark the module and carrier board, which was used tested with an *

|

Complete List is available on <project folder>/board_files/*_devices.csv

Design supports following modules:

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | Others | Notes |

|---|

| TEI0006-03-220-5I* | 220_5I_2GB | REV03|REV02|REV01 | 2GB | 128MB | -- | -- | | TEI0006-03-APC13-R | APC13R | REV03 | 128MB | 128MB | -- | without ETH PHY | | TEI0006-03-ANC13-R | ANC13R | REV03 | 128MB | 128MB | -- | without ETH PHY | | TEI0006-03-ALC13-R | ALC13R | REV03 | 128MB | 128MB | -- | without ETH PHY | | TEI0006-03-ALC13 | ALC13 | REV03 | 128MB | 128MB | -- | -- | | TEI0006-04-ALC13A | ALC13 | REV04 | 128MB | 128MB | -- | -- | | TEI0006-04-ALE13A | ALE13 | REV04 | 128MB | 128MB | -- | -- | | TEI0006-04-ANE13A | ANE13 | REV04 | 128MB | 128MB | -- | -- | | TEI0006-04-APE23A | APE23 | REV04 | 2GB | 128MB | -- | -- | | TEI0006-04-API23A | API23 | REV04 | 2GB | 128MB | -- | -- | | TEI0006-04-S004 | API23R | REV04 | 2GB | 128MB | -- | without ETH PHY | | TEI0006-04-S005 | APE23 | REV04 | 2GB | 128MB | -- | -- | | TEI0006-04-S006 | BPI23 | REV04 | 2GB | 128MB | -- | -- | | TEI0006-04-S007 | APE23R | REV04 | 2GB | 128MB | -- | without ETH PHY |

*used as reference

|

Design supports following carriers:

| Carrier Model | Notes |

|---|

| TEIB0006* |

|

*used as reference |

Additional HW Requirements:

| Additional Hardware | Notes |

|---|

| USB cable for JTAG/UART | Check Carrier Board and Programmer for correct type | | RJ45 ethernet cable | connect carrier board to network |

|

Content

For general structure and of the reference design, see Project Delivery - Intel devices

Design Sources

| Type | Location | Notes |

|---|

| Quartus | <project folder>/source_files/quartus <project folder>/source_files/<Board Part Short Name>/quartus | Quartus project will be generated by TE Scripts optional, source files for specific assembly variants | | Software | <project folder>/source_files/software | Additional software will be generated by TE Scripts |

|

Prebuilt

Notes : - prebuilt files

- Template Table:

File | File-Extension | Description |

|---|

| SOPC Information File | *.sopcinfo | File with description of the .qsys file to create software for the target hardware | | SRAM Object File | *.sof | Ram configuration file | | Programmer Object File | *.pof | FPGA configuration file | | JTAG Indirect Configuration file | *.jic | Flash configuration file | | Raw binary file | *.rbf | FPGA configuration file | | Diverse Reports | --- | Report files in different formats | | Software-Application-File | *.elf | Software application for Nios II/Nios V processor system | Device Tree | *.dtb | Device tree blob | | SFP-File | *.sfp | Boot image with SPL (Secondary Program Loader) | | BIN-File | *.bin | Image with linux kernel and ram disk | | CONF-File | *.conf | Boot configuration file (extlinux.conf) | | Yocto linux image | *.wic | Linux image for SD card |

|

|

File | File-Extension | Description |

|---|

| SOPC Information File | *.sopcinfo | File with description of the .qsys file to create software for the target hardware | | SRAM Object File | *.sof | Ram configuration file | | JTAG indirect configuration file | *.jic | Flash configuration file | | Diverse Reports | --- | Report files in different formats | | Software-Application-File | *.elf | Software application for NIOS II processor system |

|

Download

Reference Design is only usable with the specified Quartus version. Do never use different versions of Quartus software for the same project.

Reference Design is available on:

Design Flow

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first launch. |

Trenz Electronic provides a tcl based built environment based on Quartus Design Flow.

See also:

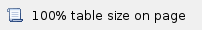

The Trenz Electronic FPGA Reference Designs are TCL-script based projects. To create a project, open a project or program a device execute "create_project_win.cmd" on Windows OS and "create_project_linux.sh" on Linux OS.

TE Scripts are only needed to generate the quartus project, all other additional steps are optional and can also executed by Intel Quartus/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery - Intel devices → Currently limitations of functionality

- Open create_project_win.cmd/create_project_linux.sh:

- Select Board in "Board selection"

- Click on "Create project" button to create project

- (optional for manual changes) Select correct quartus installation path in "<project folder>/settings/design_basic_settings.tcl"

Launch

Note: - Programming and Startup procedure

|

Programming

Check Module and Carrier TRMs for proper HW configuration before you try any design. Reference Design is also available with prebuilt files. It's recommended to use TE prebuilt files for first launch. |

Get prebuilt boot binaries

- Run create_project_win.cmd/create_project_linux.sh

- Select a Module in 'Board selection'

- Click on the 'Export prebuilt files' button

- Folder <project folder>/_binaries_<Article Name> with subfolder boot_linux will be generated and opened

QSPI

- Connect JTAG and power on carrier with module

- Open create_project_win.cmd/create_project_linux.sh

- Select correct board in "Board selection"

- Click on "Program device" button

- if prebuilt files are available: select "Program prebuilt file"

- using own generated programming file: select "Program other file" and click on "Browse ..." to open own generated programming file

- (optional) click on "Open programmer GUI" to program device with Quartus programmer GUI

- Click on "Start program device" button

JTAG

Not used on this Example.

Usage

- Prepare HW like described on section Programming

- Connect UART USB (most cases same as JTAG)

- Connect your board to the network

- Power on PCB

UART

- Open Serial Console (e.g. PuTTY)

- select COM Port

Win OS: see device manager Linux OS: see ls -l dev/serial/by-id (UART is *USB1) |

- Speed: 115200

- Press reset button

- Console output depends on used Software project, see Software Design - SDK#Application

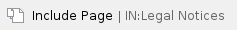

System Design - Quartus

Note: - Description of Block Design - Project, Block Design - Platform Desginer, ... Block Design Pictures from Export...

|

Block Design

The block design may differ depending on the assembly variant.

Software Design - SDK

Application

---------------------------------------------------------- General Example: hello_tei0006 Hello TEI0006 is a Hello World example as endless loop instead of one console output. |

Used software project depends on board assembly variant. Template location: <project folder>/source_files/software/

hello_tei0006

Hello TEI0006 is a Hello World example as endless loop instead of one console output.

simple_socket_server

Software example "Simple Socket Server" from eclipse (modified source files for TEI0006 board).

- If DHCP Server is not available:

- Open software project in sdk gui (e.g. Ashling RiscFree IDE for Intel FPGAs 22.4) and set in the main.c file the varaibles:

- .use_dhcp = !DEF_TRUE

- .ipv4_addr_str = <your static IP address>

- .ipv4_gateway_str =<your gateway>

- Rebuild the software project and download the *.elf file to the device.

- Open the command shell and enter "telnet <ip_address> 80" to connect to the simple socket server

Appx. A: Change History and Legal Notices

Document Change History

To get content of older revision got to "Change History" of this page and select older document revision number.

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

| Date | Document Revision | Authors | Description |

|---|

| | | - update to Quartus Prime Pro 22.4

- new assembly variants

| | v.12 | Thomas Dück | | | 2021-07-26 | v.10 | Thomas Dück | - update to Quartus Prime Pro 20.4

- new assembly variants

- document style update

- script update

| | 2020-10-19 | v.6 | Thomas Dück | | | 2020-05-13 | v.5 | Thomas Dück | | | 2020-03-18 | v.4 | Thomas Dück | | | -- | all | | -- |

|

Legal Notices