Template Revision 1.0 - on construction Design Name always "TE Series Name" + Design name, for example "TEI0001 Test Board" |

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

Important General Note: Export PDF to download, if vivado revision is changed! Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro - Use "Scroll Title" macro for pictures and table labels. Figure number must be set manually at the moment (automatically enumeration is planned by scrollPDF)

- ...

|

Table of contents

|

Overview

Refer to http://trenz.org/tei0006-info for the current online version of this manual and other available documentation.

Key Features

Notes : - Add basic key futures, which can be tested with the design

|

- Quartus 19.4 Pro

- NIOS II

- UART

- ETH

- QSPI flash memory

- DDR3L memory

- User LED

|

Revision History

Notes : - add every update file on the download

- add design changes on description

|

| Date | Quartus | Project Built | Authors | Description |

|---|

| 2020-03-09 | 19.4 Pro | TEI0006-test_board-quartus_19.4-20200309134933.zip

TEI0006-test_board_noprebuilt-quartus_19.4-20200309135555.zip | Thomas Dück | |

|

Release Notes and Know Issues

Notes :- add known Design issues and general notes for the current revision

- do not delete known issue, add fixed version time stamp if issue fixed

|

| Issues | Description | Workaround | To be fixed version |

|---|

| No known issues | --- | --- | --- |

|

Requirements

Software

Notes : - list of software which was used to generate the design

|

| Software | Version | Note |

|---|

| Quartus Prime Pro | 19.4 | needed | | NIOS II SBT for Eclipse | --- | needed |

|

Hardware

Notes : - list of software which was used to generate the design

|

Complete List is available on <design name>/board_files/*_devices.csv

Design supports following modules:

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | EMMC | Others | Notes |

|---|

| TEI0006-02-220-5I | 220-5I-1GB | REV01, REV02 | 1 GB | 128 MB | NA | NA | NA |

|

Design supports following carriers:

| Carrier Model | Notes |

|---|

| TEIB0006 |

|

|

Additional HW Requirements:

| Additional Hardware | Notes |

|---|

| USB Cable for JTAG/UART | Check Carrier Board and Programmer for correct type | | RJ45 ethernet Cable | connect carrier board to network |

|

Content

For general structure and of the reference design, see Project Delivery - Intel devices

Design Sources

| Type | Location | Notes |

|---|

| Quartus | <design name>/source_files/quartus | Quartus Project will be generated by TE Scripts | | Software | <design name>/source_files/software | Additional Software will be generated by TE Scripts |

|

Prebuilt

Notes : - prebuilt files

- Template Table:

File | File-Extension | Description |

|---|

| BIF-File | *.bif | File with description to generate Bin-File | | BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | | BIT-File | *.bit | FPGA (PL Part) Configuration File | | DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | Debian SD-Image | *.img | Debian Image for SD-Card | | Diverse Reports | --- | Report files in different formats | | Hardware-Platform-Specification-Files | *.xsa | Exported Vivado Hardware Specification for Vitis and PetaLinux | | LabTools Project-File | *.lpr | Vivado Labtools Project File | MCS-File | *.mcs | Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) | MMI-File | *.mmi | File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) | | OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | | Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems | SREC-File | *.srec | Converted Software Application for MicroBlaze Processor Systems |

|

|

File | File-Extension | Description |

|---|

| SOPC Information File | *.sopcinfo | File with description of the .qsys file to create software for the target hardware | | SRAM Object File | *.sof | Ram Configuration File | | JTAG indirect configuration file | *.jic | Flash configuration File | | Diverse Reports | --- | Report files in different formats | | Software-Application-File | *.elf | Software Application for NIOS II processor system |

|

Download

Reference Design is only usable with the specified Quartus version. Do never use different Versions of Quartus software for the same project.

Reference Design is available on:

Design Flow

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

Trenz Electronic provides a tcl based built environment based on Quartus Design Flow.

See also:

The Trenz Electronic FPGA Reference Designs are TCL-script based project. To create project, open project or program device execute "create_project_win.cmd" on Windows OS and "create_project_linux.sh" on Linux OS.

TE Scripts are only needed to generate the quartus project, all other additional steps are optional and can also executed by Intel Quartus/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- Open create_project_win.cmd/create_project_linux.sh and follow instructions in "Messages" section:

- Select board in "Board selection" section

- Click on "Create project" button to create project

- (optional for manual changes) Select correct Quartus install path on "design_basic_settings.cmd"

Launch

Note: - Programming and Startup procedure

|

Programming

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

QSPI

- Connect JTAG and power on carrier with module

- Open "create_project_win.cmd/create_project_linux.sh"

- select correct Board in "Board selection" section

- Click on "Program device" button

- (if prebuilt files are available) select "Program prebuilt file" and click on "Start program device"

- select "Program other file" and click on "Browse ..." to open own generated programming file

- (optional) click on "Open programmer GUI" to program device with Quartus programmer GUI

- Click on "Start program device"

JTAG

Not used on this Example.

Usage

- Prepare HW like described on section TEI0006 Reference Design#Programming

- Connect UART USB (most cases same as JTAG)

- Power On PCB

UART

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty

- Select "Implicit CR in every LF" in category "Terminal"

- Simple Socket Server is starting up. Follow instructions on shell.

- If dhcp server is not available: open sdk project in sdk gui and change predefined IP address in simple_socket_server.h, build software project and download *.elf file to device.

- Connect your board to the network

- Open command shell and enter "telnet <ip_address> 30"

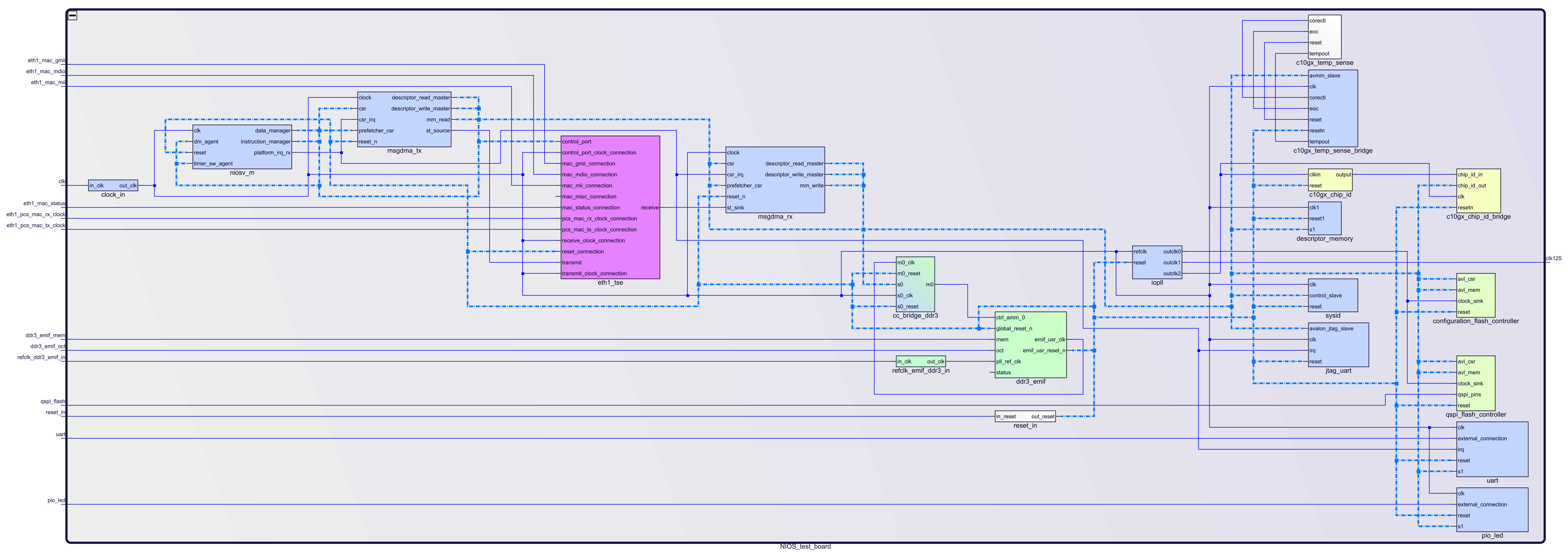

System Design - Quartus

Block Design

Software Design - SDK

Application

simple_socket_server

Software example "Simple Socket Server" from SDK software eclipse (modified source files for TEI0006 board).

Template location: <basefolder>/source_files/software/simple_socket_server

Document Change History

To get content of older revision got to "Change History" of this page and select older document revision number.

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

| Date | Document Revision | Authors | Description |

|---|

| | | | | -- | all | | -- |

|

Legal Notices