# **TE USB FX2 module SPI bus**

Host Computer's Software Connection (with SPI Flash) Available

• All SPI Flash Commands (through FLASH\_WRITE\_COMMAND command)

• Some USB FX2 API Commands:

• FLASH\_ERASE command

• FLASH\_READ command

• FLASH\_WRITE command

### • FLASH\_WRITE\_COMMAND command

USB FX2 API Commands to connect host computer's software with FPGA through SPI are currently not available; the connection can be only established only indirectly and for a single aim. The FPGA is configured by SPI Flash content when the FPGA is subject to power on or reset.

# Physical Interfaces Available

| TE Module SPI bus | B2B connection is available? | SPI Header connection is available? |

|-------------------|------------------------------|-------------------------------------|

| TE0300 SPI bus    | ⊗                            |                                     |

| TE0320 SPI bus    | <                            | 8                                   |

| TE0630 SPI bus    | 8                            | 8                                   |

SPI Physical Interfcaces Available

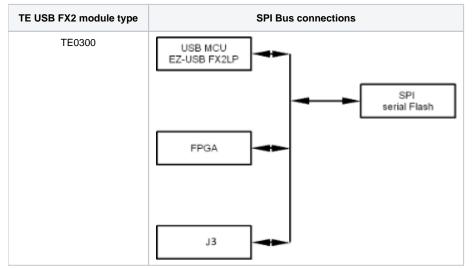

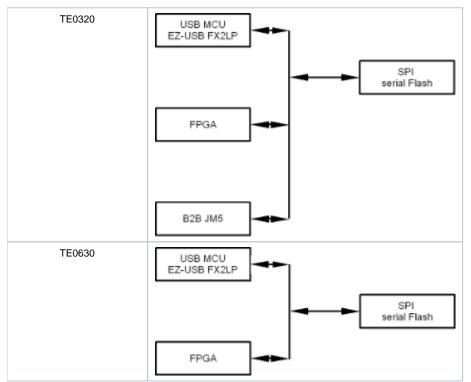

# **SPI Bus connections**

SPI Flash and FPGA connection; SPI Flash and USB FX2 microcontroller

# FPGA SPI Configuration Interface with FX2 microcontroller and SPI Flash

FPGA SPI Configuration Interface (DATA) Pins:

- SPI/S, SPI/C, SPI\_D, SPI\_Q (aka CSO\_B, CCLK, MOSI/DI, MISO/DO aka PD[7:4]) for TE0300 and TE0320

- CSO\_B, CCLK, MOSI/DI, MISO/DO, MISO3 and MISO2 (aka PD[7:4] and MISO[3:2]) for TE0630

FPGA SPI Configuration Interface (CONTROL/STATUS) Pins: PD[3:1] for every TE USB FX2 module:

• INIT\_B, DONE, FX2\_PROG\_B aka PROG\_B (Spartan-3E and Spartan-3A) or PROGRAM\_B (Spartan-6).

FX2\_PS\_EN (PD0) is used to control the signal PS\_EN (if the switch FX2\_ON is set to on), so it is not really part of the SPI Configuration Interface. The signal PS\_EN could enable/disable some power rails.

# FPGA SPI Configuration Interface (DATA) Pins

## TE0300 (Spartan-3E) and TE0320 (Spartan-3A) module

This interface section is common to TE0300 (Spartan-3E) and TE0320 (Spartan-3A) module.

Only SPI\_buswidth (for SPI Flash memory) = 1 is supported by TE0300 and TE0320 module.

| Pin Name<br>Schematic | Pin Name<br>FPGA<br>FPGA Direction | Pin Name FX2<br>FX2 direction | Description | During Configuration | After Configuration |

|-----------------------|------------------------------------|-------------------------------|-------------|----------------------|---------------------|

|-----------------------|------------------------------------|-------------------------------|-------------|----------------------|---------------------|

| SPI/S | CSO_B of Spartan-3<br>Output | PD4<br>Output when<br>the FPGA is<br>powerd off by<br>spi functions <sup>(1)</sup> | Master SPI Chip Select Output<br>Active Low.<br>Connect to the SPI Flash PROM's<br>Slave Select input.<br>Chip select: When the S# input<br>signal is HIGH, the device is<br>deselected<br>and DQ1 is at HIGH impedance.<br>Unless an internal PROGRAM,<br>ERASE,<br>or WRITE STATUS REGISTER cycle<br>is in progress, the device will be in<br>the standby power mode (not the<br>DEEP POWERDOWN mode).<br>Driving S# LOW enables the device,<br>placing it in the active power mode.<br>After power-up, a falling edge on S#<br>is required prior to the start of any<br>command.     | If HSWAP<br>or PUDC_B =1,<br>connect this signal<br>to a 4.7 k<br>pull-up resistor<br>to 3.3V.                 | Drive CSO_B High after<br>configuration to disable<br>the SPI Flash and reclaim<br>the MOSI, DIN, and<br>CCLK pins. Optionally,<br>re-use this pin and MOSI,<br>DIN, and CCLK to<br>continue communicating<br>with SPI Flash. |

|-------|------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI/C | CCLK<br>Output               | PD5<br>Output when<br>the FPGA is<br>powerd off by<br>spi functions <sup>(1)</sup> | Configuration Clock. Generated by<br>FPGA internal oscillator.<br>Connect to the SPI Flash PROM's<br>Slave Clock input.<br>Frequency controlled by ConfigRate<br>bitstream generator option.<br>If CCLK PCB trace is long or has<br>multiple connections, terminate this<br>output to maintain signal integrity.<br>Clock: The C input signal provides the<br>timing of the serial interface.<br>Commands, addresses, or data<br>present<br>at serial data input (DQ0) is latched on<br>the rising edge of the serial clock (C).<br>Data on DQ1 changes after the falling<br>edge of C. | Drives SPI Flash<br>PROM's clock input.                                                                        | User I/O. Drive High or<br>Low if not used.                                                                                                                                                                                   |

| SPI_D | MOSI<br>Output               | PD6<br>Output when<br>the FPGA is<br>powerd off by<br>spi functions <sup>(1)</sup> | Master SPI Serial Data Output<br>Connect<br>to the SPI Flash PROM's Slave<br>Data Input pin.<br>Serial data: The DQ0 input signal is<br>used to transfer data serially into the<br>SPI Flash device.<br>It receives commands, addresses,<br>and the data to be programmed.<br>Values are latched on the rising edge<br>of the serial clock (C).                                                                                                                                                                                                                                         | FPGA sends<br>SPI Flash memory<br>read commands<br>and starting address<br>to the PROM's<br>serial data input. | User I/O                                                                                                                                                                                                                      |

| SPI_Q | DIN<br>Input                 | PD7<br>Input, by default <sup>(2)</sup>                                            | Master SPI Serial Data Input Connect<br>to the SPI Flash PROM's Slave Data<br>Output pin.<br>Serial data: The DQ1 output signal is<br>used to transfer data serially out of the<br>SPI Flash device.<br>Data is shifted out on the falling edge<br>of the serial clock (C).                                                                                                                                                                                                                                                                                                             | FPGA receives serial<br>data from SPI Falsh<br>PROM's serial data<br>output.                                   | User I/O                                                                                                                                                                                                                      |

FPGA SPI Configuration Interface (DATA) Pins: PD[7:4] for TE0300 and TE0320 module

## TE0630 (Spartan-6) module

This interface section is used only by TE0630 (Spartan-6) module.

SPI\_buswidth (for SPI Flash memory) = 1 (single mode), 2 (dual mode) or 4 (quad mode) are supported by TE0630 module.

ISE procedure, for example.

1. Open TE USB FX2 project

Generate Programming File -> Process Properties

Configuration options "-g SPI\_buswidth" = 1,2 or 4 then Apply and OK

Run "Generate programming file"

Open iMPACT and generate msc from bit

6. Program mcs to Flash in x1 (single), x2 (dual) or x4 (quad) mode

| Pin Name<br>Schematic               | Pin Name<br>FPGA<br>FPGA Direction       | Pin Name FX2<br>FX2 direction                                                      | Description                                                                                                                                                                                                  | During Configuration                                                                                     | After Configuration                                                                                                                                                                                                                          |

|-------------------------------------|------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSO_B                               | CSO_B<br>Output                          | PD4<br>Output when<br>the FPGA is<br>powerd off by<br>spi functions <sup>(1)</sup> | Master SPI Chip Select Output.<br>Active Low. Connect to the SPI<br>Flash PROM's Slave Select input                                                                                                          | If HSWAPEN_B =1,<br>connect this signal to V <sub>CCO</sub><br>through pull-up resistor<br>externally.   | User I/O.<br>Drive CSO_B High<br>after configuration<br>to disable the SPI<br>Flash and reclaim<br>MOSI, DIN, and<br>CCLK pins.<br>Optionally reuse<br>this pin,<br>MOSI, DIN,<br>and CCLK<br>to continue<br>communicating<br>with SPI flash |

| CCLK                                | CCLK<br>Output                           | PD5<br>Output when<br>the FPGA is<br>powerd off by<br>spi functions <sup>(1)</sup> | Configuration clock source<br>for all configuration modes<br>except JTAG.<br>Generated by FPGA<br>internal oscillator.<br>Connect to the SPI flash<br>PROM's Slave Clock input.                              | Drive SPI Flash's clock input.                                                                           | User I/O.<br>Drive High<br>or Low<br>if not used.                                                                                                                                                                                            |

| MOSI/DI                             | MOSI/DI<br>Output/Input<br>Bidirectional | PD6<br>Output when<br>the FPGA is<br>powerd off by<br>spi functions <sup>(1)</sup> | Master FPGA Serial Data Output<br>and<br>Master FPGA Serial Data Input.<br>Connect to the SPI Flash PROM's<br>Slave Data Input pin.<br>It is used in x1 (single mode),<br>x2 (dual mode) and x4 (quad) mode. | FPGA sends SPI flash<br>memory read commands<br>and starting address to the<br>PROM's serial data input. | User I/O                                                                                                                                                                                                                                     |

| MISO/DO                             | MISO/DO<br>Input                         | PD7<br>Input, by default <sup>(2)</sup>                                            | Master FPGA Serial Data Input<br>and Slave SPI flash output.<br>Connect to the SPI Flash<br>PROM's Slave Data Output pin.<br>It is used in x2 (dual mode) and<br>x4 (quad) mode.                             | FPGA receives serial data<br>from PROM's serial data<br>output.                                          | User I/O                                                                                                                                                                                                                                     |

| MISO2 and<br>MISO3 aka<br>MISO[3:2] | MISO3 and<br>MISO2<br>Input              | NOT CONNECTED                                                                      | Master FPGA Serial Data Input<br>and Slave SPI data output.<br>They are used in x4 (quad) mode.                                                                                                              | Used only when using the fast-read quad output command.                                                  | User I/O                                                                                                                                                                                                                                     |

FPGA SPI Configuration Interface (DATA) Pins: PD[7:4] and MISO[3:2] for TE0630

# FPGA SPI Configuration Interface (CONTROL/STATUS) Pins

This interface section is common to all TE USB FX2 modules (TE0300, TE0320, TE0630): FPGA Spartan-3E, Spartan-3A and Spartan-6.

FX2\_PS\_EN is used to control the signal PS\_EN (if the switch FX2\_ON is set to on), so it is not really part of the SPI Configuration Interface.

| Pin Name<br>Schematic | Pin Name<br>FPGA<br>FPGA Direction | Pin Name<br>FX2<br>FX2 direction | Description | During Configuration | After Configuration |

|-----------------------|------------------------------------|----------------------------------|-------------|----------------------|---------------------|

|-----------------------|------------------------------------|----------------------------------|-------------|----------------------|---------------------|

| FX2_PS_EN  | NOT                                                                                                                                                 | PD0<br>Bidirectional<br>Input/Output <sup>(3)</sup> | Control of signal PS_EN<br>if the switch FX2_ON is set to on.<br>Some power rails are controlled<br>by the USB FX2 microcontroller.<br>At start-up, the FX2 microcontroller<br>switches off some power rails and<br>starts up the module in low-power<br>mode.<br>After enumeration,<br>the FX2 microcontroller firmware<br>enables (switches on) the power<br>rails previously disabled, if enough<br>current is available<br>from the USB bus.<br>See Power Rails Configuration:<br>• TE0300: S3<br>• TE0320: S2<br>• TE0630: S1B | If the switch FX2_ON<br>is set to on, FX2_PS_EN<br>should be High to allow<br>configuration to start.                                                                                                                                                                                                                                                                                                                                                                    | If the switch FX2_ON is<br>set to on, FX2_PS_EN<br>should be High to allow<br>the various components<br>of TE USB FX2<br>module to work.                                                                                                                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FX2_PROG_B | PROGRAM_B<br>(TE0630's<br>Spartan 6)<br>PROG_B<br>(TE0300's<br>Spartan 3E)<br>(TE0320's<br>Spartan 3A)<br>Input                                     | PD1<br>Bidirectional<br>Input/Output <sup>(3)</sup> | Program FPGA. Active Low.<br>Active-Low asynchronous full-chip<br>reset.<br>When asserted Low for 500 ns<br>or longer, forces the FPGA to<br>restart its configuration process<br>by clearing configuration memory<br>and resetting the DONE and<br>INIT_B pins after FX2_PROG_B<br>returns High.                                                                                                                                                                                                                                   | Must be High to allow<br>configuration to start.                                                                                                                                                                                                                                                                                                                                                                                                                         | Drive FX2_PROG_B Low<br>and release to reprogram<br>FPGA.<br>Hold FX2_PROG_B to<br>force<br>the FPGA I/O pins into<br>High-Z, allowing direct<br>programming<br>access to SPI flash<br>PROM pins.                                                                                                        |

| DONE       | DONE<br>Bidirectional I/O,<br>Open-Drain,<br>or Active<br>Use a pull-up<br>resistor (330)<br>on DONE <sup>(4)</sup> .<br>pull-up.<br>See AR# 35002. | PD2<br>Input,<br>by default <sup>(2)</sup>          | Dedicated Active-High signal<br>indicating configuration is complete:<br>• 0 = FPGA not configured<br>• 1 = FPGA configured<br>Refer to the BitGen section of<br>UG628, Command Line Tools<br>User Guide for software settings.                                                                                                                                                                                                                                                                                                     | See FPGA configuration<br>process successfully<br>completes (DONE PIN)<br>page.                                                                                                                                                                                                                                                                                                                                                                                          | The FX2 microcontroller's<br>firwmare is able to read the<br>DONE PIN status from<br>PD2 pin (IOD2) and the<br>host<br>computer's SW could<br>obtain the current value<br>using<br>READ_STATUS command.<br>DONE PIN status can be<br>read from reply[4] (=<br>EP1INBUF[4] = sts_booting<br>= FPGA_DONE). |

| INIT_B     | INIT_B<br>Open-drain<br>bidirectional<br>I/O.<br>Use a pull-up<br>resistor (4.7k)<br>on INIT_B <sup>(4)</sup> .<br>See AR# 35002.                   | PD3<br>Input,<br>by default <sup>(2)</sup>          | See AR# 39582 and AR# 35002<br>Initialization Indicator. Active Low.<br>Goes Low at start of configuration<br>during Initialization memory<br>clearing process. Released at end<br>ofmemory clearing, when mode<br>select pins are sampled.<br>The INIT pin does not have a rise<br>time requirement and is used to<br>signal the start of configuration as<br>well as a CRC, and can also be<br>used as User-IO post configuration.                                                                                                | Active during configuration.<br>Before the Mode pins are<br>sampled, INIT_B is an input<br>that can be held<br>Low to delay configuration.<br>If SPI Flash PROM requires<br>more than 2 ms to awake<br>after powering<br>on,hold INIT_B Low until<br>PROM is ready.<br>After the Mode pins are<br>sampled, INIT_B is an<br>open-drain active-Low<br>output<br>indicating whether a CRC<br>error occurred during<br>configuration:<br>• 0= CRC error<br>• 1= No CRC error | User I/O. If unused in the<br>application, drive<br>INIT_B High to avoid a<br>floating value.<br>Dual-Purpose:<br>if User I/O if POST_CRC<br>is not enabled.                                                                                                                                             |

|            |                                                                                                                                                     | (00)/700/                                           | STATUS) Pine: PD[3:0] for a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                        |

FPGA SPI Configuration Interface (CONTROL/STATUS) Pins: PD[3:0] for every TE USB FX2 module

Only the status of these PD2 pin (FPGA\_DONE) could be retrieved using the READ\_STATUS command. If the user desire to retrieve the status of the other pins as well, he/she should modify the firmware to add another FW API similar to READ\_STATUS command. Theoretically the user /developer should add another case in the switch construction inside the function ep1\_pool(void) (described in te\_api.c).

## Legend/Explanations/References of previous tables

(1) In various function of reference firmware code spi.c.

### spi.c, TE USB FX2 firmware v3.02

```

OED = 0x73; // 0b01110001; => PD6,PD5,PD4,PD0 pins output enabled;

FPGA_POWER = 0; // power off fpga

```

(2) For default direction of pin, see table 10 ("FX2LP Pin Descriptions") of the document "EZ-USB® FX2LP<sup>TM</sup> USB Microcontroller High-Speed USB Peripheral Controller" (link).

(3) In the reference firmware code fw.c.

### fw.c, TE USB FX2 firmware v3.02

```

IOD = 0x03; // Enable FX2_PS_EN and FX2_PROG_B as inputs => // 0b00000011; => PD1,PD0 pins input enabled;

OED = 0x03; // Enable FX2_PS_EN and FX2_PROG_B as outputs => // 0b00000011; => PD1,PD0 pins output enabled;

```

(4) The Xilinx Official Recommendation will still stand as using a 4.7k pull-up on INIT as the device characteristics in regards to INIT have not changed from other families. The reasoning behind the recommendation for a stronger pull-up on INIT was because INIT is a User-IO after configuration. If the INIT pin is not used in the design it will be unused, and unused pins by default have a pull-down. The voltage divider created between the pull-down and the pull-up on INIT might cause the voltage to drop lower than Vihmin at Vcco for a downstream device. For this reason, using a stronger pull-up can help ensure Vihmin is met on other devices connected to the pin. The INIT pin can also be included in the user logic and driven or tri-stated accordingly.

The DONE pin is an open drain driver which is released during the Start-Up sequence at the end of configuration. Since the pin is an open drain driver, it needs a pull-up to ensure the pin goes High. The DONE pin is expected to rise within 1 clock cycle of the Start-Up sequence. The *Spartan-6 Configuration User Guide* (v2.1, page 24) states that "DONE should be pulled-up with a 2.4k pull-up," however, this value is a typo in the document. The official recommendation for the pull-up on a Spartan-6 deviceis the same as for theSpartan-3 family and Virtex-4, Virtex-5, and Virtex-6 devices where a 330 ohm pull-up should be used. This recommendation allows for the DONE pin to rise within 1 clock cycle at a maximum configuration rate of 100 MHz. If a board has been populated with a 2.4k pull-up on the DONE signal, the board should work fine at slower speeds (~2MHz), but you might experience Start-Up sequence issues at increased speeds. The official recommendation is to use the 330 ohm pull-up on the DONE pin, and the 2.4k might enable to device to work just fine.

In short, the DONE pin pull-up recommendation of 330 ohm and INIT pin pull-up recommendation of 4.7k that Xilinx has been using for all recent FPGA families still holds true for Spartan-6 devices and these values should be used.