# **TE0720 CPLD**

#### 1 Overview Overview Feature Summary 1.2 Firmware Revision and supported PCB Revision

A Lattice XO2-1200 CPL D (U19) is used as a System Management Controller. The SC is responsible for power sequencing, lesser generation and zynq initial configuration (mode pin strapping). Moreover, some on-board ICs are connected to the SC that provides level shifting. The SC wakes up when the 3.3V input power rises above 2.1V (VIN voltage is not needed). The SC can turn on or off all of the other supplies on the module (except in 75 Gover sequencing mode when the 1.0V and 1.8 V supplies are forced to start immediately when power is applied to the module).

- - 3.3 Legal Notices

# Feature 34 Data Privacy

- 3.6 Limitation of Liability

- Power Managerright Notice

- Reset Managementagy Licenses

- JTAG Routingironmental Protection

- Boot Mode REACH, RoHS and WEEE

- User IO

- LED

- MDIO Interface

- UNI/O MAC access Watchdog Timer

- I2C

## Firmware Revision and supported PCB Revision

See Document Change History

## **Product Specification**

## **Port Description**

| Name / opt.<br>VHD Name | Direction | Pin | Pullup/Down | Bank Power | Description                                                             |

|-------------------------|-----------|-----|-------------|------------|-------------------------------------------------------------------------|

| BOOT_R /<br>BOOTMODE_R  | out       | N12 | NONE        | 3.3V       | If low then the<br>QSPI flash can<br>not be written.<br>(Write protect) |

| BOOT_R5 /<br>BOOTMODE_R5   | out   | M11 | DOWN | 3.3V | If low then the<br>QSPI flash will<br>be reset. (HOLD<br>/RESET)                                                                                                                                                                    |

|----------------------------|-------|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_125MHz                 | in    | G13 | NONE | 1.8V | 125MHZ Clock<br>Output of<br>Ethernet<br>transceiver chip<br>(88E1512-A0-<br>NNP2C000) that<br>synchronized<br>with the 25MHZ<br>reference clock                                                                                    |

| EN_3V3                     | out   | A2  | DOWN | 3.3V | If high then the<br>3.3V power will<br>be switched ON.                                                                                                                                                                              |

| EN1                        | in    | A9  | UP   | 3.3V | User Enable.<br>Enables the DC-<br>DC converters<br>and on board<br>supplies (Active<br>High). (B2B<br>JM1-28)(DIP<br>Switch on the<br>carrier board).<br>Not used if<br>NOSEQ = '1'                                                |

| ETH-CLK-EN /<br>EN_ETH_CLK | out   | J14 | NONE | 1.8V | ETH clock<br>enable. Enable<br>pin for U9<br>oscillator chip<br>U9 (SiT8008BI-<br>73-18S-<br>25.00000E) to<br>feed a clock to<br>Ethernet<br>Transceiver<br>(U8). Default is<br>mapped to logic<br>high '1'. Enabled<br>as default. |

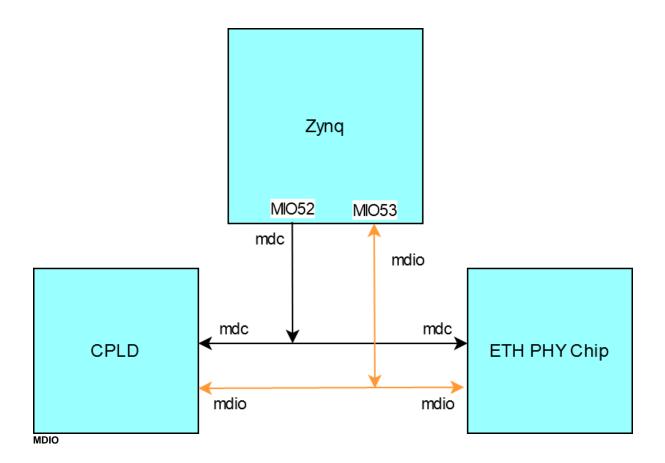

| ETH-MDC / mdc              | in    | L14 | UP   | 1.8V | Management<br>Data Clock<br>reference for the<br>Ethernet<br>transceiver chip.<br>This pin is<br>connected with<br>MIO52 of FPGA<br>too and can be<br>activated in<br>Zynq7<br>adjustment.                                          |

| ETH-MDIO /<br>mdio         | inout | К14 | UP   | 1.8V | It is<br>Management<br>Data pin of<br>Ethernet<br>transceiver chip<br>to transfer in<br>and out of the<br>device<br>synchronously<br>to mdc. It is<br>connected with<br>MIO53 of FPGA.                                              |

| ETH-RST             | out   | E14 | DOWN | 1.8V | ETH PHY<br>RESET. Reset<br>pin of Ethernet<br>transceiver chip.<br>(Active low)<br>Default is<br>mapped to<br>internal reset.                                               |

|---------------------|-------|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT                | in    | C9  | UP   | 3.3V | INIT_B_0 pin of<br>FPGA. (Active<br>low). This pin<br>must be tristate<br>for PL<br>configuratuion.<br>By user or<br>device held low<br>until is ready to<br>be configured. |

| INT1 / INT2         | in    | Ρ4  | UP   | 3.3V | MEMS Interrupt<br>1 of 3D<br>accelerometer<br>and 3D<br>magnetometer<br>chip U22<br>(LSM303DTR)<br>(Active High)                                                            |

| INT2 / INT1         | in    | P6  | UP   | 3.3V | MEMS Interrupt<br>2 of 3D<br>accelerometer<br>and 3D<br>magnetometer<br>chip U22<br>(LSM303DTR)<br>(Active High)                                                            |

| JTAGMODE            | in    | B9  |      | 3.3V | JTAGENB pin of<br>CPLD. Enable<br>JTAG access to<br>CPLD for<br>Firmware<br>update (zero:<br>JTAG routed to<br>module, one:<br>CPLD access)                                 |

| LED1                | out   | P2  | NONE | 3.3V | Display green<br>LED (D2).<br>Default mapped<br>to MIO7                                                                                                                     |

| LED2                | out   | N3  | DOWN | 3.3V | Display red LED<br>(D5). Default<br>mapped to<br>modeblink. In<br>this case LED<br>flashs<br>depending on<br>the boot mode<br>(SD card slow,<br>QSPI fast)                  |

| MEM-MAC /<br>MAC_IO | inout | M14 | UP   | 1.8V | Serial Clock<br>/Data input<br>/Output of Serial<br>EEPROM<br>(11AA02E48T-I<br>/TT) U17                                                                                     |

| MEM-SHA /<br>SHA_IO | inout | N14 | UP   | 1.8V | SDA for<br>CryptoAuthentic<br>ation Chip<br>(ATSHA204A-<br>STUCZ-T) U10                                                                                                     |

| MIO14                  | inout | M4  | NONE | 3.3V | This pin is<br>connected to<br>Zynq PS-MIO<br>(B6) . (RX pin<br>of UART0)                                                                                                                                               |

|------------------------|-------|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIO15                  | inout | N4  | NONE | 3.3V | This pin is<br>connected to<br>Zynq PS-MIO<br>(E6) . (TX pin of<br>UART0)                                                                                                                                               |

| MIO7                   | in    | P11 | UP   | 3.3V | This pin is used as GPIO.                                                                                                                                                                                               |

| MMC_RST                | out   | G14 | DOWN | 1.8V | eMMC reset.<br>Reset pin of<br>eMMC memory<br>(MTFC16GJVEC<br>-2M WT) U15.<br>Default is<br>mapped to<br>internal reset.                                                                                                |

| MODE /<br>BOOTMODE_IN  | in    | C8  | UP   | 3.3V | Latched as<br>BOOTMODE<br>once at power-<br>up, can be used<br>later as I/O,<br>weak pull up.<br>Force low for<br>boot from the<br>SD Card.<br>Latched at<br>power on only,<br>not on soft reset<br>(B2B-JM1 pin<br>32) |

| MODE /<br>BOOTMODE_IN2 | in    | М9  | UP   | 3.3V | Latched as<br>BOOTMODE<br>once at power-<br>up, can be used<br>later as I/O,<br>weak pull up.<br>Force low for<br>boot from the<br>SD Card.<br>Latched at<br>power on only,<br>not on soft reset<br>(B2B-JM1 pin<br>32) |

| MR / POR_B             | out   | P12 | UP   | 3.3V | Power-on-reset<br>pin. This pin is<br>connected with<br>supply voltage<br>monitor chip<br>(TPS3106K33D<br>BVR) U26 and<br>controls the<br>PS_POR_B pin<br>of FPGA.<br>(Active Low)                                      |

| NetU19_B12             |       | B12 |      |      | / currently_not_u<br>sed                                                                                                                                                                                                |

| NetU19_B13             |       | B13 |      |      | / currently_not_u<br>sed                                                                                                                                                                                                |

| NetU19_B2              |       | B2  |      |      | / currently_not_u<br>sed                                                                                                                                                                                                |

| NetU19_B3             |     | B3  |      |      | / currently_not_u<br>sed |

|-----------------------|-----|-----|------|------|--------------------------|

| NetU19_B7             |     | B7  |      |      | / currently_not_u<br>sed |

| NetU19_C1             |     | C1  |      |      | / currently_not_u<br>sed |

| NetU19_C10            |     | C10 |      |      | / currently_not_u<br>sed |

| NetU19_C12 /<br>Dummy | out | C12 | DOWN | 3.3V |                          |

| NetU19_C3             |     | C3  |      |      | / currently_not_u<br>sed |

| NetU19_C6             |     | C6  |      |      | / currently_not_u<br>sed |

| NetU19_C7             |     | C7  |      |      | / currently_not_u<br>sed |

| NetU19_E1             |     | E1  |      |      | / currently_not_u<br>sed |

| NetU19_E12            |     | E12 |      |      | / currently_not_u<br>sed |

| NetU19_F13            |     | F13 |      |      | / currently_not_u<br>sed |

| NetU19_F3             |     | F3  |      |      | / currently_not_u<br>sed |

| NetU19_G3             |     | G3  |      |      | / currently_not_u<br>sed |

| NetU19_H3             |     | H3  |      |      | / currently_not_u<br>sed |

| NetU19_J3             |     | J3  |      |      | / currently_not_u<br>sed |

| NetU19_K13            |     | K13 |      |      | / currently_not_u<br>sed |

| NetU19_K3             |     | K3  |      |      | / currently_not_u<br>sed |

| NetU19_L3             |     | L3  |      |      | / currently_not_u<br>sed |

| NetU19_M12            |     | M12 |      |      | / currently_not_u<br>sed |

| NetU19_M2             |     | M2  |      |      | / currently_not_u<br>sed |

| NetU19_M3             |     | M3  |      |      | / currently_not_u<br>sed |

| NetU19_N13            |     | N13 |      |      | / currently_not_u<br>sed |

| NetU19_N5             |     | N5  |      |      | / currently_not_u<br>sed |

| NetU19_N7             |     | N7  |      |      | / currently_not_u<br>sed |

| NetU19_N8             |     | N8  |      |      | / currently_not_u        |

| NOSEQ   | inout | A3  | DOWN | 3.3V | Usage CPLD<br>Variant<br>depends. (B2B-<br>NOSEQ pin 7)<br>Forces the 1.0V<br>and 1.8V DC-<br>DC converters<br>always ON<br>when high. Can<br>be used as an I<br>/O after boot.<br>Default mapped<br>to PHY_LED0. |

|---------|-------|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON_1V0  | out   | A12 | NONE | 3.3V | Enable pin for<br>1.0 V DC-DC<br>(Active High)                                                                                                                                                                    |

| ON_1V5  | out   | М7  | NONE | 3.3V | Enable pin for<br>1.5 V DC-DC<br>(Active High)                                                                                                                                                                    |

| ON_1V8  | out   | A11 | NONE | 3.3V | Enable pin for<br>1.8 V DC-DC<br>(Active High)                                                                                                                                                                    |

| OTG-RST | out   | B14 | DOWN | 1.8V | USB PHY reset.<br>Reset pin for<br>high speed USB<br>transceiver<br>(USB3320C-<br>EZK) U18<br>(Active Low).<br>Default is<br>mapped to<br>internal reset.                                                         |

| PG_1V0  | in    | A7  | UP   | 3.3V | Power OK<br>(POK) pin of 1.0<br>V DC-DC<br>converter<br>EN6347QI (U1).<br>If High then the<br>output voltage<br>of regulator is<br>within 10% of<br>nominal value<br>(OK).                                        |

| PG_1V5  | in    | N6  | UP   | 3.3V | Power OK<br>(POK) pin of 1.5<br>V DC-DC<br>converter<br>EP53F8QI (U2).<br>If High then the<br>output voltage<br>of regulator is<br>Ok.                                                                            |

| PG_1V8  | in    | A10 | UP   | 3.3V | Power OK<br>(POK) pin of 1.8<br>V DC-DC<br>converter<br>EP53F8QI (U3).<br>If High then the<br>output voltage<br>of regulator is<br>Ok.                                                                            |

| PG_3V3 / POR       | in    | C11 | UP   | 3.3V | POR Reset pin.<br>This pin is<br>connected with<br>PG_3V3. As<br>long as the<br>VCCIO34<br>voltage is zero,<br>this pin will<br>remain low.                                                                    |

|--------------------|-------|-----|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGOOD              | inout | B8  | UP   | 3.3V | Power good<br>output as<br>default, can be<br>used as I/O.<br>(B2B JM1-Pin<br>30) Forced low<br>until all on-<br>board power<br>supplies are<br>working properly.                                              |

| PHY_CONFIG         | inout | C14 | DOWN | 1.8V | ETH PHY<br>CONFIG.<br>Hardware<br>configuration pin<br>of Ethernet<br>transceiver<br>(88E1512-A0-<br>NNP2C000).<br>Default mapped<br>to logic low '0'.<br>Therefore PHY<br>address set to<br>0x00.             |

| PHY_LED0           | inout | F14 | NONE | 1.8V | LED output 0 of<br>Ehternet<br>transceiver chip                                                                                                                                                                |

| PHY_LED1           | inout | D12 | NONE | 1.8V | LED output 1 of<br>Ehternet<br>transceiver chip                                                                                                                                                                |

| PHY_LED2           | inout | C13 | NONE | 1.8V | LED output 2 or<br>interrupt output<br>pin (Active Low)<br>of Ehternet<br>transceiver chip                                                                                                                     |

| PJTAG_R            | out   | N10 | NONE | 3.3V | This pin in the<br>schematic is<br>connected with<br>SPI-DQ0/M0 Pin                                                                                                                                            |

| PROG_B             | in    | A13 | UP   | 3.3V | By pulsing this<br>pin any<br>configuration<br>that is currently<br>loaded is<br>cleared and the<br>PL prepared to<br>load new<br>configuration.<br>(Active Low)<br>Default is<br>mapped to logic<br>high '1'. |

| PS-RST /<br>SRST_B | out   | M13 | UP   | 1.8V | PS software<br>reset (Active<br>Low). Default is<br>mapped to logic<br>high '1'.                                                                                                                               |

| PUDC_B             | inout | E3  | DOWN | VCCIO34 | Selects the<br>enable or<br>disable of pull-<br>ups during<br>configuration on<br>the user I/O<br>pins. (Active<br>Low) Enables<br>internal pull-up<br>resistors on the<br>select I/O pins<br>after power-up<br>and during<br>configuration.<br>Default is<br>mapped to logic<br>low '0'. |

|--------------------|-------|-----|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESIN              | in    | C4  | UP   | 3.3V    | Master reset<br>input (Active<br>Low). Default<br>mapping forces<br>POR_B reset to<br>Zynq PS                                                                                                                                                                                             |

| RST /<br>RST_SENSE | in    | P3  | NONE | 3.3V    | Reset pin that is<br>connected with<br>PS_PORT_B<br>(Power-on-<br>reset) (Active<br>Low)                                                                                                                                                                                                  |

| RTC_INT            | in    | N2  | UP   | 3.3V    | Interrupt output<br>or frequency<br>output of RTC<br>chip<br>(ISL12020MIRZ)<br>U20 (Active Low)                                                                                                                                                                                           |

| SCL                | inout | P8  | UP   | 3.3V    | I2C clock pin of<br>MEMS chip<br>(LSM303DTR)<br>U22                                                                                                                                                                                                                                       |

| SDA                | inout | P7  | UP   | 3.3V    | I2C data pin of<br>MEMS chip<br>(LSM303DTR)<br>U22                                                                                                                                                                                                                                        |

| SPK_L              |       | M5  |      |         | / currently_not_u<br>sed                                                                                                                                                                                                                                                                  |

| SPK_R              |       | M8  |      |         | / currently_not_u<br>sed                                                                                                                                                                                                                                                                  |

| TCK / C_TCK        | out   | P13 | DOWN | 3.3V    | Zynq JTAG<br>clock pin                                                                                                                                                                                                                                                                    |

| TDI / C_TDI        | out   | P9  | DOWN | 3.3V    | Zynq JTAG data<br>input pin                                                                                                                                                                                                                                                               |

| TDO / C_TDO        | in    | M10 | DOWN | 3.3V    | Zynq JTAG data<br>output pin                                                                                                                                                                                                                                                              |

| TMS / C_TMS        | out   | N9  | DOWN | 3.3V    | Zynq JTAG<br>mode select pin                                                                                                                                                                                                                                                              |

| VCCIO34            |       | E2  |      |         | / currently_not_u<br>sed                                                                                                                                                                                                                                                                  |

| VCCIO34            |       | F2  |      |         | / currently_not_u<br>sed                                                                                                                                                                                                                                                                  |

| VCCIO34            |       | H2  |      |         | / currently_not_u<br>sed                                                                                                                                                                                                                                                                  |

| VCCIO34          |       | J2 |      |         | / currently_not_u<br>sed                                                                                                   |

|------------------|-------|----|------|---------|----------------------------------------------------------------------------------------------------------------------------|

| VCCIO34          |       | K2 |      |         | / currently_not_u<br>sed                                                                                                   |

| X_TCK / M_TCK    | in    | B6 | DOWN | 3.3V    | FTDI JTAG<br>clock pin (B2B-<br>JM1-pin 99)                                                                                |

| X_TDI / M_TDI    | in    | B4 | DOWN | 3.3V    | FTDI JTAG data<br>input pin (B2B-<br>JM1-pin 95)                                                                           |

| X_TDO /<br>M_TDO | out   | A4 | DOWN | 3.3V    | FTDI JTAG data<br>output pin (B2B-<br>JM1-pin 97)                                                                          |

| X_TMS /<br>M_TMS | in    | A6 | DOWN | 3.3V    | FTDI JTAG<br>mode select pin<br>(B2B-JM1-pin<br>93)                                                                        |

| X1               | in    | F1 | UP   | VCCIO34 | CPLD pin to the<br>FPGA (L16).<br>I2C clock from<br>FPGA                                                                   |

| X2 / XIO4        | inout | C2 | UP   | VCCIO34 | CPLD pin to the<br>FPGA (M15).<br>Default mapped<br>to PHY_LED0<br>(ETH PHY<br>LED0).                                      |

| X3 / XIO5        | inout | B1 | UP   | VCCIO34 | CPLD pin to the<br>FPGA (N15).<br>Default mapped<br>to PHY_LED1<br>(ETH PHY<br>LED1).                                      |

| X4 / XIO6        | inout | D1 | UP   | VCCIO34 | CPLD pin to the<br>FPGA (P16).<br>Default mapped<br>to PHY_LED2<br>(ETH PHY<br>LED2).                                      |

| X5               | out   | J1 | NONE | VCCIO34 | CPLD pin to the<br>FPGA (P22).<br>I2C data to<br>FPGA                                                                      |

| X6               |       | H1 |      |         | / currently_not_u<br>sed                                                                                                   |

| X7               | in    | M1 | UP   | VCCIO34 | CPLD pin to the<br>FPGA (N22).<br>I2C data from<br>FPGA                                                                    |

| XCLK             | out   | К1 | NONE | VCCIO34 | CPLD pin to the<br>FPGA (K19).<br>Default mapped<br>to<br>CLK_125MHZ.<br>(Clock output of<br>ethernet<br>transceiver chip) |

| - / SIG1           | in  | E13 | NONE | 1.8V | This pin is<br>connected with<br>VCCIO34<br>directly in the<br>schematic<br>REV03 and has<br>no lable in the<br>schematic.                                                                                                                                                      |

|--------------------|-----|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDEN / WDEN        | out | C6  | NONE | 3.3V | Enable pin for<br>WDT chip<br>BD39040MUF-<br>CE2.<br>High=Active,<br>Low=Disable<br>and WDT error<br>is ignored.                                                                                                                                                                |

| WDIN / WDIN        | out | N8  | NONE | 3.3V | Clock input pin<br>for WDT chip<br>BD39040MUF-<br>CE2                                                                                                                                                                                                                           |

| WDOUT /<br>WDOUT   | in  | МЗ  | DOWN | 3.3V | Buffer output pin<br>for the WDEN<br>pin of WDT chip<br>BD39040MUF-<br>CE2 input.<br>Abnormal<br>Power Source /<br>the GND pin<br>shortage for the<br>WDEN pin can<br>be recognized<br>by monitoring<br>this pin. This pin<br>becomes Low<br>when the<br>XRSTOUT pin<br>is low. |

| PG_ALL /<br>PG_ALL | in  | C12 | UP   | 3.3V | POWER GOOD<br>outputs and<br>Reset Pin of<br>WDT Chip<br>BD39040MUF-<br>CE2<br>(XRSTOUT)                                                                                                                                                                                        |

| X6 / X6            | in  | H1  | NONE | 1.8V | CPLD pin (H1)<br>connected to<br>the FPGA<br>(K20). Input<br>clock for<br>hardware WDT<br>that forwarded<br>to WDIN pin of<br>WDT chip.                                                                                                                                         |

## **Functional Description**

To access and control the following functions it must be accessed CR registers. For more information about how to access these registers refer to CR registers access methods

## **JTAG**

JTAG signals routed directly through the CPLD to FPGA. Access between CPLD and FPGA can be multiplexed via JTAGENB pin of CPLD (B9) (logical one for CPLD, logical zero for FPGA). This pin is connected to B2B (JM1-pin 89) directly. On the carrier board can be this pin enabled or disabled with a dip switch.

| CPLD JTAGENB (B2B JM1-89) | Description |

|---------------------------|-------------|

| 0                         | FPGA access |

| 1                         | CPLD access |

### **Boot Mode**

Boot mode can be set either by hardware (dip-switch) on the carrier board or by Linux console. Even after booting you can change the boot mode. After changing the boot mode FPGA is restarted automatically by CPLD. To change boot mode a state machine continuously monitors the corresponding register (CR4[15:8]) that can be change via MDIO interface between CPLD and FPGA. After changing CR4[15:8] according to desired boot mode, CPLD will reset FPGA.

In the following table the corresponding commands are shown:

| Change Method | Boot Mode | CPLD PGOOD<br>Pin (B2B Pin<br>JM1-30) | CPLD MODE<br>Pin (B2B Pin<br>JM1-32) | Description |

|---------------|-----------|---------------------------------------|--------------------------------------|-------------|

| Hardware      | JTAG      | 0                                     | 0                                    |             |

| Hardware      |           | 0                                     | 1                                    |             |

| Hardware      | SD Card   | 1                                     | 0                                    |             |

| Hardware      | QSPI      | 1                                     | 1                                    |             |

| Change Method | Boot Mode | Command in<br>Linux console             | Command in<br>FSBL                                  | Description |

|---------------|-----------|-----------------------------------------|-----------------------------------------------------|-------------|

| Software      | JTAG      | phytool write<br>eth0/0x1A/12<br>0x9100 | XEmacPs_PhyWrit<br>e(&Emac,<br>0x1A, 12,<br>0x9100) |             |

| Software      | SD Card   | phytool write<br>eth0/0x1A/12<br>0x9300 | XEmacPs_PhyWrit<br>e(&Emac,<br>0x1A, 12,<br>0x9300) |             |

| Software      | QSPI      | phytool write<br>eth0/0x1A/12<br>0x9200 | XEmacPs_PhyWrit<br>e(&Emac,<br>0x1A, 12,<br>0x9200) |             |

### Watchdog Timer

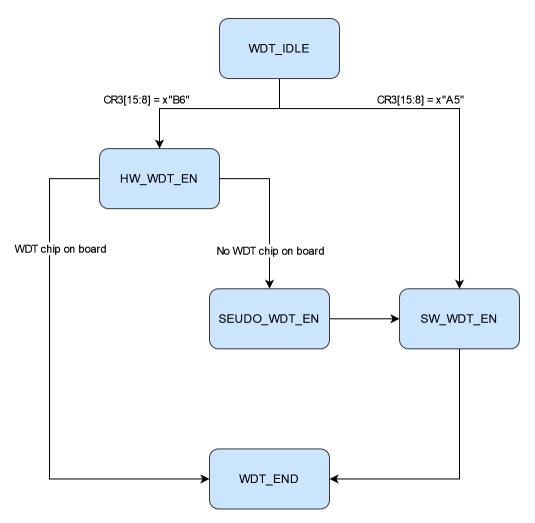

As of PCB revision 04 there is a watchdog timer chip (BD39040MUF-CE2) on the module. A state machine monitors register CR3[15:8]. If the value of the register is 0xA5, WDT is activated. First state machine assumes that WDT chip is assembled on the board, therefore it tries to activate hardware WDT at the beginning. If there is no WDT chip on the board, for example the module PCB is revision REV03 or older, software WDT will be activated. In the following is shown WDT state machine diagram:

#### Hardware WDT

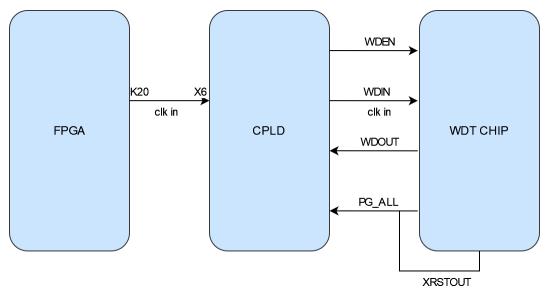

New PCB revision of TE0720 (Rev04) consists of watchdog timer chip (BD39040MUF-CE2). There are four pins between this chip and CPLD.

| CPLD   | Direction | WDT Chip         | Description                     |

|--------|-----------|------------------|---------------------------------|

| WDEN   | OUT       | WDEN             | WDT enable pin                  |

| WDIN   | OUT       | WDIN             | WDT clock pin                   |

| WDOUT  | IN        | WDOUT            | Fed back WDT enable pin to CPLD |

| PG_ALL | IN        | PG_ALL + XRSTOUT | Power-GOOD and Reset pins       |

Watchdog Timer (WDT) monitors FPGA's operation by detecting the time from both rise and fall edge of WDIN. BIST is a self-test of chip to see if comparators of the WDT chip work correctly. If BIST result is abnormality, WDT does not work and XRSTOUT is kept low.Once BIST ends without any errors, XRSTOUT becomes High. WDT is activated when WDOUT=High, and both WDEN and XRSTOUT have to be High in order to get WDOUT to be High. As long as the duty of WDIN clock is kept within "Trigger open window", WDT does not detect any errors and XRSTOUT stays at High. WDIN input signal is ignored when WDOUT=Low. WDT is activated when WDOUT=High, and both WDEN and XRSTOUT have to be High in order to get WDOUT to be High.

Input clock of hardware WDT is generated in FPGA (pin K20) and forwarded by X6 ( CPLD pin) to WDIN pin of WDT chip. The hardware WDT will be activated , if WDT chip exists on the board and the following command in linux console be executed:

#### "phytool write eth0/0x1A/7 0xB600"

If WDT chip does not exist on the board by executing this command software WDT will be activated automatically. In this case input clock of WDT will be K20 pin of FPGA that connected to X6 pin of CPLD. The following table shows all cases for WDT:

| WDT Chip<br>on Board? | Command<br>in linux<br>console         | Command in<br>FSBL                                 | WDT Type     | Input Clock                            | Description                                                                |

|-----------------------|----------------------------------------|----------------------------------------------------|--------------|----------------------------------------|----------------------------------------------------------------------------|

| NO                    | phytool write<br>eth0/0x1A/7<br>0xA500 | XEmacPs_PhyW<br>rite(&Emac,<br>0x1A, 7,<br>0xA500) | Software WDT | CR1(14)                                |                                                                            |

| NO                    | phytool write<br>eth0/0x1A/7<br>0xB600 | XEmacPs_PhyW<br>rite(&Emac,<br>0x1A, 7,<br>0xB600) | Software WDT | K20 pin of<br>FPGA (X6 pin<br>of CPLD) | Clock frequency<br>must be less<br>than 31.9 HZ<br>with 50% duty<br>cycle. |

| YES                   | phytool write<br>eth0/0x1A/7<br>0xA500 | XEmacPs_PhyW<br>rite(&Emac,<br>0x1A, 7,<br>0xA500) | Software WDT | CR1(14)                                |                                                                            |

| YES                   | phytool write<br>eth0/0x1A/7<br>0xB600 | XEmacPs_PhyW<br>rite(&Emac,<br>0x1A, 7,<br>0xB600) | Hardware WDT | K20 pin of<br>FPGA (X6 pin<br>of CPLD) | Clock frequency<br>must be less<br>than 31.9 HZ<br>with 50% duty<br>cycle. |

#### Software WDT

Software WDT can be activated by executing the following instruction in linux console:

"phytool write eth0/0x1A/7 0xA500"

CR[14] bit is same as a clock input pin for software WDT. If this bit after enabling software WDT will not be toggled correctly, FPGA will be reseted.

If the software WDT is activated and the generated clock is fed to WDT input clock, it will not be reset the board (WDT\_RST signal low). But if the generation of this clock is stopped, the board will be reset (WDT\_RST signal high) after a period of time depending on the WDT\_time (CR4[7:0] register value).

To test Watchdog timer can be fed a clock signal to WDT clock input. The following shell script file generates a clock for WDT input clock. This file must be copied as init.sh to the SD card additionally. This shell script file will be executed by booting the board and generates the WDT input clock automatically. As long as 1 key and enter key is not pressed, the WDT clock will be generated and subsequently the board will not be reset. But if generation of clock signal be stopped, the board will be reset after a period of time. Note that WDT must already be activated in FSBL code.

#### init.sh

```

#WDT test

#!/bin/sh

echo "Starting the WDT Clock"

sleep 1

while :

do

phytool read eth0/0x1A/5

phytool write eth0/0x1A/5 0x4041

sleep 0.5

phytool read eth0/0x1A/5

phytool write eth0/0x1A/5 0x0041

sleep 0.5

read -r -t 0.1 b

echo "Press 1 to exit!"

if (( b == 1 )) ; then

break

fi

done

printf "\Quit.....\n\n"

```

#### WDT adjustment

Watchdog timer is an added option in the CPLD code. To control and to use watchdog timer correctly, it must be written correct values in the related CR registers.

| Software WDT<br>signal / register | Related CPLD<br>Register     | Access in FSBL code                   | Access in Linux | Description                                                                             |

|-----------------------------------|------------------------------|---------------------------------------|-----------------|-----------------------------------------------------------------------------------------|

| WDT input clock                   | CR1(14)<br>CR1 = Register5   | XEmacPs_PhyWrite<br>/ XEmacPs_Phyread | Phytool command |                                                                                         |

| WDT_time                          | CR4[7:0]<br>CR4 = Register12 | XEmacPs_PhyWrite<br>/ XEmacPs_Phyread | Phytool command | If CR4[7:0] = 0x00<br>WDT_time = 0x07<br>If CR4[7:0] /= 0x00<br>WDT_time = CR4[7:<br>0] |

| WDT_Enable | CR3[15:8]       | XEmacPs_PhyWrite<br>/ XEmacPs_Phyread | Phytool command | If CR3[15:8] = 0xA5<br>WDT enable   |

|------------|-----------------|---------------------------------------|-----------------|-------------------------------------|

|            | CR3 = Register7 |                                       |                 | If CR3[15:8] /= 0xA5<br>WDT disable |

For example to access these registers in FSBL code it can be used the following instruction:

- Status = XEmacPs\_PhyWrite(&Emac, 0x1A, 7, 0xA500); if(Status != XST\_SUCCESS){ return XST\_FAILURE; } To enable software WDT

- Status = XEmacPs\_PhyWrite(&Emac, 0x1A, 7, 0xB600); if(Status != XST\_SUCCESS){ return XST\_FAILURE; } To enable hardware WDT

- Status = XEmacPs\_PhyWrite(&Emac, 0x1A, 7, 0x0000); if(Status != XST\_SUCCESS){ return XST\_FAILURE; } To disable hardware /software WDT WDT

- Status = XEmacPs\_PhyWrite(&Emac, 0x1A, 12, 0x001F); if(Status != XST\_SUCCESS){ return XST\_FAILURE; } To adjust desired time for WDT

Another way to access the related registers for WDT is to use phytool command. It must be added the ethtool package in Linux. To add this package it must be chosen in petalinux configuration for rootfs this option. The path in petalinux rootfs is: **Filesystem package/console/network/ethtool**

The phytool instruntion format is :

- Phytool read device/addr/register

- Phytool write device/addr/register <value>

To write desired value in the related WDT registers for example can be written the following instructions in Linux console:

- phytool write eth0/0x1A/7 0xA500 Software WDT enable

- phytool write eth0/0x1A/7 0xB600 Hardware WDT enable

- phytool write eth0/0x1A/7 0x0000 Software/ Hardware WDT disable

- phytool write eth0/0x1A/12 0x001F Adjusted software WDT time. It depends on the period of the CPLD clock.

- phytool write eth0/0x1A/5 0x4000 To set the WDT input clock of software WDT high

- phytool write eth0/0x1A/5 0x0000 To set the WDT input clock of software WDT low

### Reset

Zynq will be reset, when it occures one of the following conditions:

| Reset name  | Reset reasone                                                                                                           | related reset pin /<br>signal | Active |

|-------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------|

| Reset       | Reset push button                                                                                                       | RESIN                         | LOW    |

| Extra Reset | Reset command in software                                                                                               | CR1(15)                       | HIGH   |

| WDT reset   | Overflowing the WDT<br>counter and no existance<br>WDT input clock (For<br>more information refer to<br>Watchdog Timer) | WD_RST                        | HIGH   |

Extra Reset

The board can also be reset through software.

| Extra reset     | related register             | Access in FSBL code                   | Access in Linux | Description                                                                              |

|-----------------|------------------------------|---------------------------------------|-----------------|------------------------------------------------------------------------------------------|

| Enable register | CR3[15:8]<br>CR3 = Register7 | XEmacPs_PhyWrite<br>/ XEmacPs_Phyread | Phytool command | If CR3[15:8] = 0xE5<br>Extra reset enable<br>If CR3[15:8] /= 0xE5<br>Extra reset disable |

| Reset bit       | CR1(15)                      |                                       | Phytool command | If CR1(15) = '1'<br>Reset the board                                                      |

For example the following instructions can reset the board:

- phytool write eth0/0x1A/7 0xE500 Extra reset enable

- phytool write eth0/0x1A/5 0x8000 Reset the board

It can be activated this option in FSBL code too:

Status = XEmacPs\_PhyWrite(&Emac, 0x1A, 7, 0xE500); if(Status != XST\_SUCCESS) { return XST\_FAILURE; }

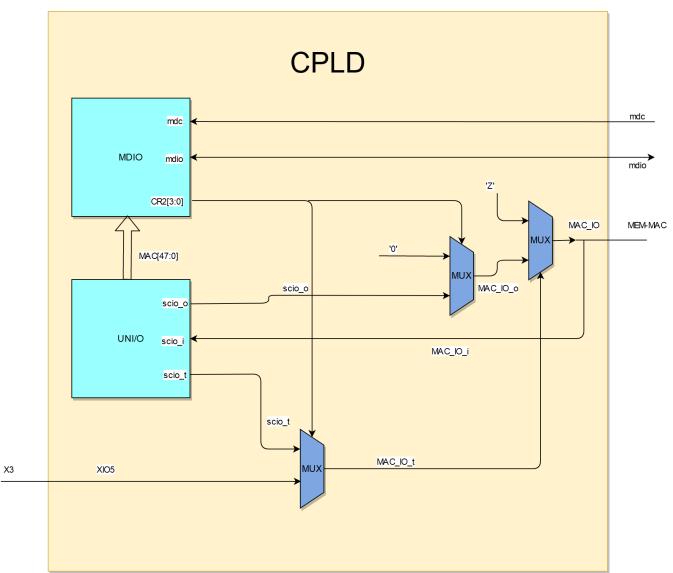

### Serial EEPROM

The seial EEPROM (U17) is used to save MAC addess. The MAC\_IO pin of EEPROM uses UNI/O interface to communicate with CPLD. The connection between EEPROM chip and CPLD depends on the value of XIO4.

| XIO4[3:0] | MAC_IO                               |

|-----------|--------------------------------------|

| 0011      | '0'                                  |

| else      | Connected to internal MAC read block |

### CryptoAuthentication

The CryptoAuthentication chip (U10) is a high-security hardware authentication device that allows use in many application same as checking user password. This device can communicate with 1MHZ I2C interface, single-wire interface or UART.

| XIO4[3:0] | Value XIO5 | SHA_IO |

|-----------|------------|--------|

| 0010      | '0'        | '0'    |

| else      |            | 'Z'    |

### UART

| CR2[7:4]  | MIO14 (RX) | Description                                                   |

|-----------|------------|---------------------------------------------------------------|

| 1001      | XIO5_in    | XIO5_in is equal to XIO5 if<br>VCCIO34 voltage equal to 1.8V. |

| else      | 'Z'        |                                                               |

| CR2[11:8] | MIO15 (TX) | Description                                                   |

| 1001      | XIO6 in    | XIO6_in is equal to XIO6 if                                   |

|--|

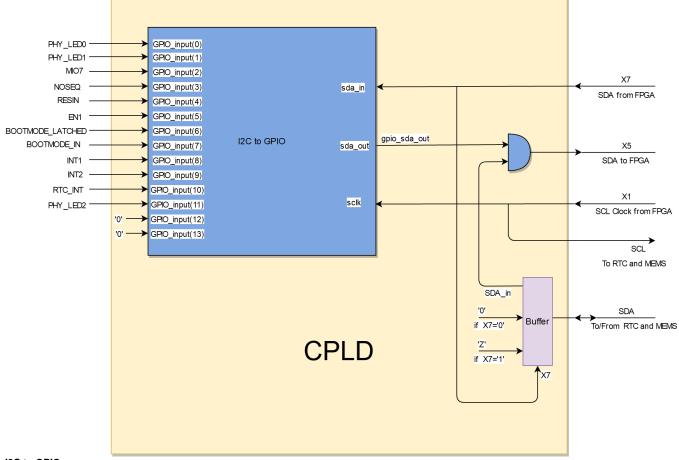

### **I2C to GPIO block**

This subsystem provides 32-bit (4 x 8-bit) of general purpose parallel input and output (I/O) expansion for the I2C bus protocol. Address of this module is 0x20. This module contains four 8-bit registers for reading (GPIO\_input[7:0] to GPIO\_put[31:24]) and four registers for writing (GPIO\_output[7:0] to GPIO\_output[31:24]) separately with 0x00 to 0x03 address. These registers can be accessed with I2C commands in linux console or with i2c functions in FSBL code. To access these registers the following commands in linux console can be used:

- To see the i2c bus addresses : i2cdetect -y -r 1

- To read register of i2c to GPIO module: i2cget -y 1 0x20 <register address>

- To write data in a register of i2c to GPIO module: i2cset -y 1 0x20 <register address> <data>

I2C to GPIO

The MIO7 pin is connected to third bit of GPIO input of the I2C to GPIO subsystem (GPIO\_input(2)) .To test the I2C to GPIO the MIO7 state can be changed and the value of the first register (register address 0x00) can be monitored. The initial value of this register depends on the CPLD firmware and can be variable. In the following example the initial value of this register is equal to 0x39. That means that initial value of MIO7 is zero. Now set MIO7 to one and read the value of the first register with address 0x00 again. It should be equal to 0x3D. LED1 (Green LED) glows, if MIO7 is set high:

- To read the first register of the subsystem:

- <sup>o</sup> i2cget -y 1 0x20 0x00 For example here is equal to 0x39. Here 0x20 is device address and 0x00 is register address.

- To set MIO7 to one:

- ° cd /sys/class/gpio/

- ° echo 913 > export

- o echo out > gpio913/direction

- o echo 1 > gpio913/value

- To read the first register of the subsystem again:

o i2cget -y 1 0x20 0x00

equal to 0x3D.

It should be

| root@petalinux:~# i2cdetect -y -r 1                          |

|--------------------------------------------------------------|

| 0 1 2 3 4 5 6 7 8 9 a b c d e f                              |

| 00:                                                          |

| 10:                                                          |

| 20: 20                                                       |

| 30:                                                          |

| 40:                                                          |

| 50: 57                                                       |

| 60: UU                                                       |

| 70:                                                          |

| root@petalinux:~# i2cget -y 1 0x20 0x00                      |

| 0x39                                                         |

| root@petalinux:~# cd /sys/class/gpio/                        |

| root@petalinux:/sys/class/gpio# echo 913 > export            |

| root@petalinux:/sys/class/gpio# echo out > gpio913/direction |

| root@petalinux:/sys/class/gpio# echo 1 > gpio913/value       |

| root@petalinux:/sys/class/gpio# i2cget -y 1 0x20 0x00        |

| 0x3d                                                         |

| root@petalinux:/sys/class/gpio#                              |

| Evemple                                                      |

| Example                                                      |

The subsystem I2C to GPIO port mapping is according the following table:

| I2C to GPIO | Pin name | CPLD Pin | Direction               | FPGA Pin | Description                                                                                        |

|-------------|----------|----------|-------------------------|----------|----------------------------------------------------------------------------------------------------|

| sda_in      | X7       | M1       | from FPGA               | N22      |                                                                                                    |

| sda_out     | X5       | J1       | to FPGA                 | P22      | If X7 is Low,<br>this pin will be<br>disconnected.                                                 |

| sclk        | X1       | F1       | from FPGA               | L16      |                                                                                                    |

| SDA         | SDA      | Ρ7       | To/From RTC<br>and MEMS |          | I2C data pin of<br>ISL12020MRZ<br>RTC chip / I2C<br>data pin of<br>MEMS chip<br>(LSM303DTR)<br>U22 |

| SCL         | SCL                                                     | P8 | To RTC and<br>MEMS |  | I2C clock pin of<br>ISL12020MRZ<br>RTC chip / I2C<br>clock pin of<br>MEMS chip<br>(LSM303DTR)<br>U22 |  |  |

|-------------|---------------------------------------------------------|----|--------------------|--|------------------------------------------------------------------------------------------------------|--|--|

| GPIO_input  | Mapping the GPIO_input bits to various ports or signals |    |                    |  |                                                                                                      |  |  |

| GPIO_output | Not used                                                |    |                    |  |                                                                                                      |  |  |

GPIO input bit mapping:

| GPIO_input bit | Connected to:    |

|----------------|------------------|

| 0              | PHY_LED0         |

| 1              | PHY_LED1         |

| 2              | MIO7             |

| 3              | NOSEQ            |

| 4              | RESIN_g          |

| 5              | EN1_g            |

| 6              | BOOTMODE_LATCHED |

| 7              | BOOTMODE_IN      |

| 8              | INT1             |

| 9              | INT2             |

| 10             | RTC_INT          |

| 11             | PHY_LED2         |

| 12             | '0'              |

| 13             | '0'              |

### **UNI/O MAC read block**

UNI/O bus is a low speed serial interface for embedded systems that requires only one logic signal SCIO (Serial Clock, Data Input/Output). By using Manchester encoding techniques, the clock and data are combined into a single, serial bit stream (SCIO),where the clock signal is extracted by the receiver to corr ectly decode the timing and value of each bit. The serial EEPROM (U17) interface is UNI/O. The UNI/O bus uses a master/slave configuration. In this system the serial EEPROM chip is slave and a UNI/O subsystem in CPLD works as master. Both master and slave can operate as transmitter or receiver, but th e master device determines which mode is active. The UNI/O MAC read block in CPLD reads the MAC address from serial EEPROM chip during power-on.

#### UNI/O

| uio_sm_cnt[8:5] | uio_io_data |

|-----------------|-------------|

| 0000            | MIO7        |

| 0001            | RTC_INT     |

| 0010            | INT1        |

| 0100            | INT2        |

| 0011            | PHY_LED0    |

| 0100            | PHY_LED1    |

| 0101            | PHY_LED2    |

| 0110            | BOOTMODE_IN |

| 0111 | MIO14  |

|------|--------|

| 1000 | MIO15  |

| 1001 | XIO4   |

| 1010 | XIO5   |

| 1011 | XIO6   |

| 1100 | WD_HIT |

| 1101 | '0'    |

| 1110 | '0'    |

Multiplexing uio data output between uio-id and uio-io:

| uio_sm_cnt[2:1] | uio_sm_cnt(4) | uio_unidir  |

|-----------------|---------------|-------------|

| 01              | -             | '0'         |

| 10              | '0'           | uio_id_data |

| 10              | '1'           | uio_io_data |

## SC Pins to B2B

| Name  | B2B        | Mode                      | Default<br>function            | Alternative | Description                                                                                                                                                    |

|-------|------------|---------------------------|--------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN1   | JM1-Pin 28 | input, weak pull-<br>up   | Power Enable                   | Ю           | High enables<br>the DC-DC<br>converters and<br>on-board<br>supplies. Not<br>used if<br>NOSEQ=1                                                                 |

| MODE  | JM1-Pin 32 | input, weak pull-<br>up   | Boot mode                      | SDA or IO   | Force low for<br>boot from the<br>SD Card.<br>Latched at<br>power on only,<br>not on soft reset!                                                               |

| NOSEQ | JM1-Pin 7  | input, weak pull-<br>down | Power<br>sequencing<br>Control | Output      | Forces the 1.0V<br>and 1.8V DC-<br>DC converters<br>always ON<br>when high. Can<br>be used as an I<br>/O after boot.                                           |

| PGOOD | JM1-Pin 30 | output, open<br>drain     | Power good                     | SCL or IO   | Forced low until<br>all on-board<br>power supplies<br>are working<br>properly.<br>Attention:<br>During CPLD<br>programming,<br>this pins is high<br>impedance. |

| RESIN | JM2-Pin 18 | input, weak pull-<br>up | Reset input | Ю | Active Low<br>Reset input,<br>default mapping<br>forces POR_B<br>reset to Zynq PS |

|-------|------------|-------------------------|-------------|---|-----------------------------------------------------------------------------------|

|-------|------------|-------------------------|-------------|---|-----------------------------------------------------------------------------------|

### **SC Pins to FPGA**

| Schematic ne | et n <b>/airfi@</b> L<br>Name | Default<br>function                                     | Direction | SC pin | FPGA pin | Description                                          |

|--------------|-------------------------------|---------------------------------------------------------|-----------|--------|----------|------------------------------------------------------|

| XCLK         | XCLK                          | ETH PHY<br>Clock to<br>FPGA                             | to FPGA   | К1     | K19      |                                                      |

| Х7           | Х7                            | I2C Data<br>from FPGA                                   | from FPGA | M1     | N22      | SDA from<br>EMIO I2Cx                                |

| X5           | X5                            | I2C Data to<br>FPGA                                     | to FPGA   | J1     | P22      | SDA to EMIO<br>I2Cx                                  |

| X4           | XIO6                          | ETH PHY<br>LED2<br>(PHY_LED2)                           | to FPGA   | D1     | P16      |                                                      |

| Х3           | XIO5                          | ETH PHY<br>LED1<br>(PHY_LED1)                           | to FPGA   | B1     | N15      | RTC, MEMS<br>Interrupt or<br>PHY LED1                |

| X2           | XIO4                          | ETH PHY<br>LED0<br>(PHY_LED0)                           | to FPGA   | C2     | M15      |                                                      |

| X1           | X1                            | I2C Clock<br>from FPGA                                  | from FPGA | F1     | L16      | SCL from<br>EMIO I2Cx                                |

| PUDC_B       | PUDC_B                        | Enables<br>internal pull-<br>up resistors<br>on the IOs | to FPGA   | E3     | K16      | normally not<br>used tied to<br>fixed level by<br>SC |

| Пур.045<br>Пр.9115<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215<br>П.9215 | 500720.0<br> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| PL ph/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

#### NOSEQ Pin

This is a dedicated input that forces the module's 1.0V and 1.8V supplies to be enabled if high. This pin has a weak pull-down on the module. If left open the module will power up in normal power sequencing enabled mode. This pin is 3.3V tolerant. This pin is also connected to the System Management Controller. The SC can read the status of this pin (it can be detected if the module is in power sequencing enabled mode). The SC can also use this pin as output after normal power on sequence.

#### No Sequencing mode

If the module is powered from a single 3.3V supply and power sequencing is disabled, then NOSEQ pin should be powered from the main 3.3V input. That is VIN, 3.3Vin and NOSEQ should all be tied together to the input 3.3V power rail. Sequencing mode should not be used if VIN is not 3.3V.

#### Normal mode

For normal operation leave NOSEQ open or pull down with a resistor.

Normal mode with user function on NOSEQ

NOSEQ can be used as an output after boot. NOSEQ must be low when 3.3V power is applied to the module. Common usage is an LED connected between NOSEQ and GND. The mapping of NOSEQ pin can be changed by CR1 register. The CR1 register is control register of MDIO slave interface that its content can be changed with FSBL code, uboot command or in linux console directly.

### **SC MDIO Interface**

Most registers and functions are available via ETH PHY Management interface (MIO pins 52 and 53).

Address

| Addr  | R/W | Register name       | Description                                                                                                                                                                                                                                                                         |

|-------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | RO  |                     |                                                                                                                                                                                                                                                                                     |

| 1     | RO  |                     |                                                                                                                                                                                                                                                                                     |

| 2     | RO  | ID1                 | PHY Identifier Register 1                                                                                                                                                                                                                                                           |

| 3     | RO  | ID2                 | PHY Identifier Register 2                                                                                                                                                                                                                                                           |

| 4     | RW  | (register4)         | register4 = CR5[15:14] &<br>BOOTMODE_GEN &<br>PUDC & CR5[10:8] &<br>CPLD_REVISION<br>BOOTMODE_GEN,<br>PUDC and<br>CPLD_REVISION are<br>generic parameters.<br>CR5[9:8] = boot mode<br>CR5[10] = CPLD boot<br>mode flag (if active '1'<br>boot mode adjustment via<br>linux console) |

|       |     |                     | CR5[15:14] = WDT status                                                                                                                                                                                                                                                             |

| 5     | RW  | CR1 (register5)     | Control Register 1: LED's                                                                                                                                                                                                                                                           |

| 6     | RW  | CR2 (register6)     | Control Register 2; XIO<br>Control                                                                                                                                                                                                                                                  |

| 7     | RW  | CR3 (register7)     | Control Register 3; Reset,<br>Interrupt                                                                                                                                                                                                                                             |

| 8     | RO  | SR1 (register8)     | Status Register                                                                                                                                                                                                                                                                     |

| 9     | RO  | MAChi (register9)   | Highest bytes of primary MAC Address                                                                                                                                                                                                                                                |

| 0xA   | RO  | MACmi (register10)  | Middle bytes of primary MAC Address                                                                                                                                                                                                                                                 |

| 0xB   | RO  | MAClo (register11)  | Lowest bytes of primary MAC Address                                                                                                                                                                                                                                                 |

| 0xC   | RO  | CR4 (register12)    | reserved do not use                                                                                                                                                                                                                                                                 |

| 0xD   | RW  | MMD_CR (register13) | MMD Control Register                                                                                                                                                                                                                                                                |

| 0xE   | RW  | MMD_AD (register14) | MMD Address/Data                                                                                                                                                                                                                                                                    |

| 0xF   | -   | (register15)        | reserved do no use                                                                                                                                                                                                                                                                  |

| other | -   |                     | reserved do not use                                                                                                                                                                                                                                                                 |

### Register Overview

To adjust desired boot mode in linux console or in FSBL code are used registers CR3(register7), CR4 (register12) , CR5 and register4. These registers are used for communication between user, CPLD and FPGA. The format of these registers is shown in the following tables:

| Register           | Bit 158                                                                                                                                                        | Bit 70                                                                               | Description                                                                                                                                                  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR3<br>(register7) | Software WDT and<br>Hardware WDT activation<br>/External reset enable<br>0xA5 Software WDT<br>active<br>0xB6 Hardware WDT<br>active<br>0xE5 Extra reset enable | connected to some signals<br>/ports that is shown in the<br>related following table. | CR3 register is register7<br>in mdio slave interface.<br>CR3 can be written<br>by user:<br>phytool write eth0<br>/0x1A/7 <desired<br>valude&gt;</desired<br> |

| Register            | Bit 1512                                                        | Bit 1110 | Bit 98                                                                  | Bit 70                     | Description                                                                                                                                                                                                                                                              |

|---------------------|-----------------------------------------------------------------|----------|-------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR4<br>(register12) | Control bits for<br>boot modes<br>1001 Soft boot<br>mode active | Reserved | boot mode<br>00 Undefined<br>01 JTAG Mode<br>10 QSPI Mode<br>11 SD Card | Software WDT<br>time value | CR4[9:8] bits<br>are written by<br>user to define<br>desired boot<br>mode in linux<br>console or in<br>FSBL code.<br>CR4[15:12] bits<br>is used by user<br>to reset FPGA<br>after defining<br>boot mode.<br>CR4 register is<br>register12 in<br>mdio slave<br>interface. |

|                     |                                                                 |          |                                                                         |                            | CR4 can be<br>written by<br>user. For<br>example:<br>phytool<br>write eth0<br>/0x1A/12<br>0x9300 To<br>change boot<br>mode in<br>linux<br>console                                                                                                                        |

| Register  | Bit 1514                                                                                                                                                                              | Bit 1312                                                                                                                                   | Bit 11                                                   | Bit 10                                                                                                                  | Bit 98                                                                        | Bit 70                                 | Description                                          |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------|

| register4 | Watchdog<br>timer status<br>00 WDT<br>deactivated<br>01 Hardware<br>WDT active<br>10 Software<br>WDT active<br>11 No WDT<br>chip on the<br>board,<br>software<br>WDT with PL<br>clock | Boot mode<br>generic<br>parameter<br>00 QSPI/SD<br>Card<br>01 QSPI<br>/JTAG<br>10 default<br>(QSPI/JTAG<br>/SD Card)<br>11 JTAG/SD<br>Card | PUDC<br>generic<br>parameter<br>0 Pull-up<br>1 Pull-down | Software<br>boot mode<br>adjustment<br>active<br>0 CPLD boot<br>mode<br>deactivated<br>1 CPLD boot<br>mode<br>activated | Boot mode<br>00 Undefined<br>01 JTAG<br>mode<br>10 QSPI<br>mode<br>11 SD Card | CPLD_REVIS<br>ION generic<br>parameter | User does<br>not have<br>access to this<br>register. |